一、概述

SPI:Serial Peripheral Interface,串行外围设备接口。

是由摩托罗拉在20世纪80年代中期开发的同步串行总线接口规范(带有时钟信号,通过时钟极性

和时钟相位来控制采样,

即同步传输)。

1、支持半双工、全双工通信模式。

2、没有流控制和应答机制来确认是否接收到数据(UART有校验或流控制)。

3、没有一个固定的传输速率规定,已有器件SPI输出速率达到50Mbps以上(I2C有明确规定速

率)。

4、只能板内的短距离传输(RS232、RS485输出距离远)。

5、没有限制传输bit数量,常用的是8bit或9bit。

6、不需要硬件地址(I2C要地址),采用片选。

7、主从模式,一托多。

二、3线和4线模式

3线SPI和4线SPI各个模式下信号定义:

3线9bit I型 接口信号:SCL、CS、SDA

3线9bit II型接口信号:SCL、CS、SDO、SDI

4线8bit I型接口信号:SCL、CS、DCX、SDA

4线8bit II型接口信号:SCL、CS、DCX、SDO、SDI

3线9bit 2 data Lane 接口信号:SCL、CS、D0、D1

对于3线或4线来区分,并不是信号线的数量,也不是网上说的半双工和全双工,或者数据线数量差异。

个人认为:

3线说的是时钟、片选、数据信号(不管是一根数据线,还是两根数据线),共三种信号。

4线说的是时钟、片选、数据信号、数据或命令控制线(确定发送的是数据还是命令),共4中信号。

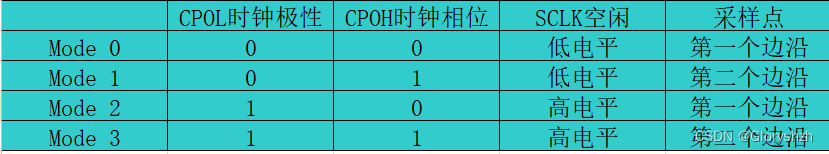

三、SPI 四种工作模式

通过CPOL时钟极性和CPHA时钟相位的搭配来得到四种工作模式:

CPOL时钟极性定义的是 SCLK时钟线空闲状态时的电平

CPOL时钟极性定义的是 SCLK时钟线空闲状态时的电平

CPOL=0,即SCLK=0,表示SCLK时钟信号线在空闲状态时的电平为低电平,因此有效状态为高电平。

CPOL=1,即SCLK=1,表示SCLK时钟信号线在空闲状态时的电平为高电平,因此有效状态为低电平。

CPHA时钟相位定义的是数据位相对于时钟线的时序(即相位)

CPHA=0,即表示输出(out)端在上一个时钟周期的后沿改变数据,而输入(in)端在时钟周期的

前沿(或不久之后)捕

获数据。输出端保持数据有效直到当前时钟周期的尾部边缘。对于第一个时钟周期来说,第一位的

数据必须在时钟前沿之

前出现在MOSI线上。也就是一个CPHA=0的周期包括半个时钟空闲和半个时钟置位的周期。

CPHA=1,即表示输出(out)端在当前时钟周期的前沿改变数据,而输入(in)端在时钟周期的后

沿(或不久之后)捕获

数据。输出端保持数据有效直到下一个时钟周期的前沿。对于最后一个时钟周期来说,从机设备在

片选信号消失之前保持

MISO信号线有效。也就是一个CHPA=1的周期包括半个时钟置位和半个时钟空闲的周期。

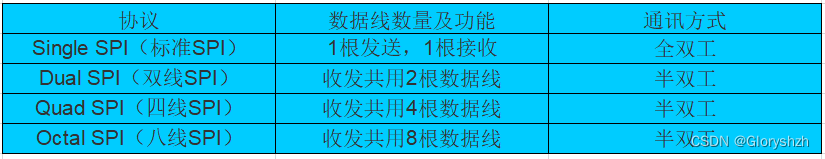

四、SPI升级版

SPI flash接口有standard SPI、Dual SPI、Quad SPI、Octal SPI,也就是所谓的1\2\4\8线模式。

五、SDR和DDR模式

五、SDR和DDR模式

SPI通信支持SDR和DDR模式。

SDR:Single Data Rate通过 SCLK 的触发对信号进行采样时,一个时钟周期只执行一次,称为单

倍数据速率模式。

DDR:Double Data Rate通过 SCLK 的触发对信号进行采样时,每个上升沿和下降沿将采样一次。

也就是说一个时钟周期内发送2位或者接收2位数据,称为双倍数据速率模式

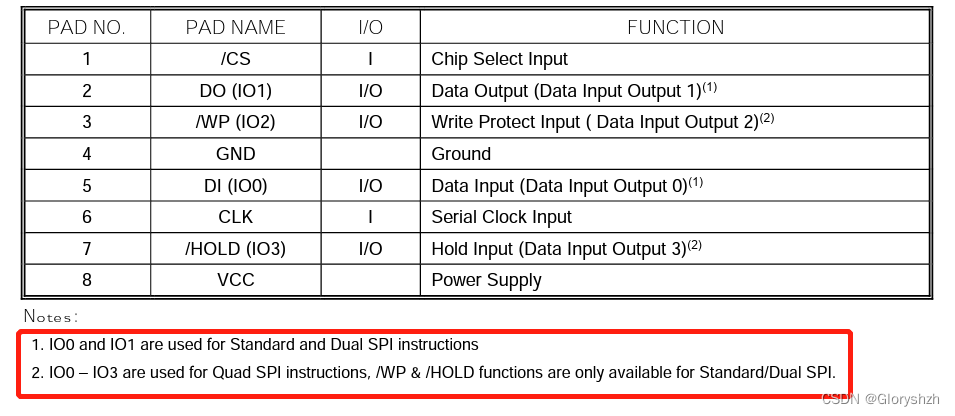

六、SPI Flash接口

Dual SPI有两根数据IO;Quad SPI有4根数据IO。

SPI flash spec:

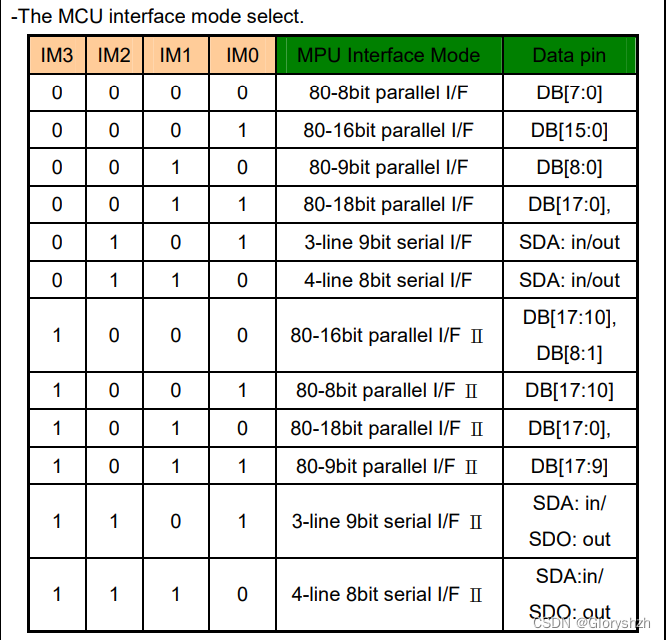

七、SPI TFT液晶屏接口

七、SPI TFT液晶屏接口

TFT液晶屏ST7789 spec定义,支持串行和并行,支持SPI多种通信模式。

八、信号定义及连线

八、信号定义及连线

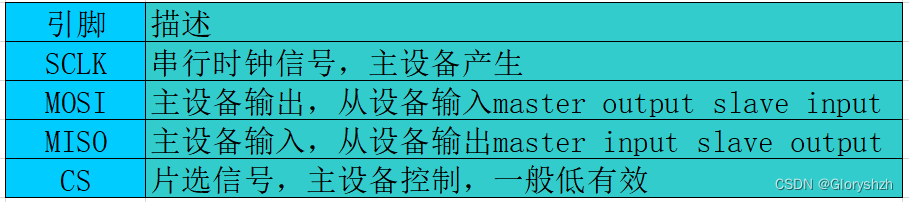

标准SPI接口信号定义:

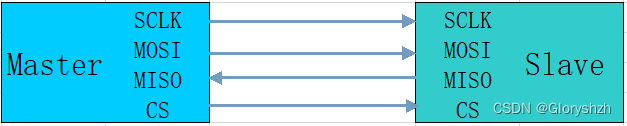

标准的SPI规范连线:

标准的SPI规范连线:

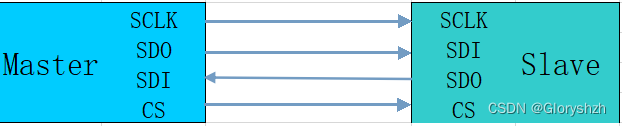

SDO\SDI网络命名的连线(SDO和SDI交叉):

SDO\SDI网络命名的连线(SDO和SDI交叉):

SPI总线,一对多连线:

九、小结

九、小结

1、有的参考设计原理图中,用SDI表示MOSI,用SDO表示MISO,连线要注意输出和输入的定义。

2、芯片引脚的信号输入或输出,是针对自身来标明的,因此在主从设备芯片的输出或输入要连接正确。

3、电路设计上引脚信号不需要上拉。如果是IO模拟的话,需注意是不是开漏,如是要加上拉。

另,要确认器件spec的SPI

信息,可能有特殊的要加上下拉。

4、一对多的连线,片选信号CS单独控制,多个从设备需要多个CS信号。

5、从设备未被选中时,信号线变成高阻态(断开)。

6、Layout上没有特殊要求,当然可以SCLK信号包下地。

本文详细介绍了SPI接口的发展、工作模式(CPOL和CPHA)、3/4线区别、SPI升级版本(如SPIFlash接口)以及SDR和DDR模式。还涉及了TFT液晶屏接口和信号定义,提醒读者注意电路设计中的细节,如信号线连接、片选、数据速率等。

本文详细介绍了SPI接口的发展、工作模式(CPOL和CPHA)、3/4线区别、SPI升级版本(如SPIFlash接口)以及SDR和DDR模式。还涉及了TFT液晶屏接口和信号定义,提醒读者注意电路设计中的细节,如信号线连接、片选、数据速率等。

996

996

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?