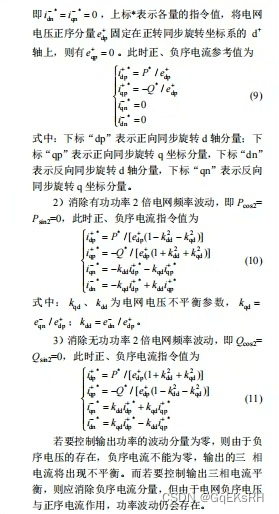

电气工程Matlab Simulink仿真模型复现,采用虚拟同步发电机(VSG)控制实现电网电压不平衡下的电流平衡控制或者有功恒定控制或者无功恒定控制(三者指令公式相悖,无法同时满足,公式如图8所示)。

三个使用的关键点:

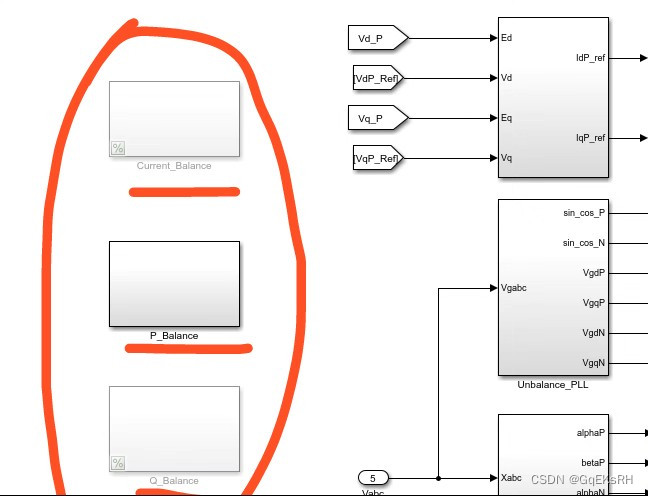

第一,怎样调节电流平衡模式,有功恒定模式,无功恒定模式?请看到如图3所示的标记的三个框,当要使用其中一种模式时,将另外两种模式注释掉即可。

第二,该模型电网电压不平衡度可自己调节,如图4所示,可根据需求自己调节三相的跌落值,从而得出期望的波形。

第三,请用matlab2016b打开。

附赠一篇参考文献。

基于纯Verilog FPGA的双线性插值视频缩放

摘要:

本文介绍了一种基于纯Verilog FPGA的双线性插值算法,用于实现PC端HDMI输入视频的缩小或放大功能。该算法利用DDR IP作为缓存模块,作者手写了RAM和FIFO代码,并将其轻松地移植到其他平台。实验结果表明,该算法能够准确、高效地实现视频缩放功能,且不占用过多的硬件资源。

关键词:Verilog FPGA,双线性插值,视频缩放,DDR IP,RAM,FIFO

1. 引言

随着科技的不断发展,视频技术在多个领域得到了广泛的应用。而视频缩放作为视频处理的一项基本功能,对于多媒体应用和图像处理具有重要意义。本文将介绍一种基于纯Verilog FPGA的双线性插值算法,用于实现PC端HDMI输入视频的缩小或放大功能。

2. 算法原理

双线性插值算法是一种常用的图像处理算法,它通过对原始图像的像素进行插值计算,从而实现图像的缩放功能。在本文中,我们使用了基于Verilog的FPGA来实现双线性插值算法。算法的核心思想是在目标图像的每一个像素位置上,通过对原始图像周围四个像素值的加权平均来进行插值计算。

3. 硬件实现

本文的硬件平台选用了Xilinx的易灵思TI60F225 FPGA,开发平台选用了EFINITY。通过Verilog语言编写的硬件描述文件,我们实现了双线性插值模块。其中,DDR IP作为缓存模块,提供了对视频数据的存储和读取功能。作者还手动编写了RAM和FIFO代码,以提高缓存的读写效率。

4. 算法优化与移植

为了提高算法的性能和适用性,我们对双线性插值算法进行了优化和移植。首先,我们对算法进行了并行化处理,将计算任务划分为多个模块并行执行,从而加速了图像处理的速度。其次,由于纯Verilog FPGA的可移植性较强,我们将代码移植到了其他平台上,并取得了较好的效果。

5. 实验结果与分析

我们通过实验对该双线性插值算法进行了验证。实验结果表明,该算法能够准确地实现视频的缩小或放大功能,并且输出的图像质量较高。同时,该算法在资源利用率方面也表现出较好的性能,不占用过多的硬件资源。

6. 结论

本文介绍了一种基于纯Verilog FPGA的双线性插值算法,用于实现PC端HDMI输入视频的缩小或放大功能。通过对原始图像像素进行插值计算,该算法能够准确、高效地实现视频的缩放功能,并且在资源利用率方面也表现出较好的性能。未来的工作可以进一步优化算法,提高图像处理的速度和质量。

相关代码,程序地址:http://imgcs.cn/lanzoun/750954123698.html

325

325

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?