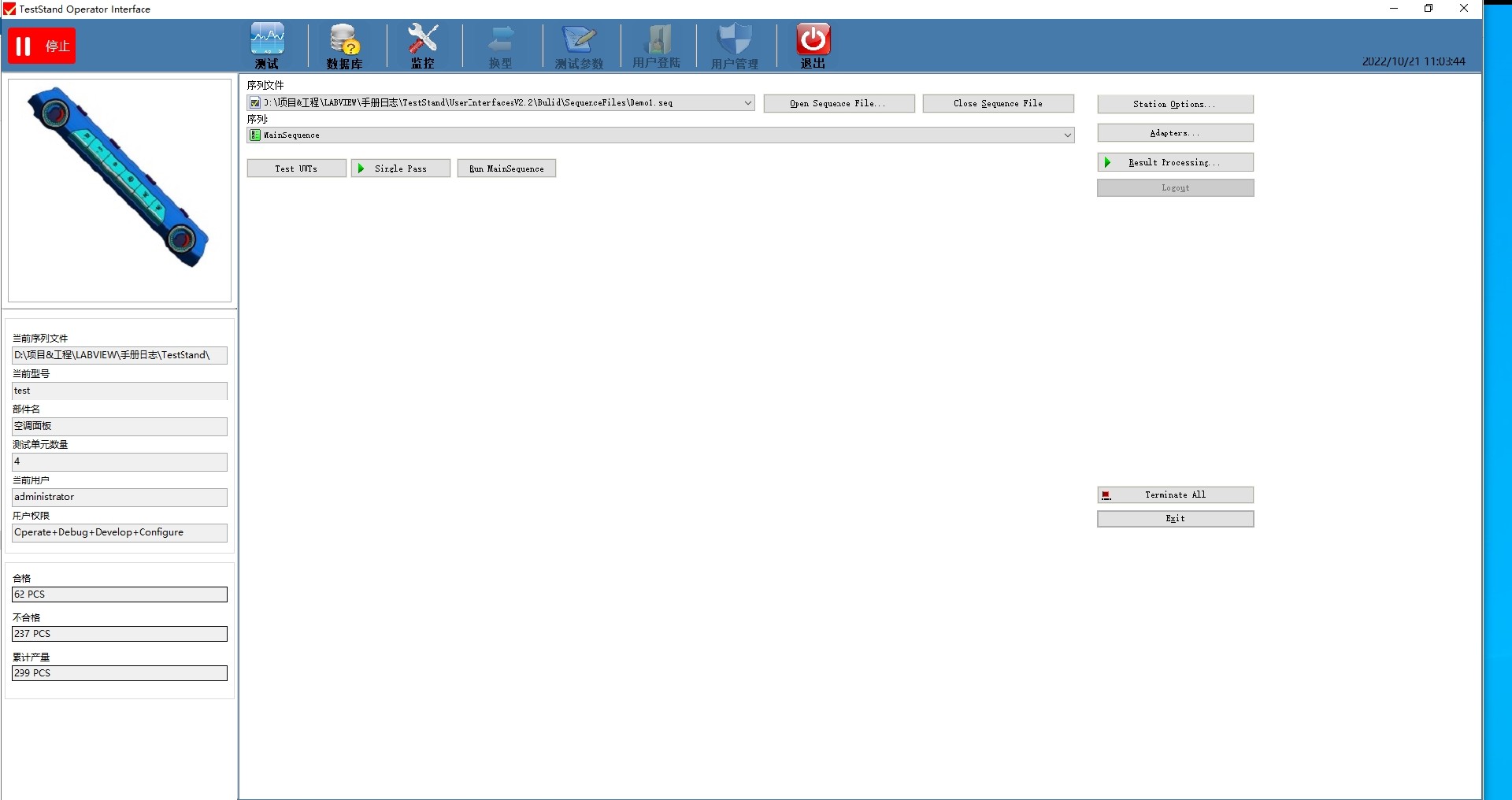

Tsetstand自定义界面,只需要把测试序列放在根目录下,最大支持6个UUT并行测试(可编辑指定)。

除了测试参数需要自己做并生成exe,界面其它功能都可以通过简单修改文本实现快速运行。

1.UUT图片可以指定路径

2.测试序列放到指定目录文件自动加载

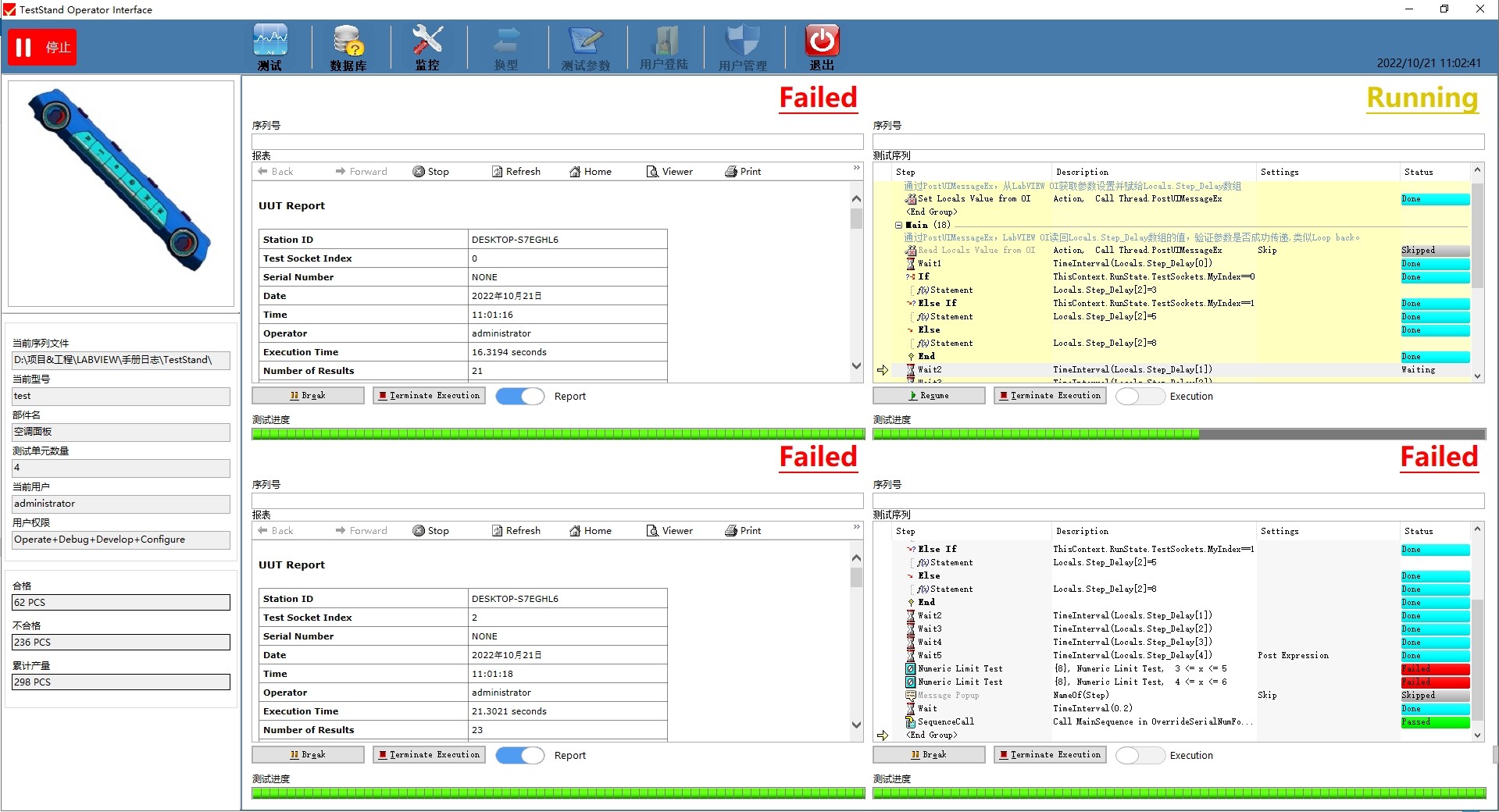

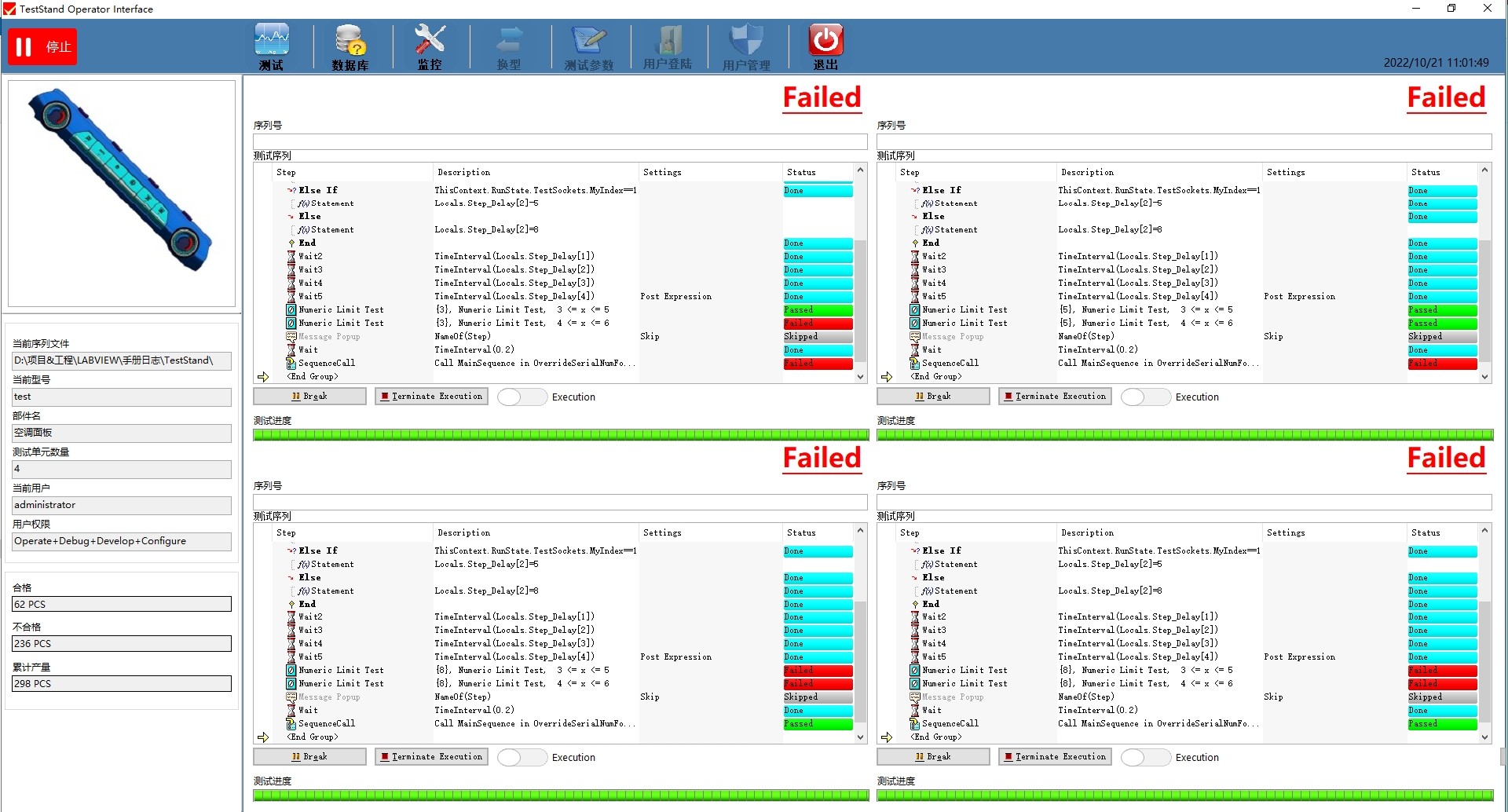

3.每个Scoket都有独立的暂停,继续,终止等控制按钮

3.每个Scoket都有独立的报表显示

4.执行视图采用TS的Execution View 控件,相比较第一版的LV表格控件,它能实时显示被嵌套调用的序列执行状态。

5.界面自由增加删除用户信息

本软件依赖于teststand2019 x86 runtime

ID:31330676018163716

芳心可可

Tsetstand自定义界面是一款强大的测试工具,它能够方便地自定义测试界面,只需将测试序列放置在根目录下即可。该工具最大支持6个UUT(被测单元)的并行测试,您可以根据需要进行编辑和指定。

在使用Tsetstand自定义界面时,除了测试参数需要自行制作并生成exe文件外,其他功能均可通过简单修改文本实现快速运行。这一特点使得用户能够灵活地应对各种测试需求,提升测试效率。

下面是Tsetstand自定义界面的一些功能与特点:

-

UUT图片路径指定:用户可以通过指定图片路径,将对应UUT的图片与测试结果关联起来,从而更直观地了解测试过程中各个UUT的状态。

-

自动加载测试序列:将测试序列放置在指定目录下,Tsetstand自定义界面会自动加载这些序列文件,方便用户快速选择测试流程。

-

独立的控制按钮:每个Scoket(测试通道)都具有独立的暂停、继续和终止等控制按钮。这样,用户可以对单个通道进行灵活控制,增强了测试过程的可控性。

-

独立的报表显示:每个Scoket都有独立的报表显示功能,用户可以查看单个通道的测试结果,从而更为详细地了解每个UUT的测试情况。

-

使用TS的Execution View 控件:执行视图采用TestStand(简称TS)的Execution View 控件,相较于第一版的LV表格控件,它能实时显示被嵌套调用的序列执行状态。这一功能提升了用户对测试流程的可视化程度,便于用户监控和调试。

此外,Tsetstand自定义界面还支持界面的自由增加和删除用户信息,用户可以根据需要进行界面的个性化定制。

需要说明的是,本软件依赖于teststand2019 x86 runtime,这一点用户在使用时需要注意。

总结起来,Tsetstand自定义界面是一款功能强大,操作简便的测试工具,它通过自定义界面、独立控制按钮、独立报表显示等特点,将测试过程变得更加灵活和高效。用户可以根据自己的需求,灵活配置和管理测试流程,提高测试效率和准确性。无论是对于专业的测试人员还是对于普通的程序员来说,Tsetstand自定义界面都是一款实实在在的技术分析工具,而非仅仅是一份广告软文。

(字数:447)

以上相关代码,程序地址:http://coupd.cn/676018163716.html

304

304

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?