点击蓝字关注我们

关注、星标公众号,精彩内容每日送达

来源:网络素材false path是STA中的一个非常常见的术语。它指的是不需要优化timing路径,在芯片的正常工作情况下,这个path的timing永远不需要满足。在正常情况下,从触发器发出的信号必须在一个时钟周期内被另一个触发器捕获。然而,在某些情况下,来自launch 触发器的信号在什么时间到达接收触发器并不重要,导致此类场景的tming路径被标记为false path,并且不需要通过优化工具优化timing。

常见的false path场景:下面,我们列出了一些可以应用false path的示例:

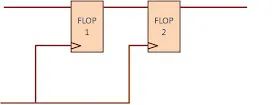

信号同步:假设我们在发送和接收触发器之间放置了一个双触发器同步器(发送和接收触发器可能在不同的时钟域或同一时钟上工作)。在这种情况下,不需要满足从发送触发器到同步器第一阶段的timing。下图1显示了一个双触发器同步器。我们可以认为flop1的信号是假的,因为即使信号导致flop1亚稳定,它也会在下一个时钟边沿到达之前稳定,成功率由同步器的MTBF控制。这种false path也被称为时钟域交叉(CDC)。

然而,这并不意味着无论你在哪里看到两个触发器,都有第一个触发器的false path。这两个触发器可能是为了打拍逻辑。因此,一旦确认存在同步器,您就可以将信号指定为false。

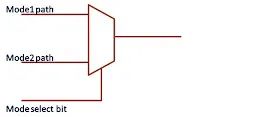

由于模式合并而产生的静态信号的false path:假设您有一个结构,如下图所示。您有两种模式,多路复用器输出的路径因模式而异。您可以通过选择多路复用器来指定false path,如果没有与模式转换相关的特殊timing要求,这在两种模式信号下都是静态的。具体来说,对于下图所示的情景,

Mode 1 : set_case_analysis 0 MUX/SEL

Mode 2 : set_case_analysis 1 MUX/SEL

Mode with Mode1 and Mode2 merged together : set_false_path -through MUX/SEL

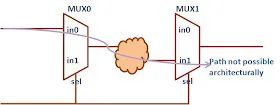

架构false path:有一些timing路径永远不会发生。假设我们有一个场景,其中两个2:1多路复用器的选择信号与同一信号绑定。因此,不可能存在通过MUX0的in0引脚的数据可以穿越MUX1的in1引脚的场景。因此,这是架构的false path。下图描述了场景。

指定false path:将timing路径指定为false path的SDC命令是“set_false_path”。在以下情况下,我们可以应用false path:

寄存器到寄存器

set_false_path -from regA -to regB

时钟域到时钟域

set_false_path -from [get_clocks clk1] -to [get_clocks clk2]

通过某个信号

set_false_path -through [get_pins AND1/B]

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?