点击蓝字关注我们

关注、星标公众号,精彩内容每日送达

来源:网络素材本文包含两部分内容:1)AXI接口简介;2)AXI IP核的创建流程及读写逻辑分析。

1 AXI简介(本部分内容参考官网资料翻译)

自定义IP核是Zynq学习与开发中的难点,AXI IP核又是十分常用的自定义IP核,因此掌握AXI IP核的创建流程及通信机制显得尤为重要。要搞懂AXI IP核,就必须先了解AXI接口。先介绍如下:

1) AXI(Advanced eXtensible Interface)协议主要描述了主设备(Master)和从设备(Slave)之间的数据传输方式,主设备和从设备之间通过握手信号建立连接。当主设备的数据准备好时,会发出和维持VALID信号,表示数据有效;当从设备准备好接收数据时,会发出READY信号。数据只有在这两个信号都有效时才开始传输。

2) AXI协议(又称AXI4.0),包括3种接口标准:AXI4、AXI-Stream、AXI-lite。

AXI4:适用于要求数据高速传输的场合。

AXI-Stream:如FIFO,数据传输不需要地址,而是主从设备间直接进行数据的读写,主要用于高速数据传输的场合,如视频、高速AD等。

AXI-lite:可用于单个数据传输,主要用于访问一些低速外设。

3) AXI接口具有5个独立通道:WriteAddress通道、Write Data通道、Write Response通道、Read Address通道、Read Address通道、Read Data通道。

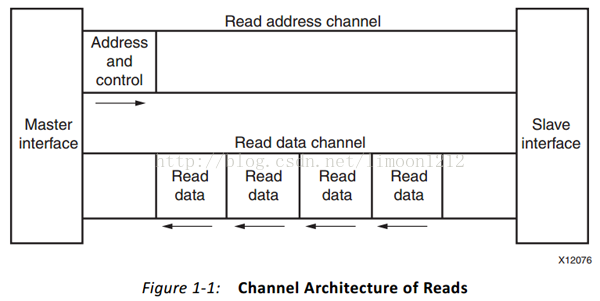

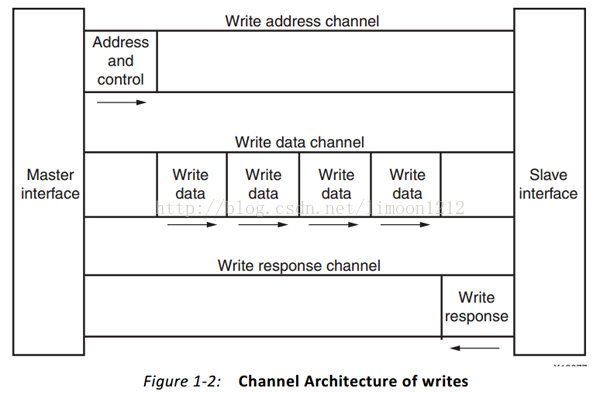

4) 读/写通道并行地进行数据交互,明显提高了数据吞吐量,对写数据,从设备会返回确认信号,这样可以保证写数据通道的安全,读/写模型分别如图1-1、图1-2。

读模型:主设备发送读地址占用信号给从设备→从设备将数据写入主设备,实现读操作。

写模型:主设备发送写地址占用信号给从设备→主设备将数据写入从设备→从设备回复确认收到信号,实现写操作。

5) AXI协议严格来讲是一个点对点的主/从接口协议,当多个外设需要互相交互数据时,我们需要加入一个AXI Interconnect模块,也就是AXI互联矩阵,AXI Interconnect的作用是将一个或多个AXI主设备连接到一个或多个AXI 从设备。

6) AXI Interconnect IP核最多支持16个主设备和16个从设备,如果需要更多的接口可以在设计中加入多个IP核。

7) ZYNQ中的AXI接口包含三个类型,共9个,主要用于PS与PL的互联。

(1)AXI_HP接口(PL模块作为主设备)

包括4个,主要用于PL访问PS上的存储器。每个接口都有两个FIFO缓冲器,一个是读缓冲,一个是写缓冲。

【实例:设计视频处理时,高清的图像可由FPGA直接完成采集、预处理,然后通过AXI_HP接口将数据高速传输至DDR中,供APU(加速处理器)完成进一步的图像处理】

(2)AXI_ACP接口(PS端是从设备端)

只有1个,又叫加速器一致性端口,适合做专用指令加速器模块接口。PL端可直接从PS部分的Cache中拿到CPU的计算结果,同时也可以第一时间将逻辑加速运算的结果送至Cache中,延时很小。

(3)AXI_GP接口(PS端是从设备端)

通用AXI接口,总共有4个。可用于控制电机运转,获取传感器信号等逻辑模块的连接接口。

2 AXI IP核的创建流程及读写逻辑小结

(1)AXI IP核的创建流程(以AXI PWM IP为例)

环境:win 7 +64(i5,4G) Vivado 2014.4+Xilinx SDK2014.4

开发板:zedboard version d xc7z020clg484-1

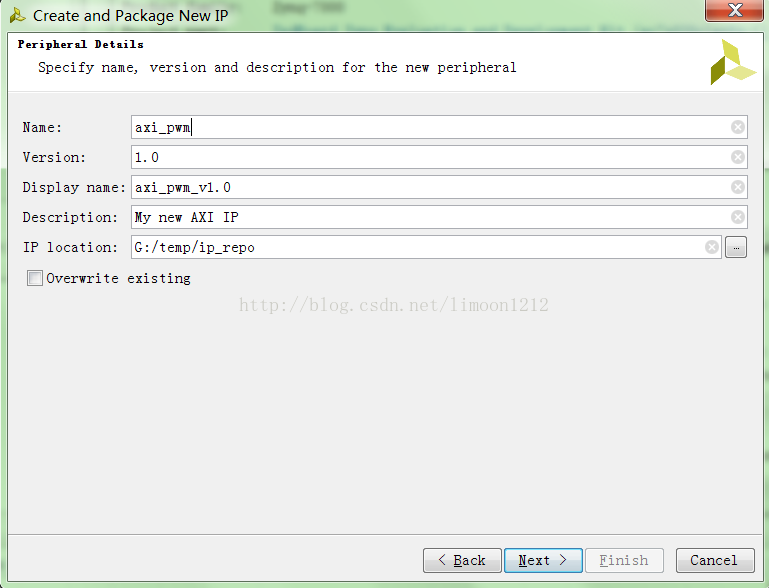

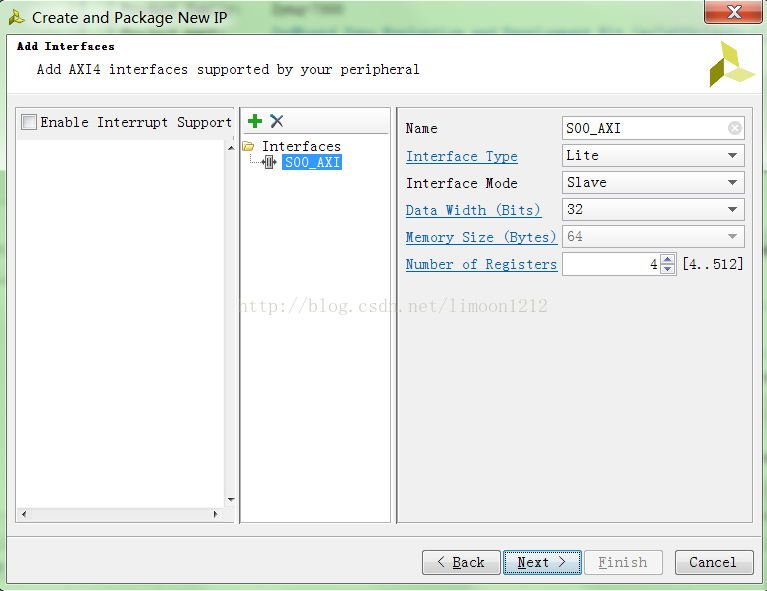

1) 新建工程→Tools → Create and PackageIP → Next → Create a new AXI4 peripheral → 修改name: axi_pwm(如图1)→ Next → 为用户IP核添加AXI4总线接口的支持(如图2)→ Add IP to the repository →Finish

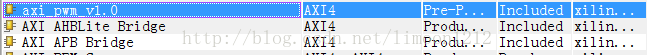

2) 在Flow Navigator中选择 IP Catalog,打开IP管理器,看到刚才添加的axi_pwm_v1.0(如图3)→ 右击axi_pwm_v1.0 → Edit in IPPackager选项,单击OK,此时系统会自动打开另一个Vivado IDE来对用户IP核进行编辑,完成IP核的封装。

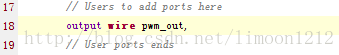

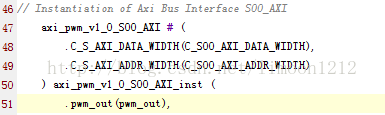

3) 在新打开的VivadoIDE中,在source窗口中双击打开axi_pwm_v1_0.v顶层文件,添加用户自定义端口pwm_out(如图4),并对端口进行例化(如图5)。

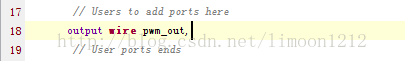

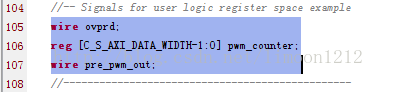

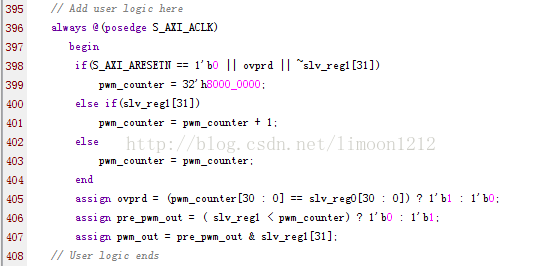

4) 双击打开axi_pwm_v1_0_S00_AXI.v实例化文件,添加端口声明(如图6),添加用户信号(如图7),添加用户逻辑(如图8)。

图 6

图 7

图 8

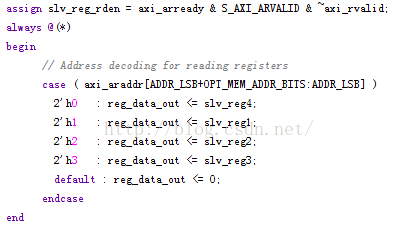

前面看到是用户写数据及其IP核接收到的数据寄存器,下面是IP核的输出数据,也就是用户在读IP核时被读的寄存器:

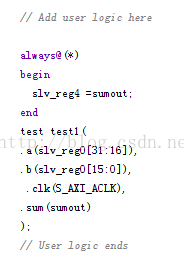

先定义一个寄存器slv_reg4:

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg4;

又添加了一条:

wire [C_S_AXI_DATA_WIDTH-1:0] sumout;

主要是为了把test.v这个模块添加进来;

这里在实验中,做了一些更改,将slv_reg0,变为了slv_reg4;

最后在用户逻辑部分,添加例化的模块。

这样,用户在读地址00的时候,读到的值便是sumout。

5) 切换到Package IP-axi_pwm窗口,点击CustomizationParameters,单击如图9所示链接,对刚才修改过的顶层文件进行更新。

图 9

6) 点击Review and Package →Re-Package IP,至此,AXI PWM IP核设计完成。

(2)读写逻辑小结

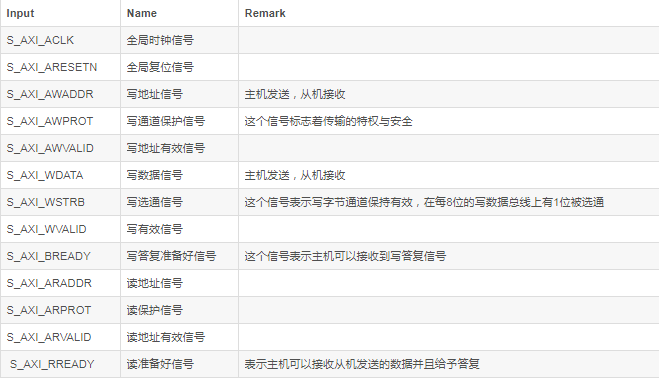

a. 输入信号:

b. 输出信号:

c. 4个从机寄存器(在创建AXI IP时,可以自己设定个数,如图2)

slv_reg0;slv_reg1; slv_reg2; slv_reg3;

d. 读写逻辑示意

写://写准备好信号——写准备好地址总线被占用——写地址通道有效——写地址选择——写数据传输——写应答回复

读://读地址准备好——读总线被占用——读地址有效信号产生——读数据总线有效——读数据有效——读地址有效——主机寄存器读取数据

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

2972

2972

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?