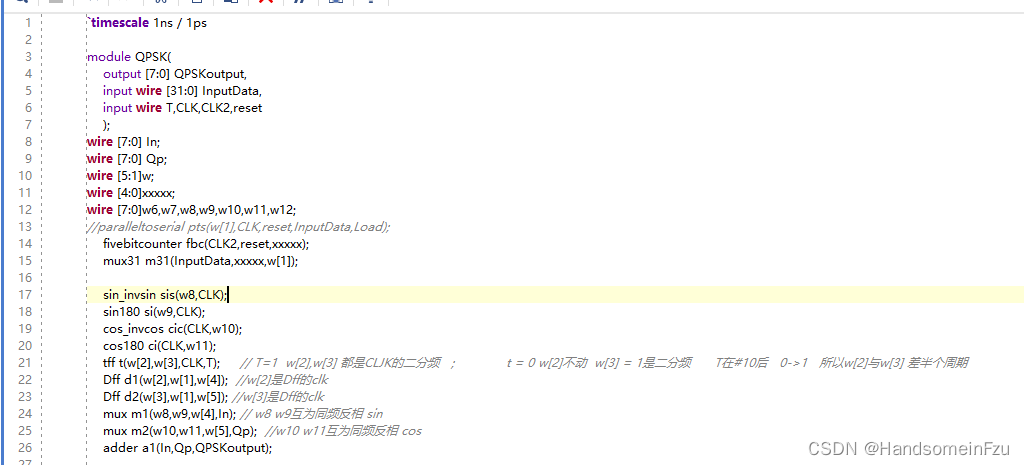

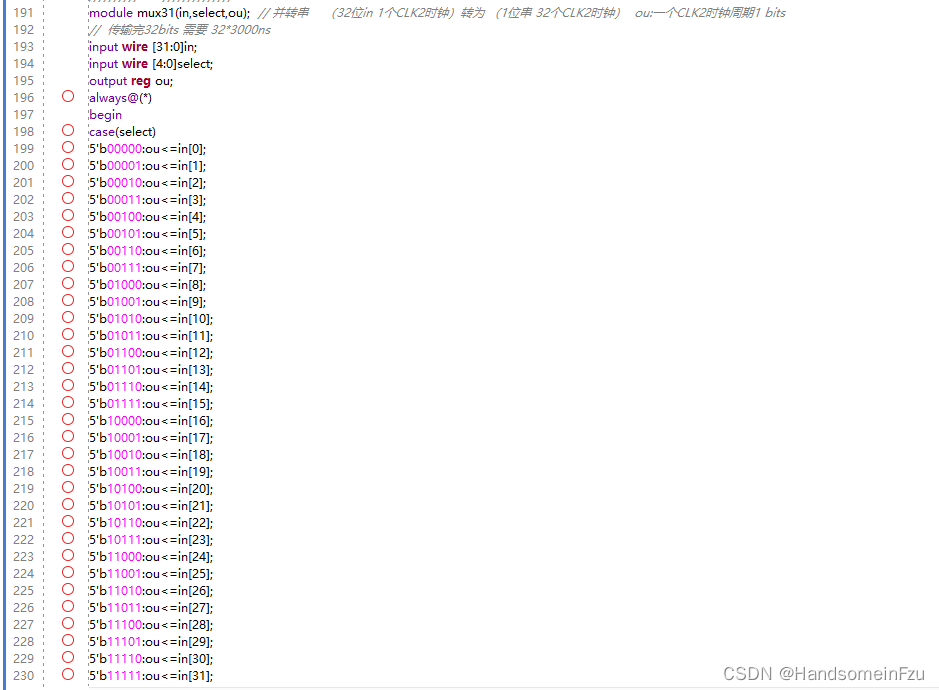

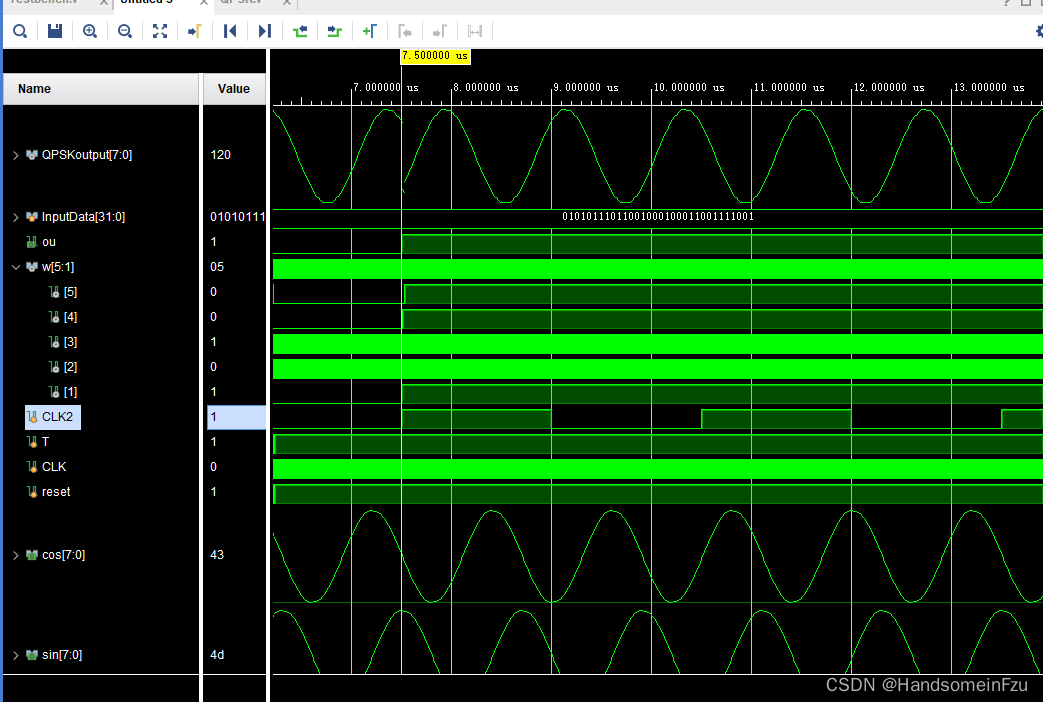

输入32bits 并行数据,输出 8bits 数据

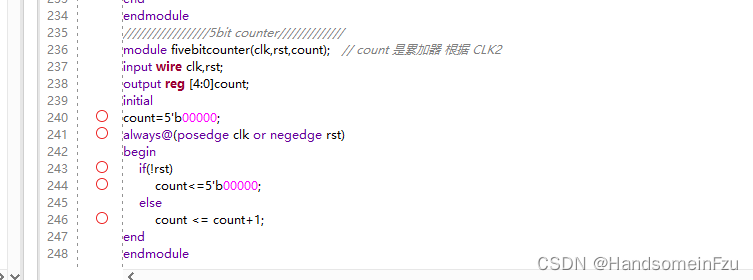

CLK2 是CLK的150倍分频; 将并转串 ,每CLK2周期传1 bit

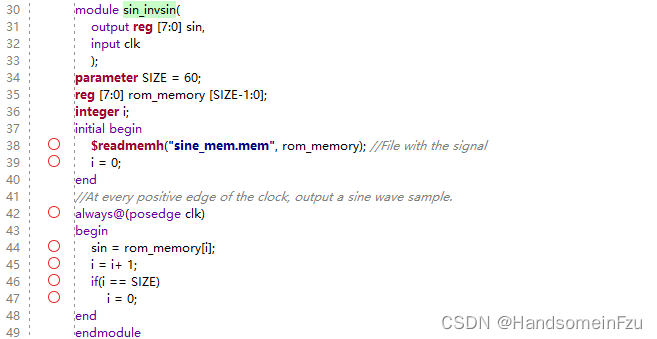

产生-sin (因为QPSK调制方式等效于两个BPSK相加 即 Acoswt - Bsinwt

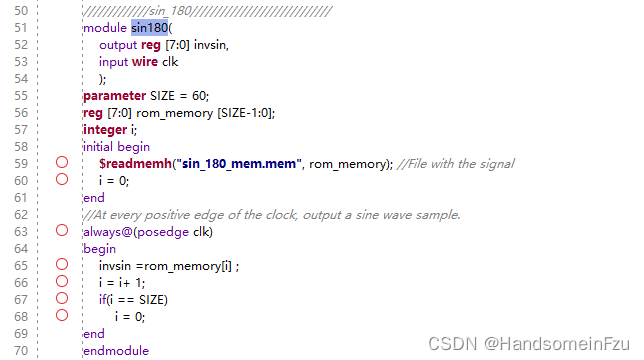

产生 sin , 与上面的sin 同频反相

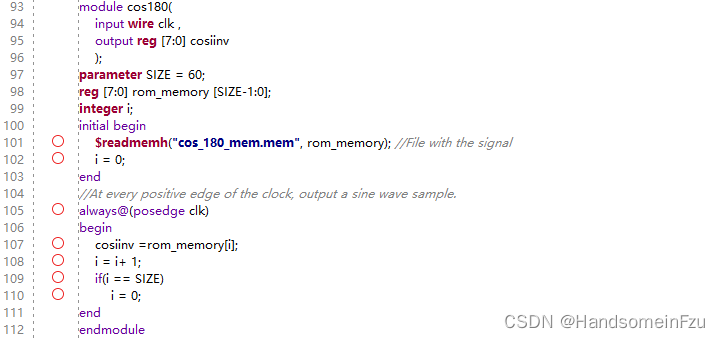

同理是cos 和 -cos

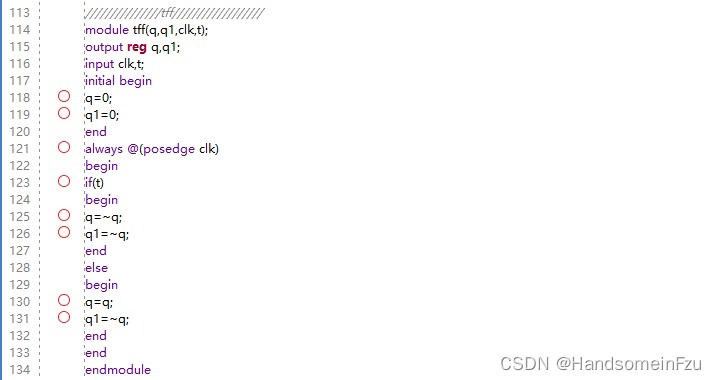

为了产生相差半个周期的时钟,受t 控制:

把第二位赋值第三位

![]()

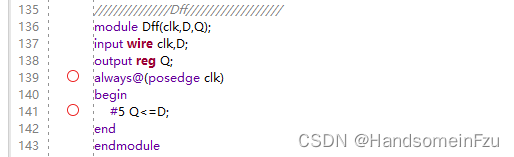

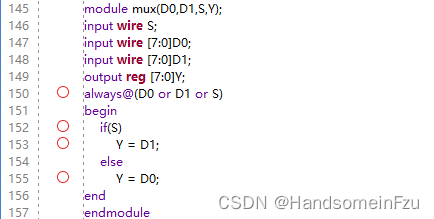

选择器:

信息比特是1:cos 0:-cos 等效于调制。

![]()

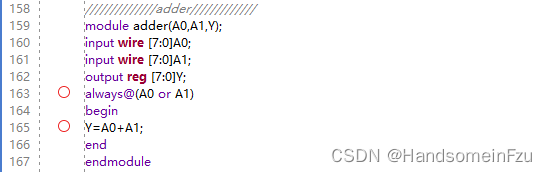

最后是相加:

adder a1(In,Qp,QPSKoutput);

波形:

资源下载:

(31条消息) QPSK-using-VERILOG-HDL-master.rar资源-CSDN文库

2575

2575

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?