training-28nm

floorplan

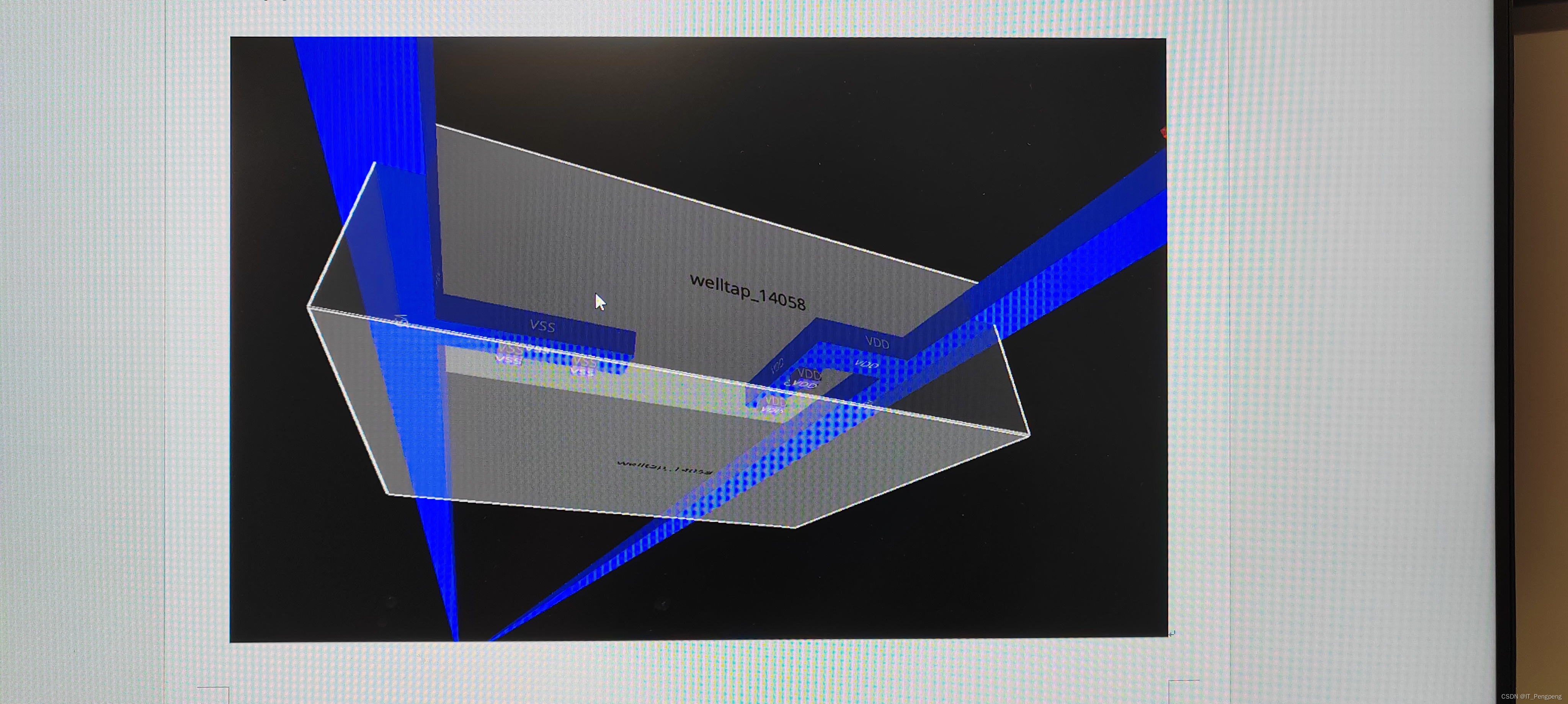

endcap welltap分布情况

endcap在左边分布是ENDTIEL(靠边)和ENDCAPL组合分布,在右边是ENDTIER(靠边)和ENDCAPR组合。在上边和下边是ENDTIE。

welltap从上到下覆盖整个core区域。

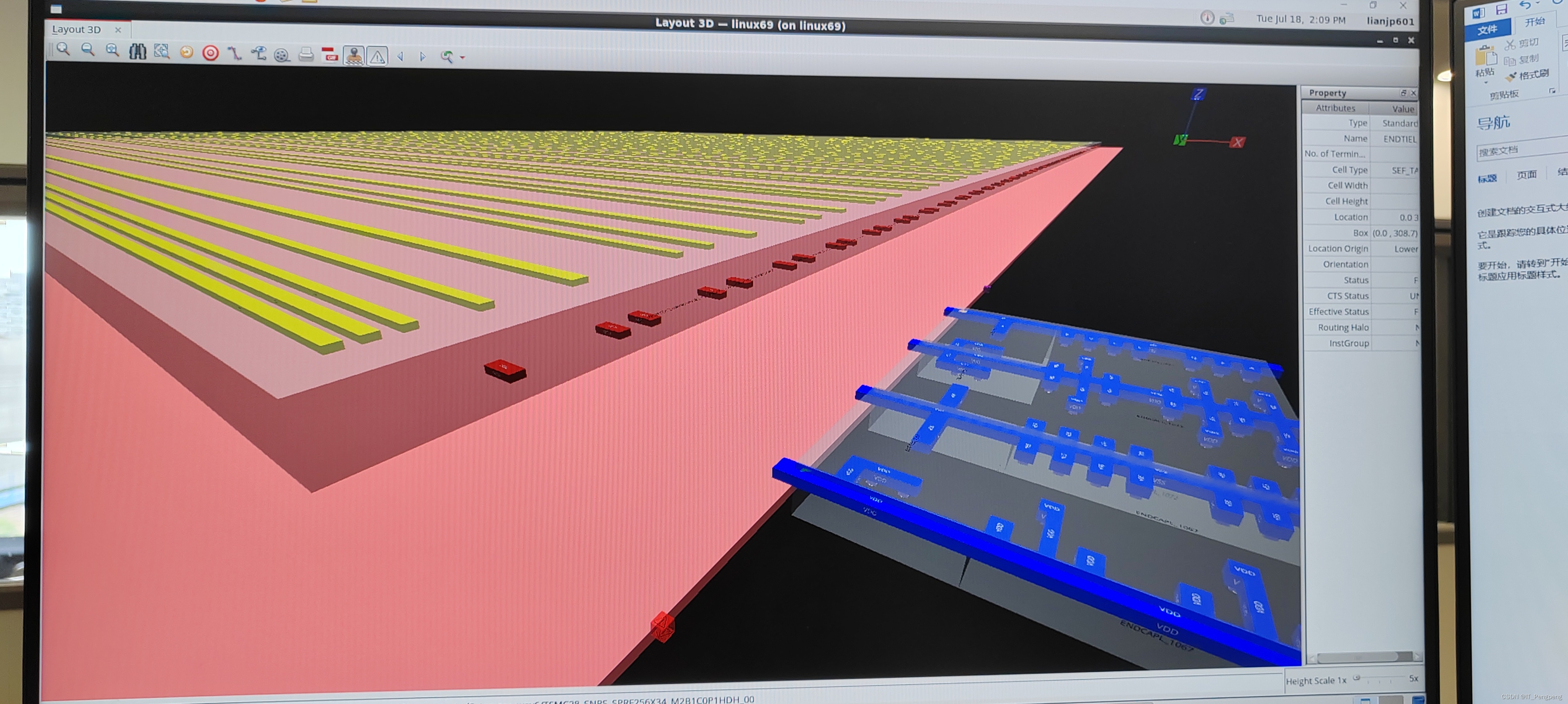

cell分布

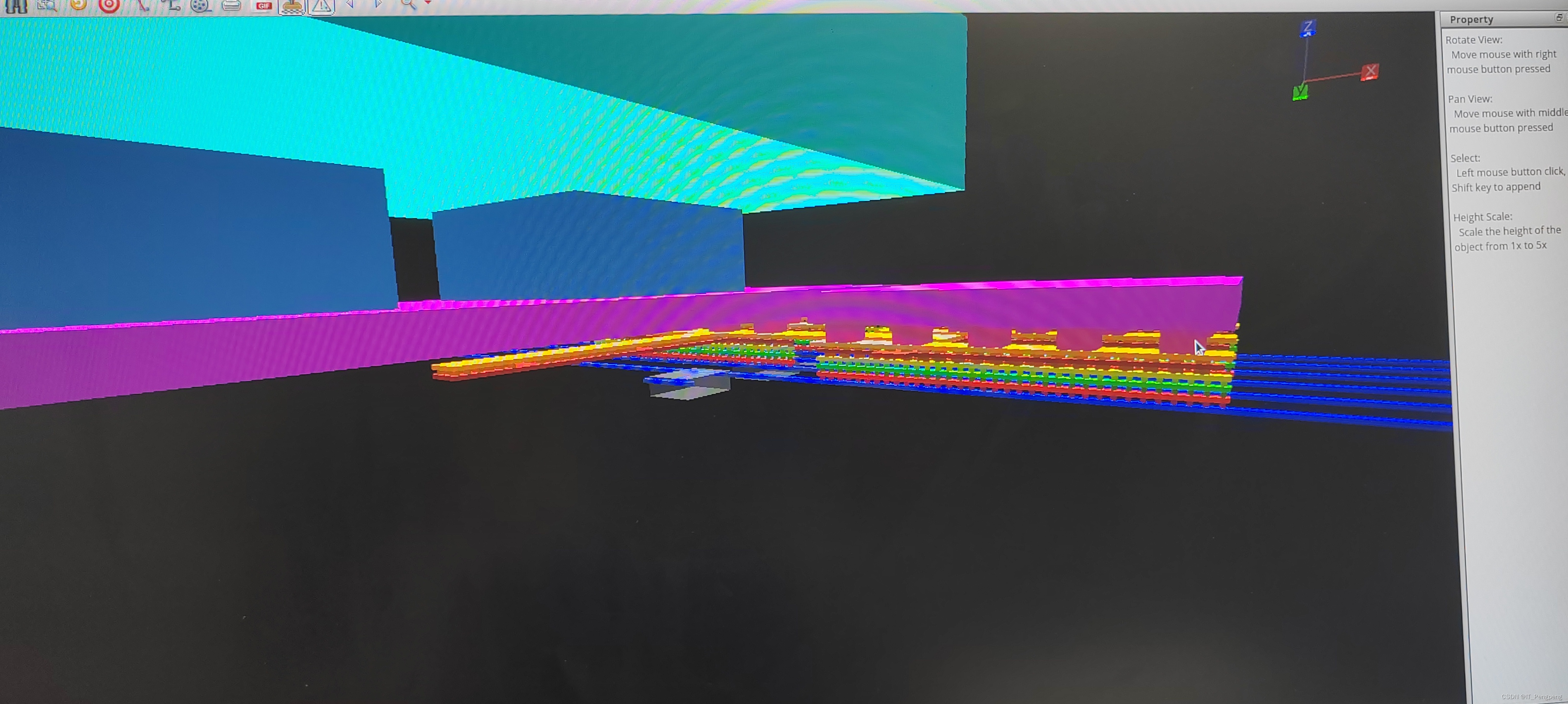

cell分布在M0层,M1层电源线穿过cell并与cell里的VDD和VSS相接。memory一共占从M0到M4,pin在M2,电源线在M4。

如果想和core区域的std连接,可以用于布线的资源,memory之间缝宽度内M2到M4的布线资源,以及M4层以上的布线资源。所以建议缝宽度达到要求。

层叠结构

电源规划

-

定义全局连接关系

globalNetConnect VDD -pin VDD -type pgpin -all -override globalNetConnect VDD -pin VDD -type pgpin -all -override -

添加电源环power ring

-

添加power stripe

也负责添加via。

addStripe -

添加电源轨道followpins或power rail

为std cell提供供电网络。需要在每条row上打上电源线,然后std cell放上面,就能实现供电。

sroute -connect {corePin} -

通电

供电IO单元和power ring连接起来,形成一个完整的供电网络。

-

添加电源通孔

-

一些操作

删除所有电源线

deleteAllPowerPreroutes替换via cell

#VIA1替换 1、2层之间 deselectAll editSelectVia -cut_layer VIA1 -net {VDD VSS} dbGet selected.via.name -u editChangeVia -net VDD -area {0 0 9000 9000} -from VIAGEN12_RECT_1 -to TSEDI_V12_2x1 editChangeVia -net VSS -area {0 0 9000 9000} -from VIAGEN12_RECT_1 -to TSEDI_V12_2x1 #VIA2替换 2、3层之间 deselectAll editSelectVia -cut_layer VIA2 -net {VDD VSS} dbGet selected.via.name -u editChangeVia -net VDD -area {0 0 9000 9000} -from VIAGEN23_RECT_1 -to TSEDI_V23_2x1 editChangeVia -net VSS -area {0 0 9000 9000} -from VIAGEN23_RECT_1 -to TSEDI_V23_2x1 #VIA3替换 3、4层之间 deselectAll editSelectVia -cut_layer VIA3 -net {VDD VSS} dbGet selected.via.name -u editChangeVia -net VDD -area {0 0 9000 9000} -from VIAGEN34_RECT_1 -to TSEDI_V34_2x1 editChangeVia -net VSS -area {0 0 9000 9000} -from VIAGEN34_RECT_1 -to TSEDI_V34_2x1 #VIA4替换 4、5层之间 deselectAll editSelectVia -cut_layer VIA4 -net {VDD VSS} dbGet selected.via.name -u editChangeVia -net VDD -area {0 0 9000 9000} -from VIAGEN45_RECT_1 -to TSEDI_V45_2x1 editChangeVia -net VSS -area {0 0 9000 9000} -from VIAGEN45_RECT_1 -to TSEDI_V45_2x1

添加IO

-

创建group

-

添加pin到group

-

创建pin guide,规划区域,规划区域时规划的面积一定要包含core area以外,否则pin guide不能成功。

-

布置IO

createPinGroup cpupingrp -cell cpu_sys_top -excludePin sameLayer

addPinToPinGroup -cell cpu_sys_top -pinGroup cpupingrp -pin *

createPinGuide -area {250 1116.082 450 1126.082} -name cpupingrp -cell cpu_sys_top layer {5}

assignIoPins -pin * -moveFixedPin

添加Halo

deleteHaloFromBlock -allMacro

addHaloToBlock left bottom right top -allMacro -snapToSite

添加physical cell

deleteInst *welltap*

deleteInst *ENDCAPL*

deleteInst *ENDCAPR*

deleteInst *ENDTIE*

source ../tcl/encounter_db_proc.tcl

source ../tcl/addEndCapTie_28.tcl

addWellTap -checkerBoard -cell SEF_TAPDS -prefix welltap -cellInterval 58

deleteFiller -prefix GFILL

add_gate_array_filler -cell SEG_DCAP_ECOCT_12 -stepx 49.98 -stepy 50.4 -prefix GFILL

检查

checkPlace #检查重叠,是否缺少模块,是否超过core area。

macro摆放原则

- macro出pin方向朝向core区域

- IO方向检查,对于不同的边,IO放在不同的layer上,例如IO在上下两边,则需放置在电源线为H的layer;IO在左右两边,则需放置在电源线为V的layer。

- macro出pin走线至core区域,最大长度要在400um以内。

- memory之间间距控制在3um左右,背靠背时,也需要有1um的间距。缝大于3um,就需要打placementblockage。

- macro pin摆布为V的时候,优先摆放左右两边,优先把Pin直接露出来。

- 优先摆放和其他模块有较多联系的macro。

- block尽量贴近于正方形。

- 属于一个大module的macro放在一起,避免走线过长。

- 小的macro可以叠层,来创造更多靠边放置的资源。

- 避免狭窄区域,避免旮旯区域。

- 尽量不要留大缝,因为不打算插buffer cell,控制长度在400um以内就可以。

库类型

- SVF时7T,SEF是9T。

结尾

本次项目目前做完floorplan,后续持续更新PR等各个环节的设计要点和思路,希望各位老铁关注我联系我!

1919

1919

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?