引言

具有硅通孔互连的三维集成电路在开发高速、紧凑和高功能的电子系统方面是有效的。事实上,3D-IC技术已经用于部分系统的量产。需要更小的TSV、更低的TSV成本和更高的TSV 成品率,才能 3D-IC技术的应用扩展到各种系统。在TSV形成工艺中,减小TSV尺寸和提高TSV良率方面是有效的,因为可以容易地形成小TSV,以及很容易在之间形成电接触TSV 和多层互连。但是,为确保与Cu-TSV底部的电接触,必须执行Cu-TSV显露工艺。

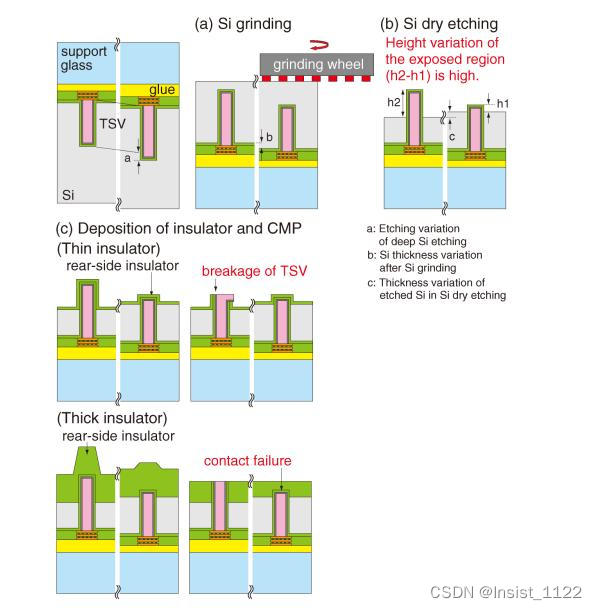

通常,Cu-TSV reveal 是通过Si研磨、Si干法蚀刻、背面绝缘体沉积和化学机械抛光(图 1)。该工艺的缺点是,由于暴露区域的高度变化较大,因此在CMP工序中可能会发生TSV破损或接触故障。

图1:常规的Cu-TSV显示过程

实验

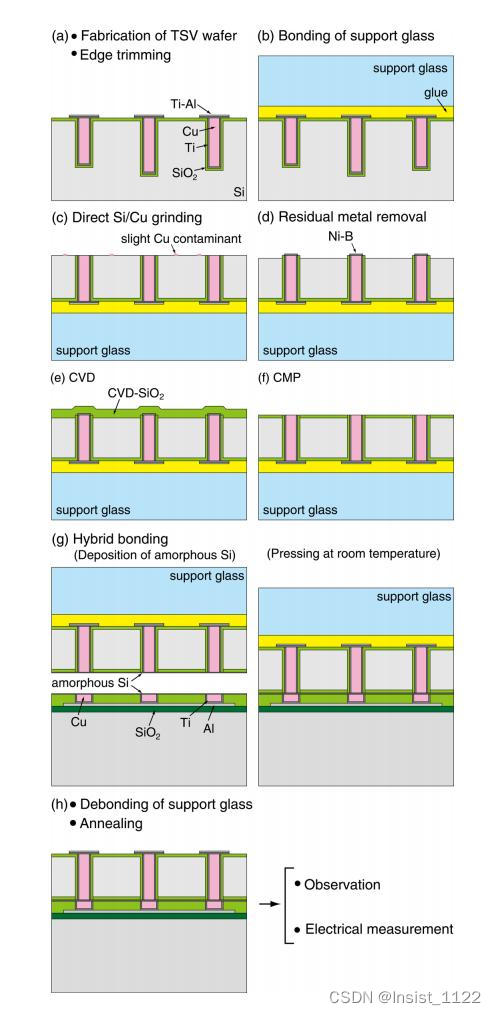

图2为中间通道Cu-TSV晶片的制作流程和三维叠加。首先,通过深硅蚀刻、使用四乙基正硅酸盐和o2气体的化学气相沉积、屏障种子层沉积、自下而上的Cu电镀、CMP和Ti-Al布线形成,制备了直径为200 mm的TSV晶片。tsv的直径和深度分别为5.5μm和33μm。随后,修整晶片的边缘。修剪后的Si的宽度和深度分别为1.5 mm 和0.15 mm。然后,使用胶粘住支撑玻璃,并进行直接Si/Cu研磨。

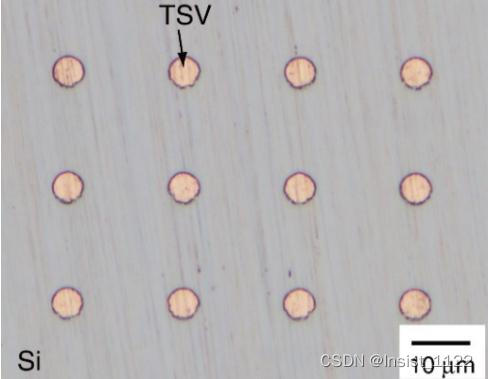

因此,我们可以对直径为 5.5μm的TSV进行均匀显示(见图3)。 直接 Si/Cu 研磨后的TSV厚度约为22 μm。随后,通过化学镀 Ni-B 和 Si 的碱性蚀刻,减少了TSV之间 Si 区域中的轻微 Cu 污染。(江苏英思特半导体科技有限公司)

图3:直接硅/Cu研磨显示的tsv的光学显微图

结果和讨论

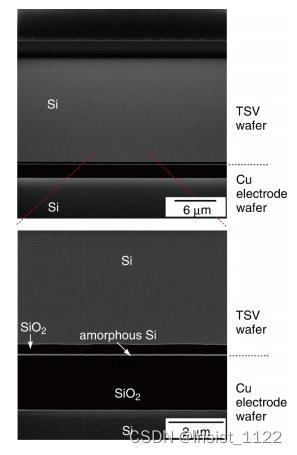

图5和图6分别显示了 Si 区域和 TSV-Cu 对区域的横截面扫描离子显微镜 (SIM) 图像。视角为45°。不仅 SiO 2 -SiO 2界面而且 TSV-Cu 电极界面也被键合。这是由于Si超薄膜的作用。(江苏英思特半导体科技有限公司)

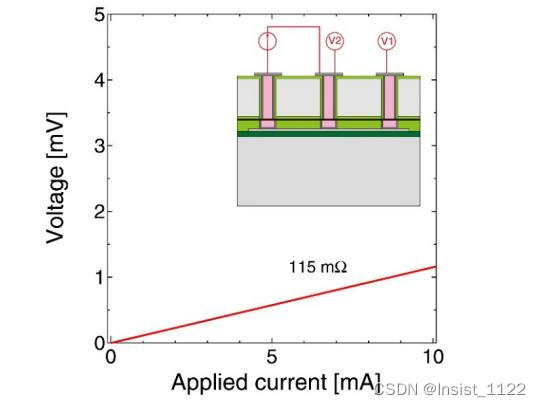

图7显示了四端测量的结果。即使在TSV和Cu电极之间插入了Si超薄膜,施加的电流和TSV-Cu电极对两端的电压之间的关系也是线性的。此外,测得的TSV-Cu电极对的电阻很低(大约 0.12 Ω)。

图5:Si区域的横断面SIM图像。

图2:中间通道Cu-TSV晶片的制作流程和三维叠加。

图6:TSV-Cu电极对的横截面SIM图像。

图7:四端子测量结果

结论

我们对使用直接Si/Cu研磨、残余金属去除、CVD和CMP制造的通孔中间TSV晶圆进行了混合键合。通过使用Si超薄膜的表面活化接合在室温下进行接合。我们还证明了不仅 SiO 2 -SiO 2界面而且TSV-Cu电极界面都被Si超薄膜粘合。TSV-Cu电极对的测量电阻很低,TSV-Cu电极对之间的漏电流也很低。在这个实验中,两个晶圆被键合。然而,我们相信通过在室温下重复混合键合和支撑玻璃的剥离,可以相对容易地堆叠三个或更多晶圆。

江苏英思特半导体科技有限公司主要从事湿法制程设备,晶圆清洁设备,RCA清洗机,KOH腐殖清洗机等设备的设计、生产和维护。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?