1 设计要求

- 试设计一个简易的处理器,该处理器处理的数据宽度是8bit,可以实现至少8种算术运算和逻辑运算

- 可以实现算术加法、算术减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或共8种运算。

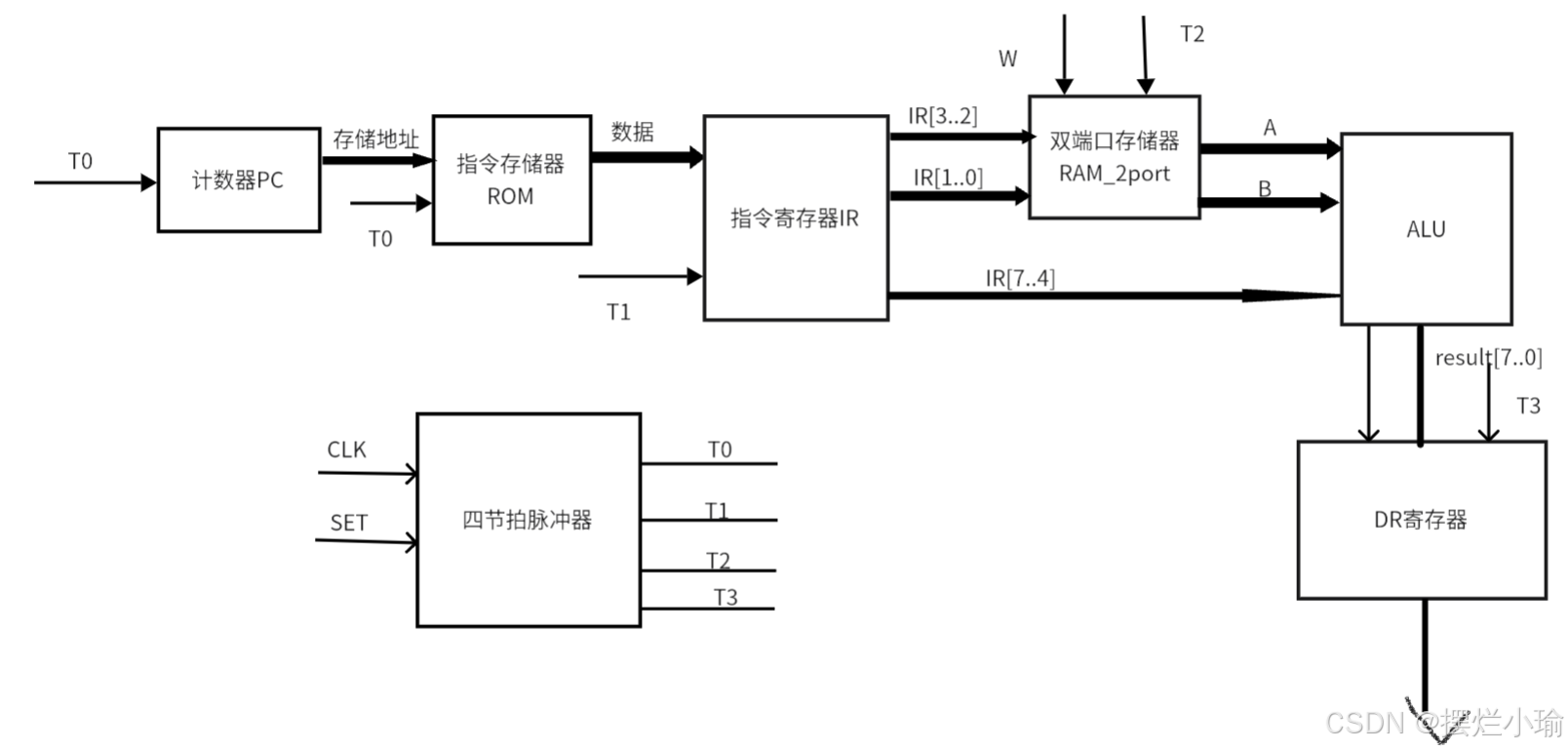

2 系统总体设计

2.1 设计模块

- 四节拍脉冲发生器:当rst置1时,输入四个时钟信号CLK后可输出四个脉冲周期T0、T1、T2、T3。

- 程序计数器PC:可以自加一也可以自定义输入地址,当set_pc为低电平时,可以自行输入地址,当set_pc为高电平时,PC自动加一,之后再将地址传给指令存储器ROM;

- 指令寄存储器ROM:根据PC传过来的地址在IR中取指令,将写好并已经存入ROM的8位指令传送给指令寄存器IR。

- 指令寄存器IR:将ROM传过来的8位指令进行处理,并将高四位输出给ALU作为操作码,低四位输出分成两部分组成RD[1..0]、RS[1..0]作为地址码传入通用寄存器组。

- 通用寄存器组:由两个部分组成,一个是数据存储模块,另一个是数据选择模块,数据存储用来存放外部输入的8位操作数DATA[7..0],将DATA[7..0]存储到G1到G4上,数据选择模块再根据IR传入的2位的地址码RD[1..0]、RS[1..0]进行取值作为操作数A[7..0]和B[7..0],并传送A和B到运算器ALU。

- 运算器ALU:对通用寄存器组传输进来的数据按照IR传进来的四位操作指令进行对应的运算,并将运算结果传送给数据存储器;

- 数据存储器:用来存储运算的结果并输出运算结果。

2.2 输入输出端口

- 输入端口:

SW[0]:控制四节拍脉冲器,当SW[0]为高电平时,T0~T3将在CLK1的输入脉冲作用下,周期性地轮流输出正脉冲,机器进入连续运行状态。

SW[2]:清零信号,当SW[2]为高电平时,数据清零。

KEY[0]:手动脉冲以进行指令周期

- 输出端口:

LEDR [7..0]: A和B运算之后的结果输出。

LEDG[0]:进位显示小灯

- 控制端口:

KEY[0]:手动脉冲,按一次进行一个时钟信号,四个时钟信号为一个脉冲周期。

2.3 数据通路

CPU由四节拍脉冲发生器、计数器、指令存储器、指令寄存器器、双端口储存器、运算器以及数据存储器七个模块组成,手动控制时钟信号CLK,四个时钟信号为一个脉冲周期。T0控制计数器PC和指令存储器ROM,PC产生的数为指令存储器ROM的地址码,ROM根据地址码取出的数据寄存在指令寄存器IR中。IR将ROM传过来的8位指令进行处理,并将高四位输出给ALU作为操作码,低四位输出分成两部分组成IR[1..0]、IR[1..0]作为地址码传入双端口存储器RAM_2port。双端口存储器根据IR[1..0]、IR[1..0]取出数据A、B。运算器ALU对数据A、B进行运算,最后存入DR寄存器。

2.4 指令系统

3 系统详细设计

3.1 四节拍脉冲发生器

3.1.1 设计

原理:四节拍脉冲发生器由4个D触发器和一个或非门串联组成,这些触发器通过逻辑控制实现特定的时序输出。D触发器由一个共同的时钟信号clk驱动,该信号控制触发器状态的更新。在每个时钟周期,当前的触发器状态会传递到下一个触发器,从而在每个触发器的输出端产生一个的脉冲序列。rst控制脉冲发生器的启动、停止和复位。当rst为高电平时,T1~T4将在CLK1的输入脉冲作用下,周期性地轮流输出正脉冲,机器进入连续运行状态。

功能:在CPU设计中,四节拍脉冲发生器可以用于控制指令的取指、译码、执行等阶段,确保CPU能够按照正确的时序执行指令。

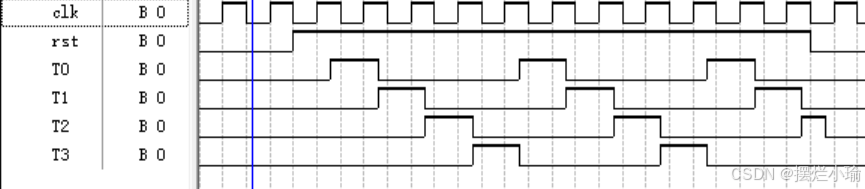

3.1.2 仿真结果

如下图,当rst为低电平时,T0~T3恒为低电平;当rst为高电平时,T0~T3将在clk的输入脉冲作用下,周期性地轮流输出正脉冲,机器进入连续运行状态。

3.2 计数器PC

3.2.1设计

原理:使用lpm_counter宏功能模块设计,8条指令设计一个位宽为4bit的计数器,模值为8,从0000开始,CLK高电平的时候+1并输出到ROM中。

功能:PC输出当前ROM中数据的地址码,PC通过增加指令字节数来实现自动更新,指向下一条指令的地址。遇到跳转指令时,PC更新为跳转目标地址,允许程序执行流程的非线性变化。PC确保指令按预定顺序执行,是程序控制流程的核心。

3.2.2仿真结果

仿真结果如下图所示,来一个时钟信号PC计数器自动+1。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2567

2567