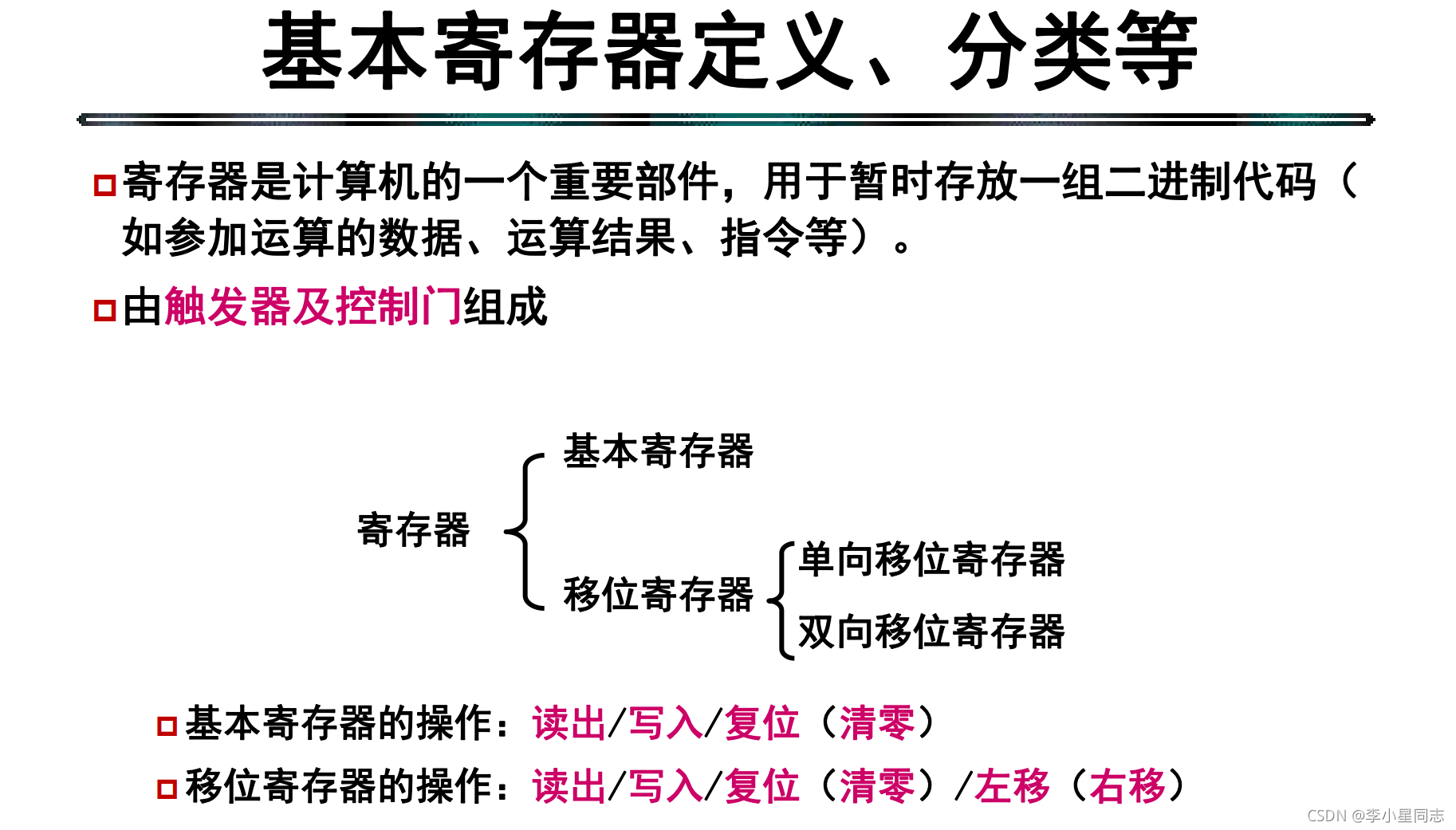

寄存器是什么?:

先讲讲基本寄存器:

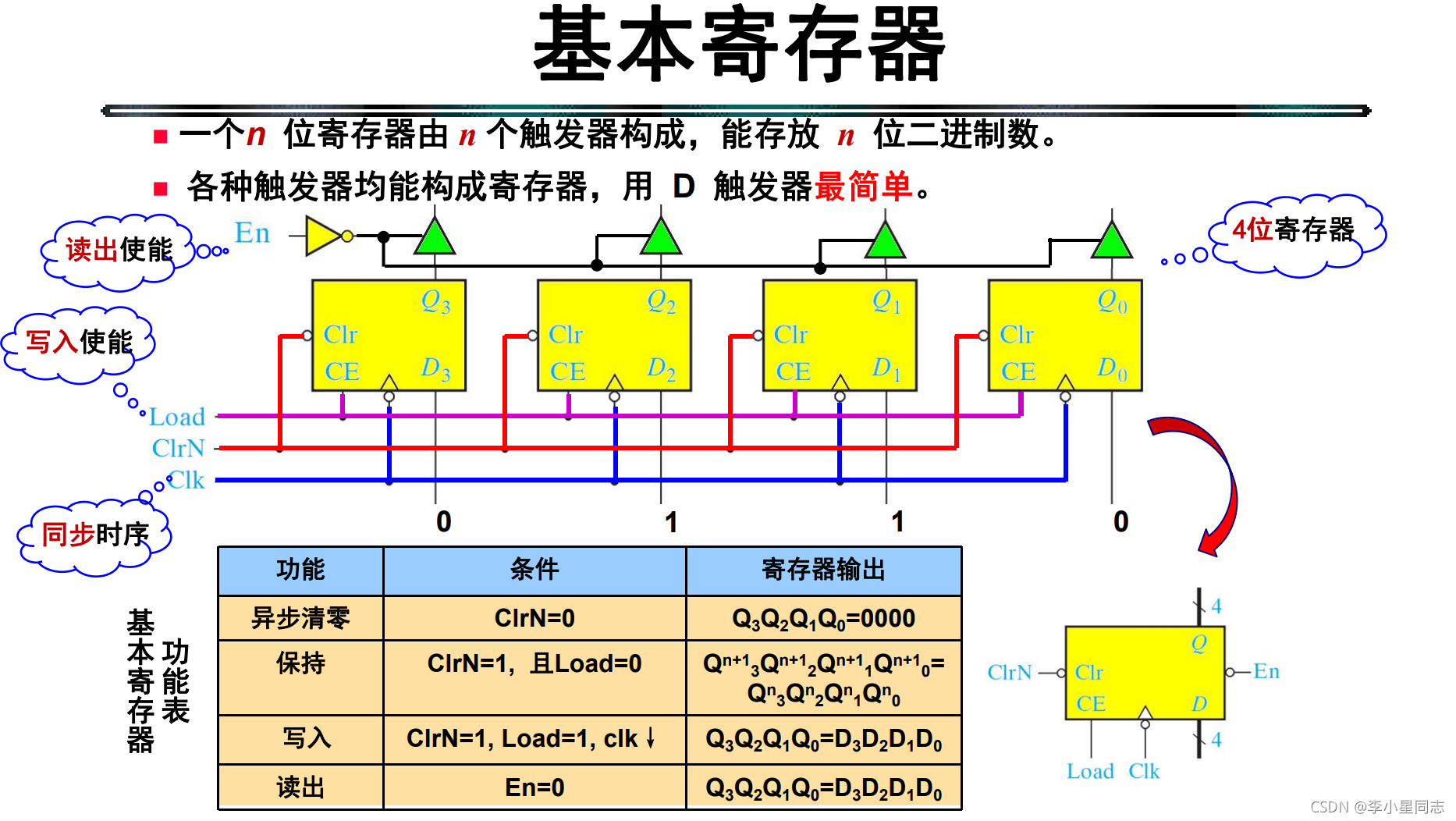

不出所料,寄存器是用触发器做出来的,拿其中的一个输出当存储就可以了。这里使用了带有带有异步清0端的D.(CLRN就是清零的。注意到那个非了吗?低电平有效)

Clrn=0,当然是清零了。记住了,异步的输入端是不用看clk和ce的脸色的,想清零就清零。想要保持的话,就不能清零(Clrn=1),还不能受外界干扰,Lord(也就是CE)还得是0,把触发器锁住不许你改。想要改的话,CE=1(也就是Lord),ClrN=1(别给我清零了)加上时钟就可以了。En是控制最上面的三态器件的,也就控制了读取。

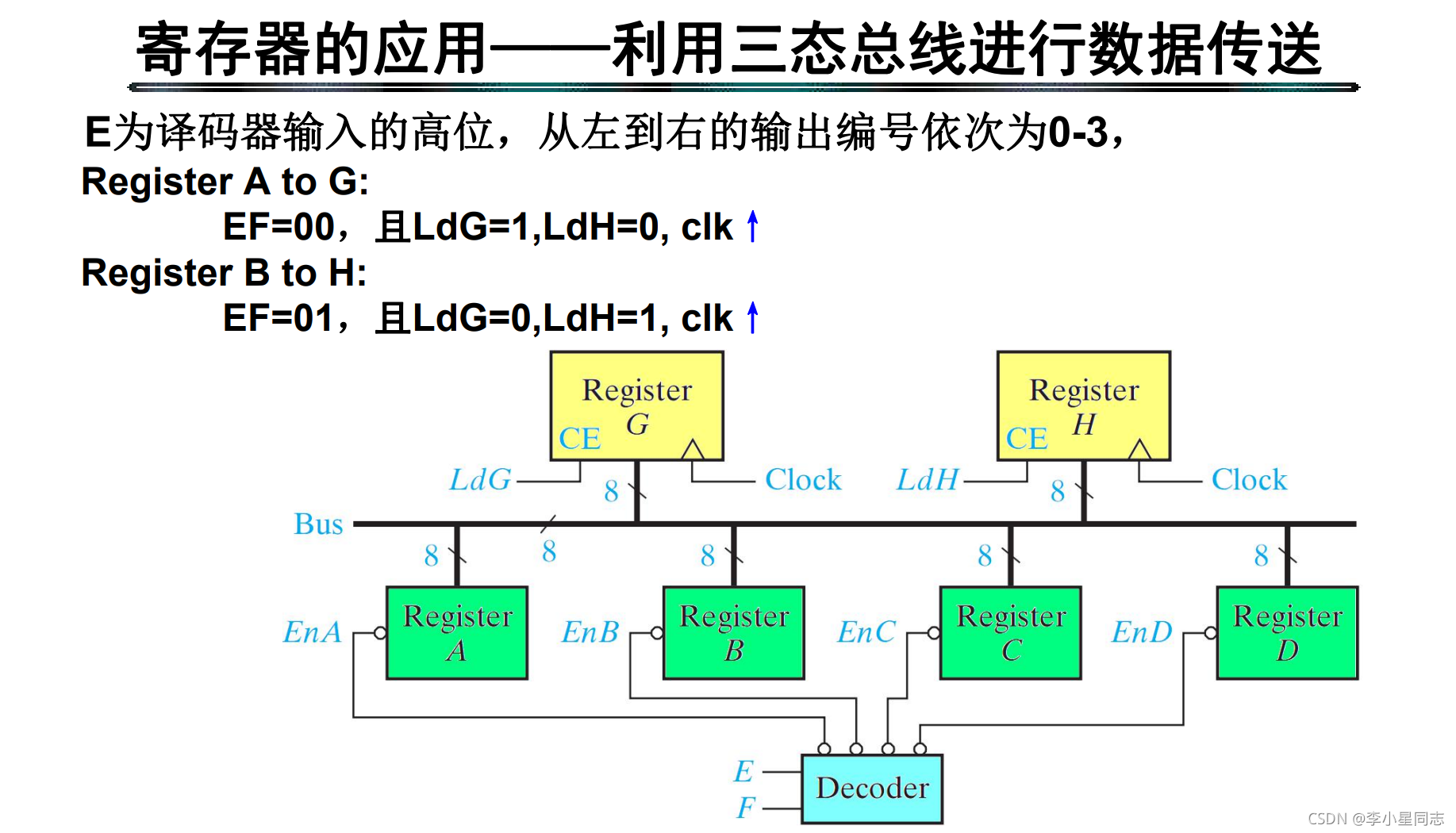

可以看到,就是用EF控制使用ABCD中的哪一个寄存器,读出数据传给上面,用LdG,LdH控制要不要接受。

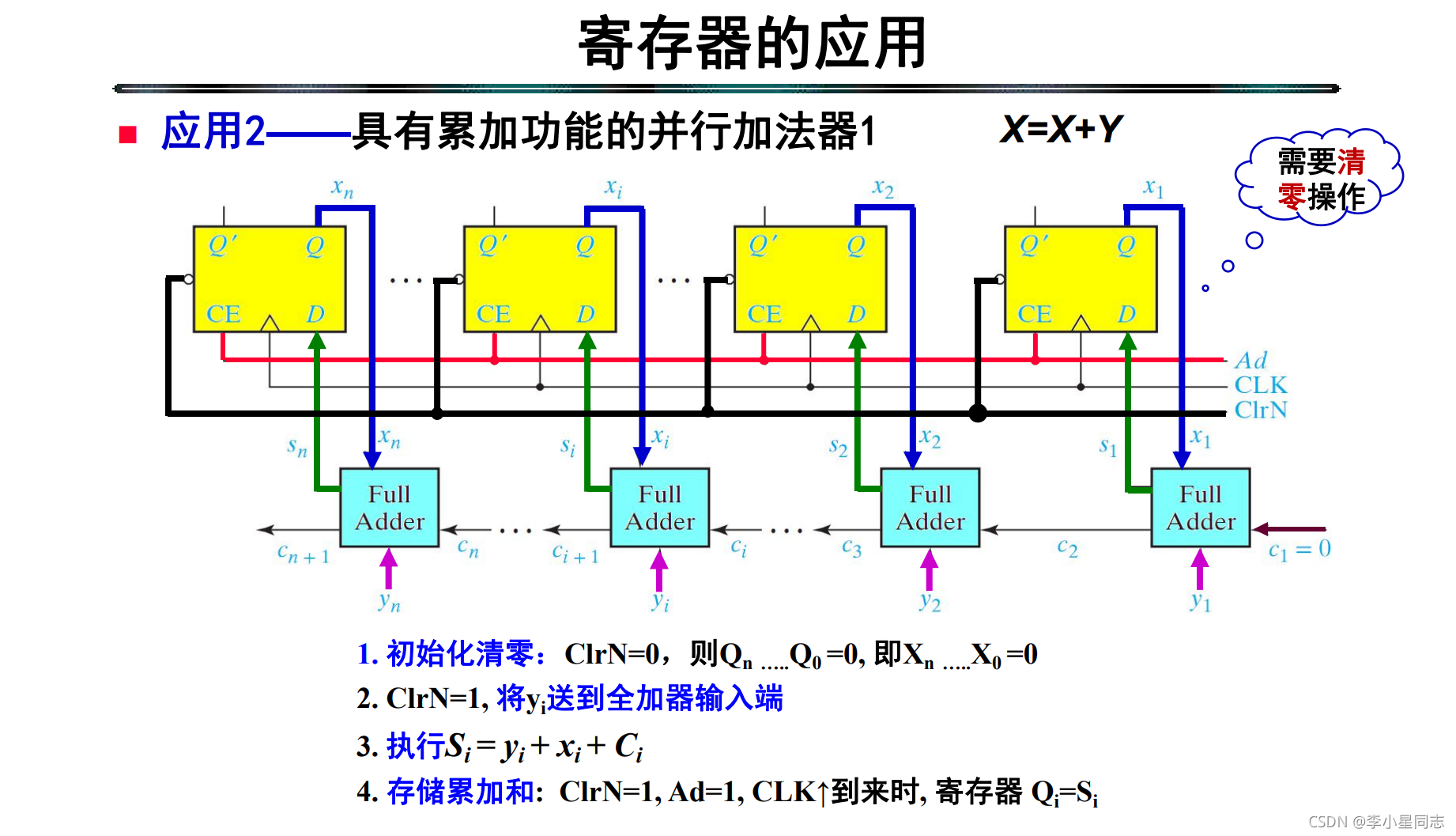

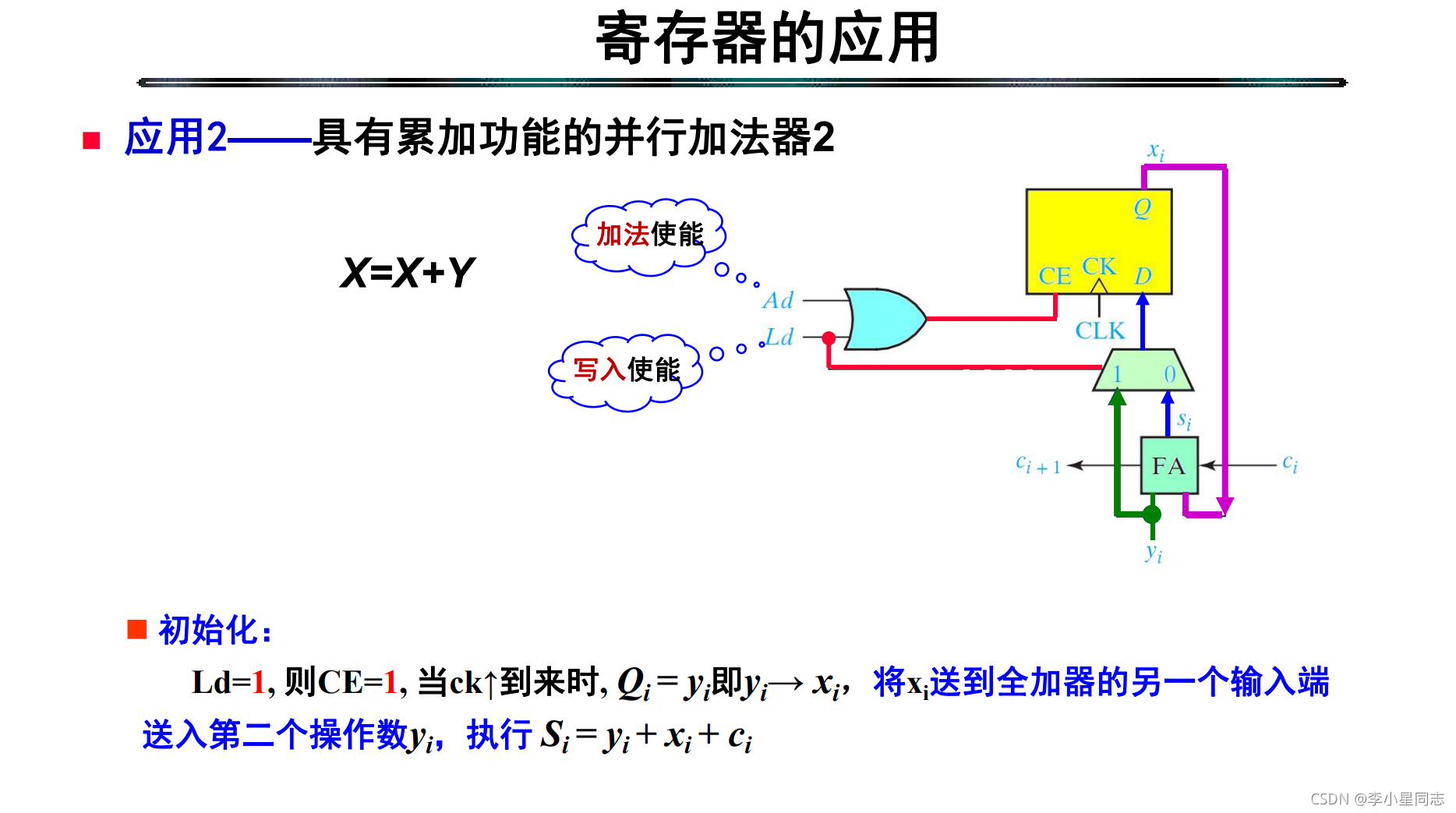

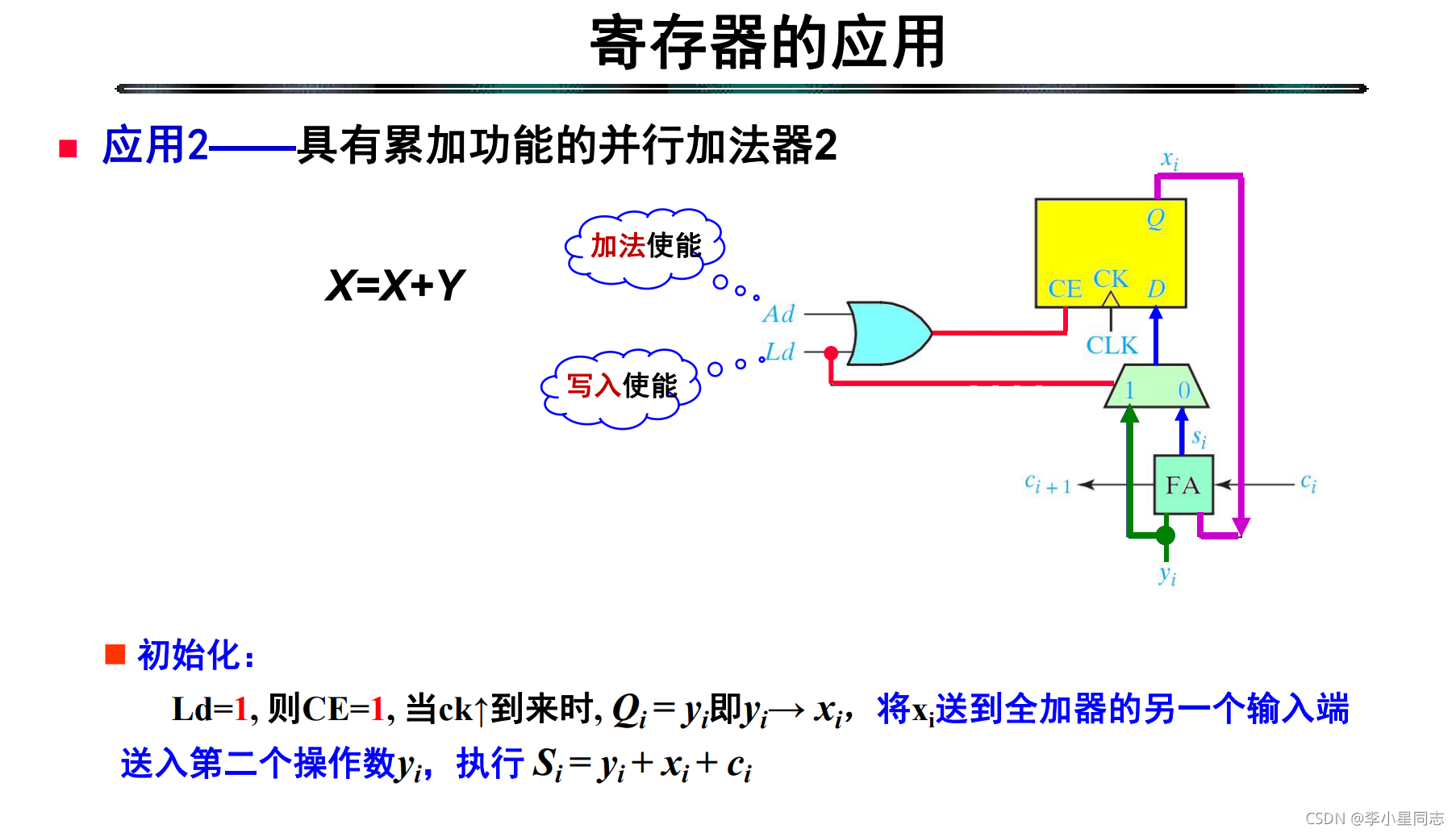

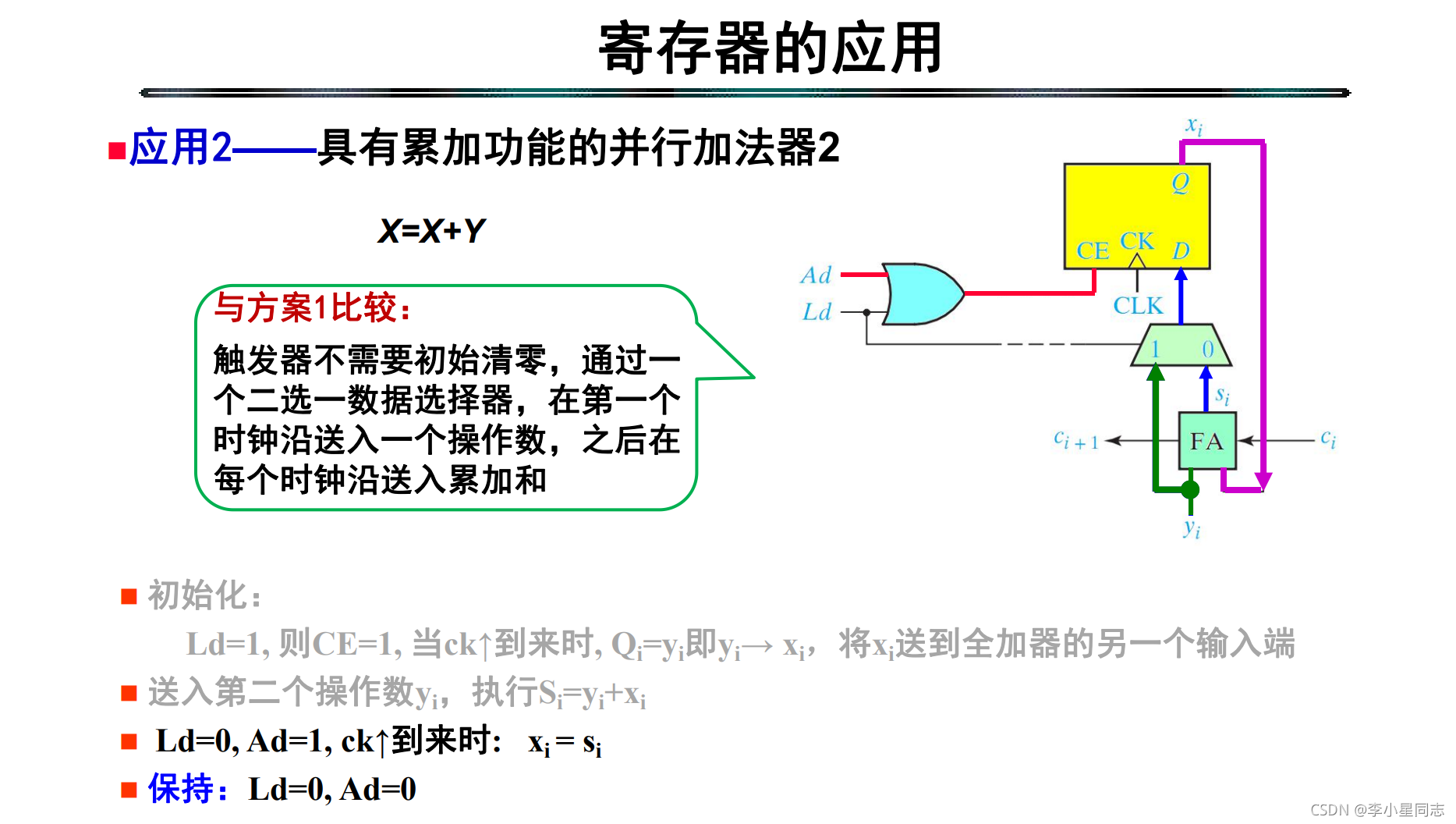

一开始的时候X都是0,加上Y就是Y自己,结果送到D那,变成了Q,也就是X回来,又和Y加,结果又回到Q···只要CLK来一回就加一会。

并行加法器需要一个叫超前进位的玄学东西,还不太懂。印象中那个很简单的结构是比较大小的。

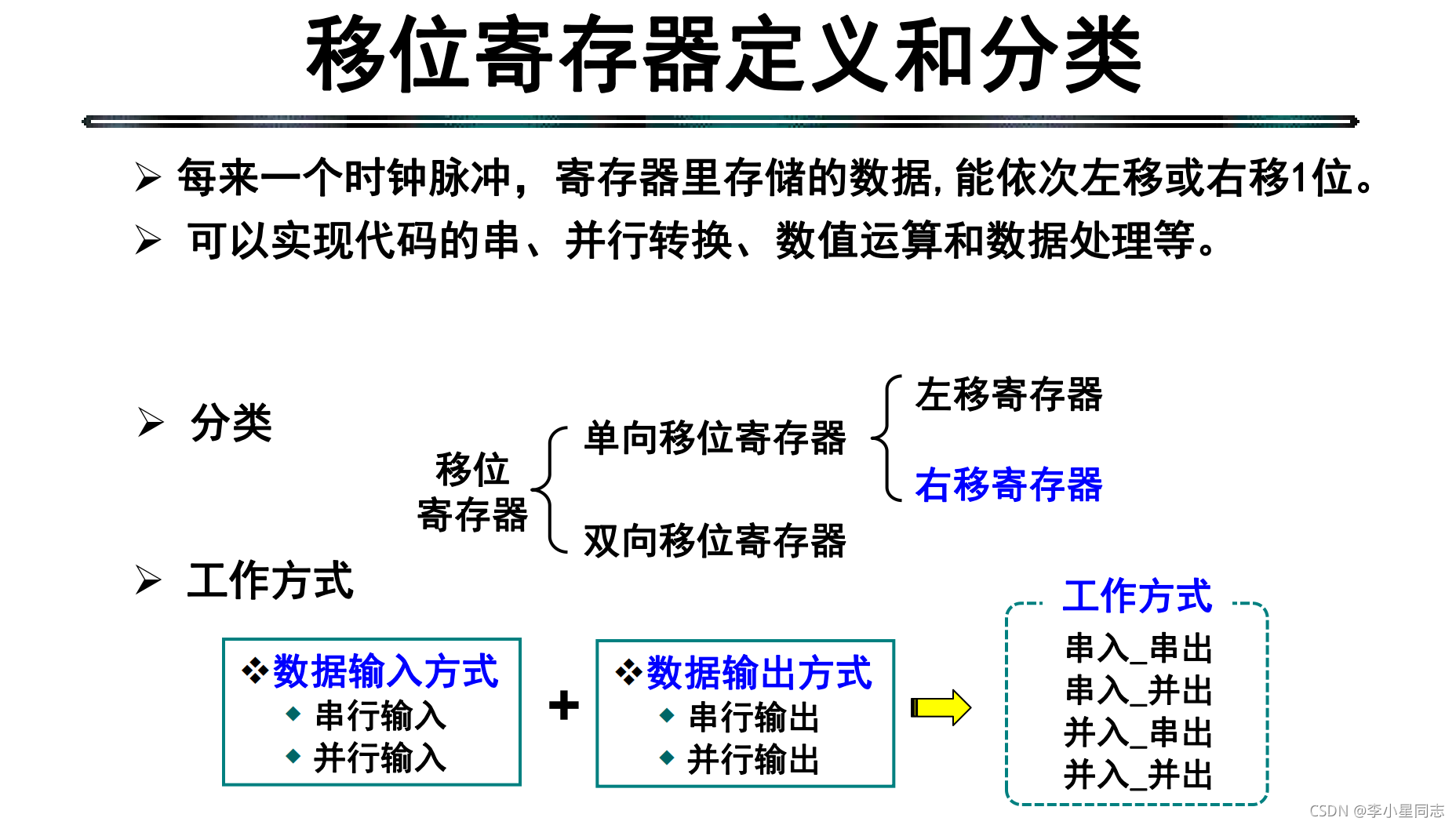

接下来讲移位寄存器:

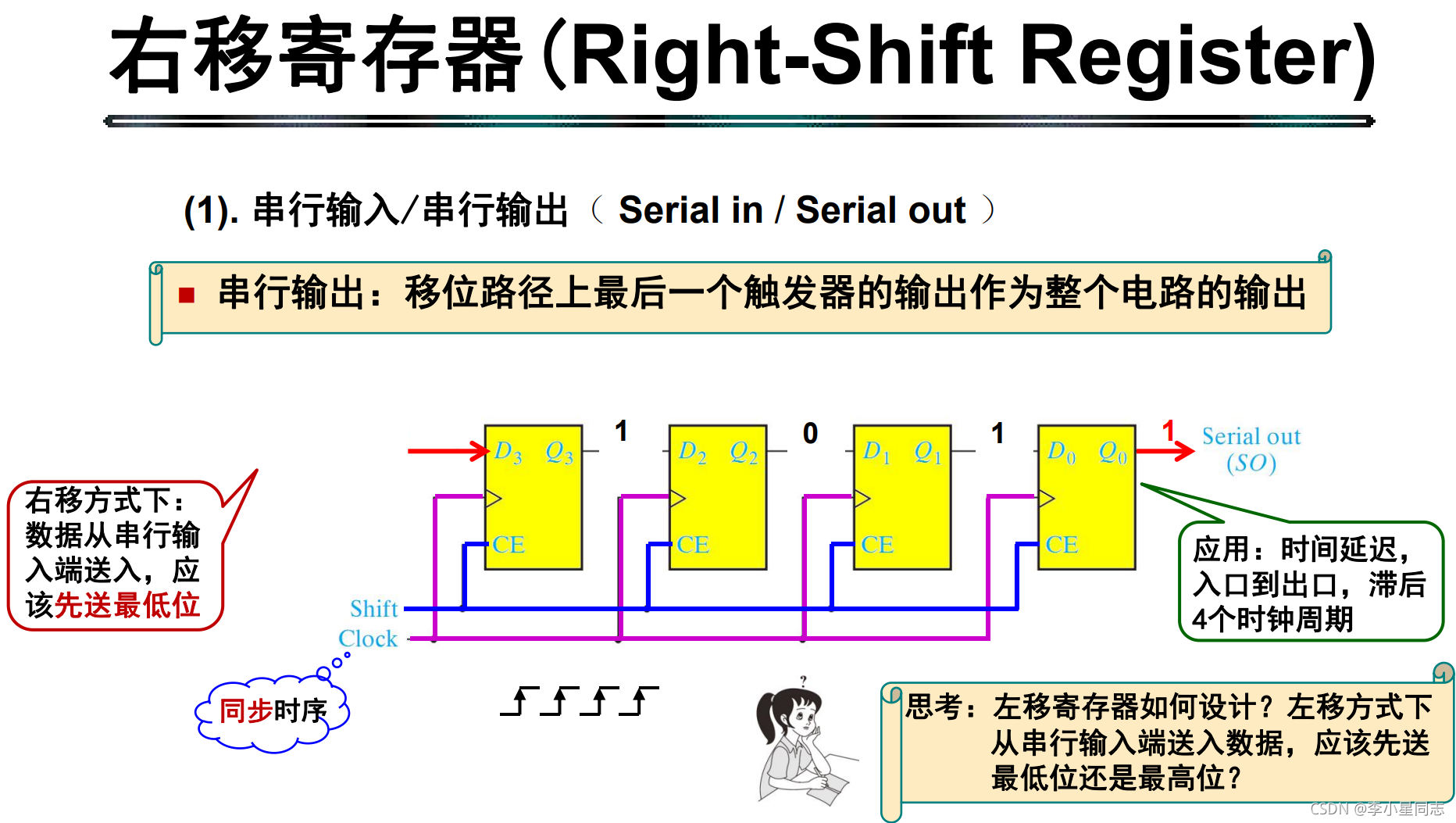

这个的用处只是加延迟。

这个的用处只是加延迟。

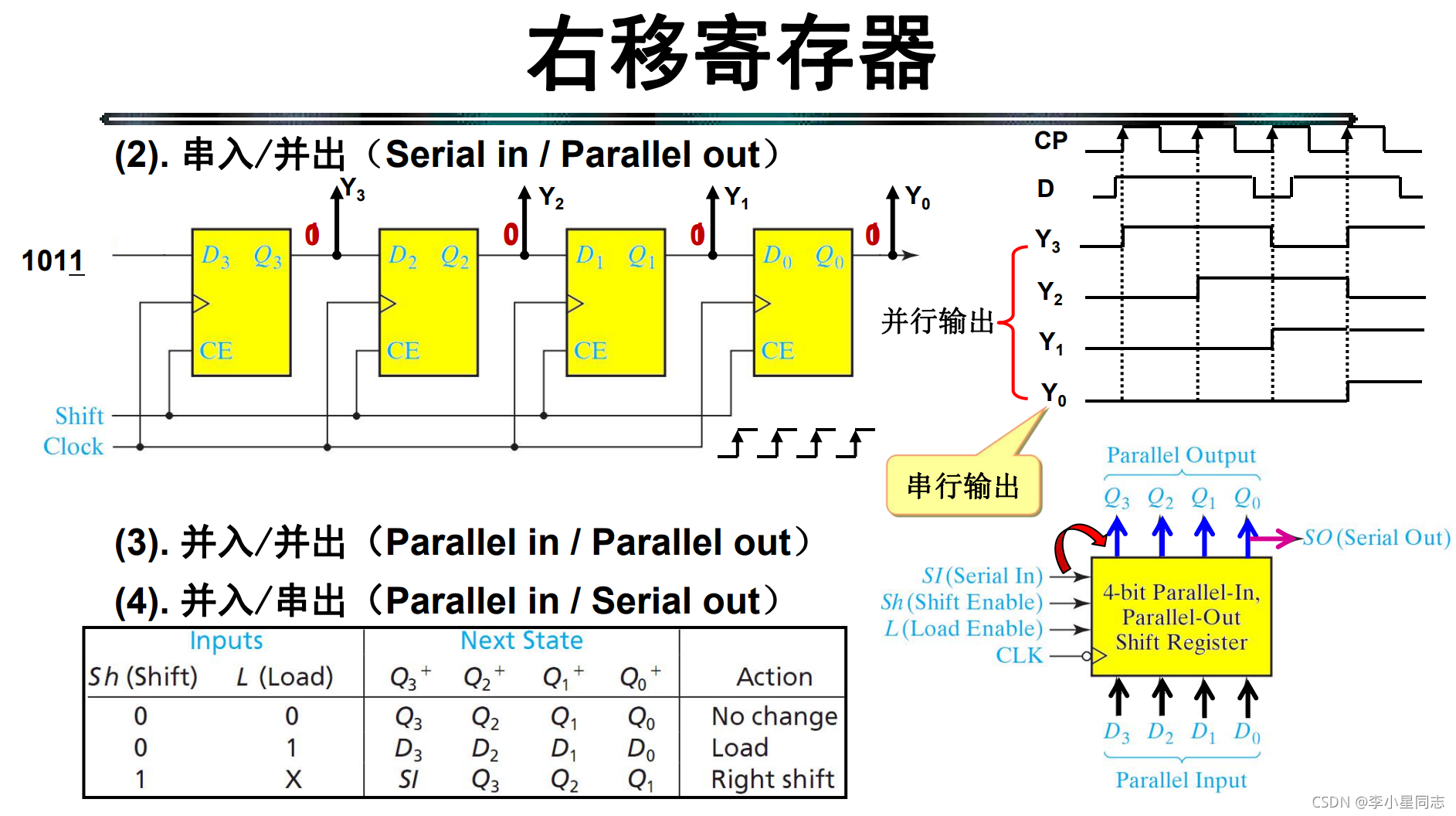

每个都能输出,每位都有延迟,这下就有“向右移”的效果了。

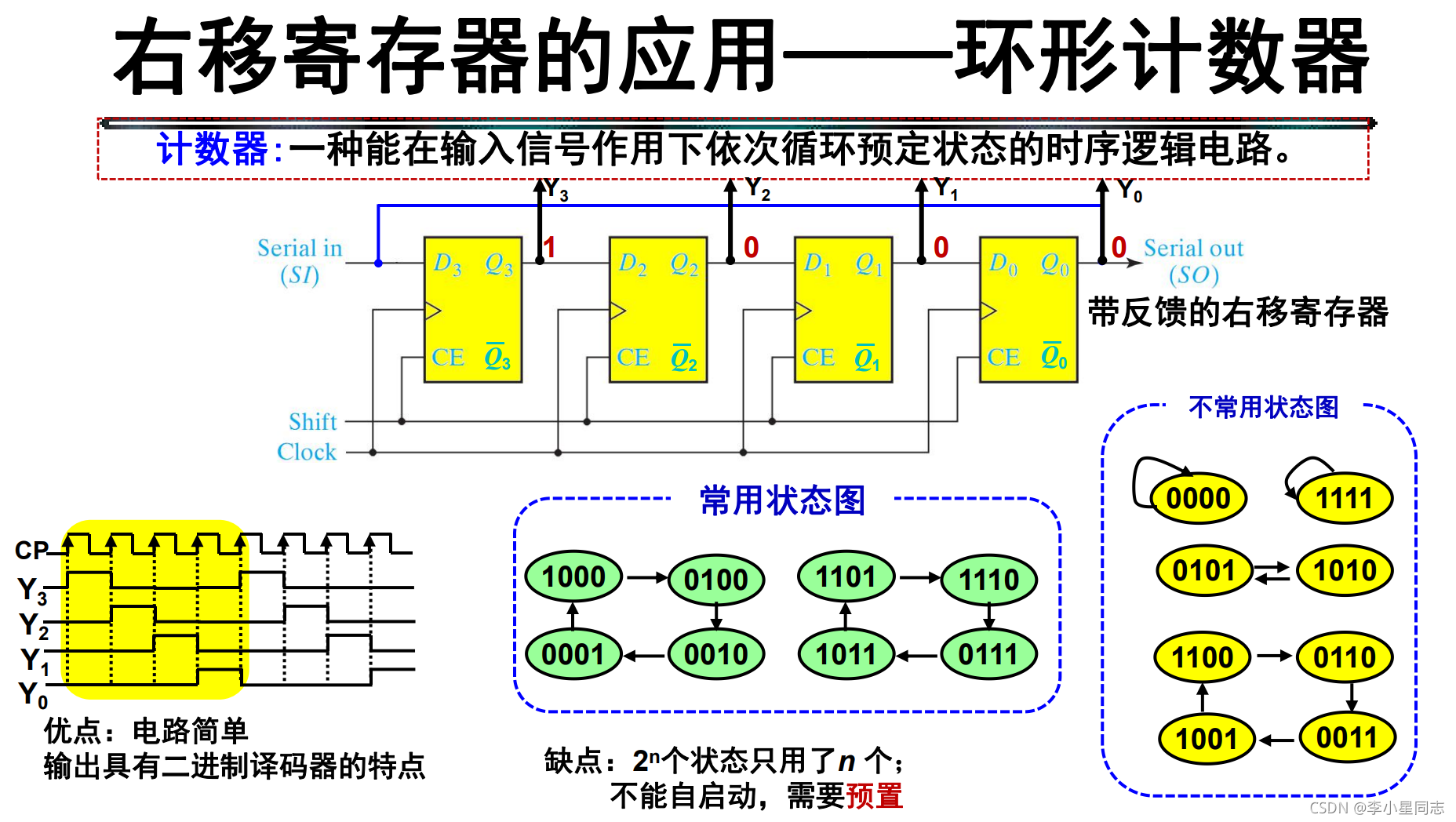

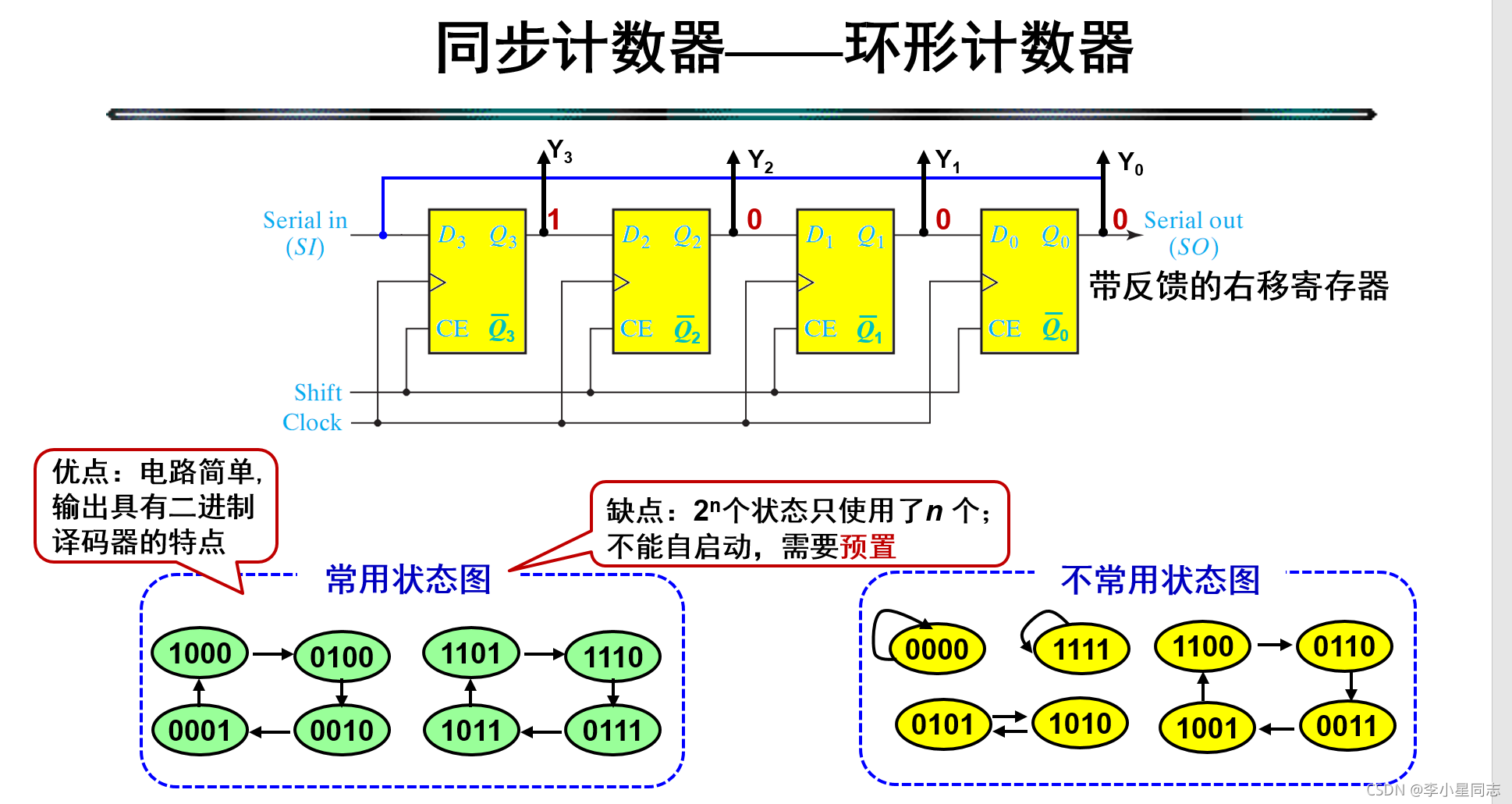

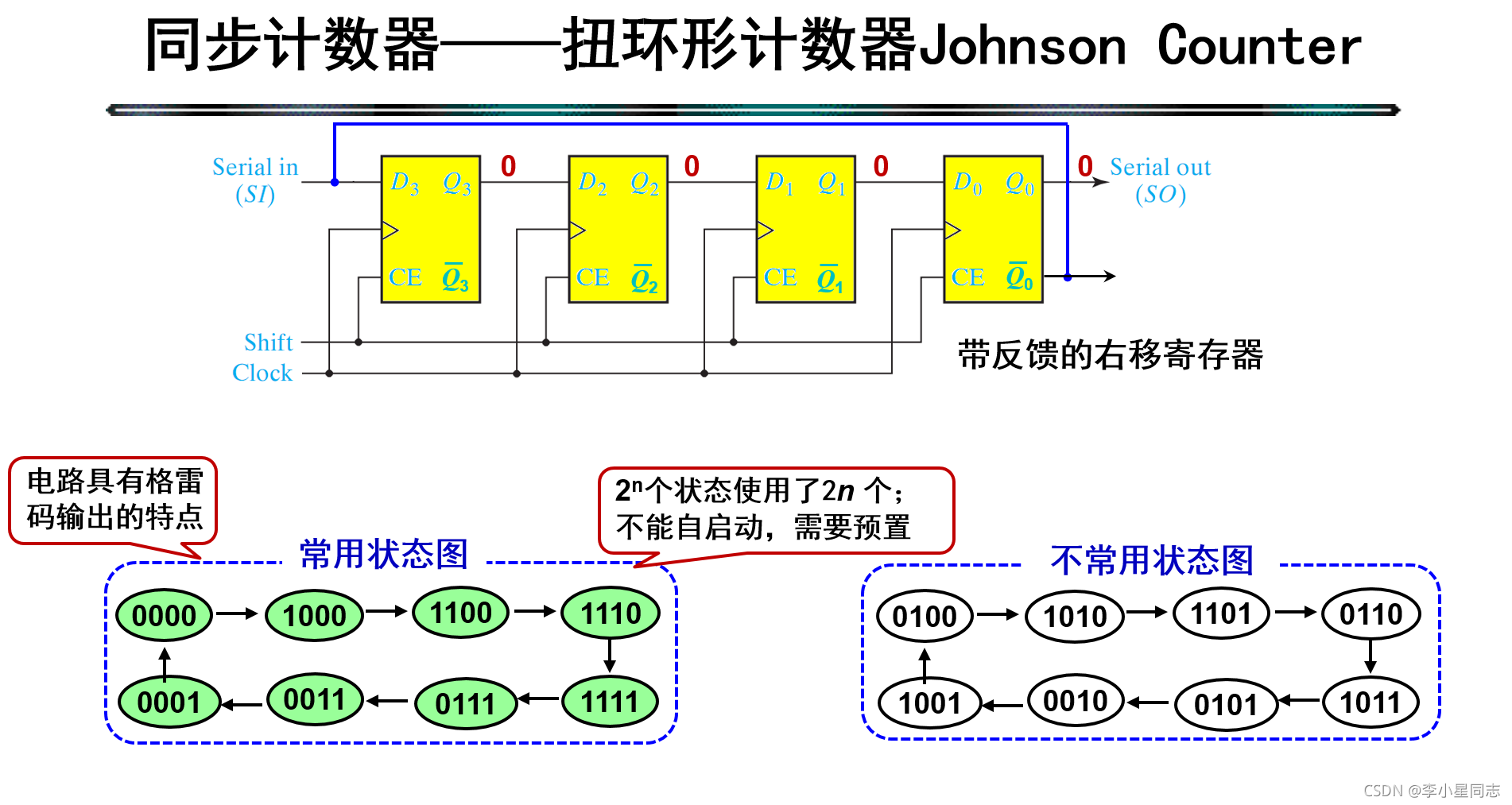

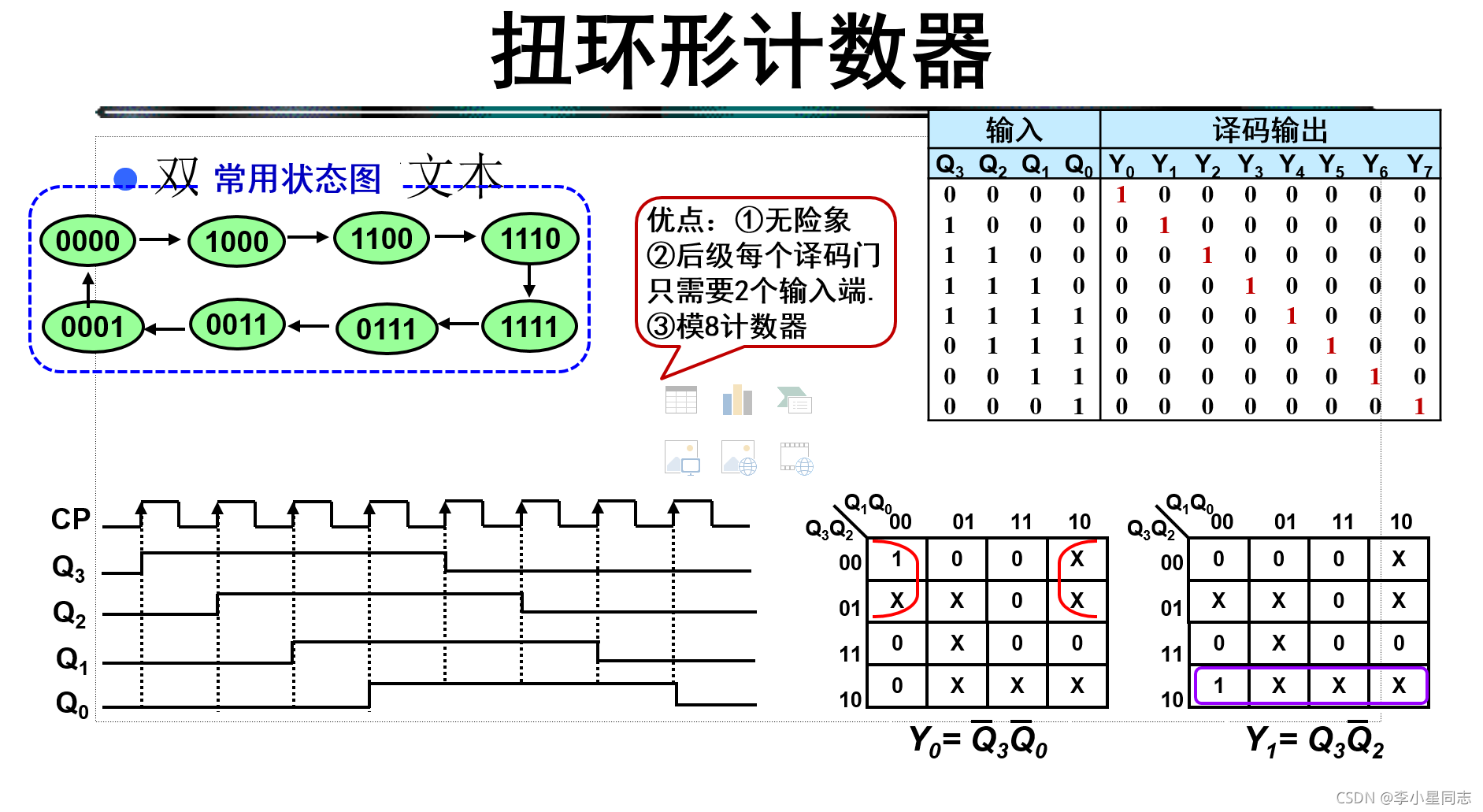

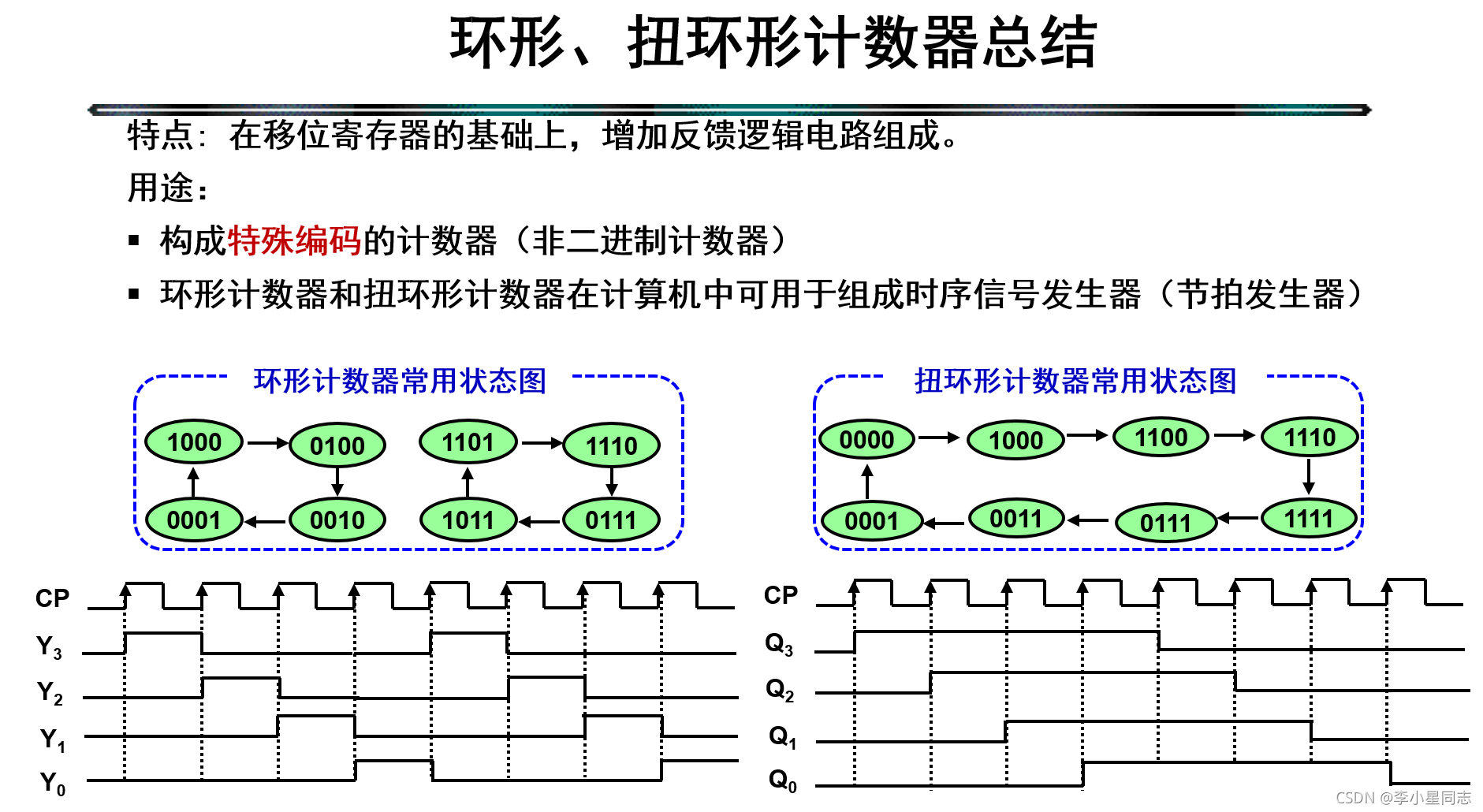

这下就可以转转转了,不过有点浪费状态,还需要预制。

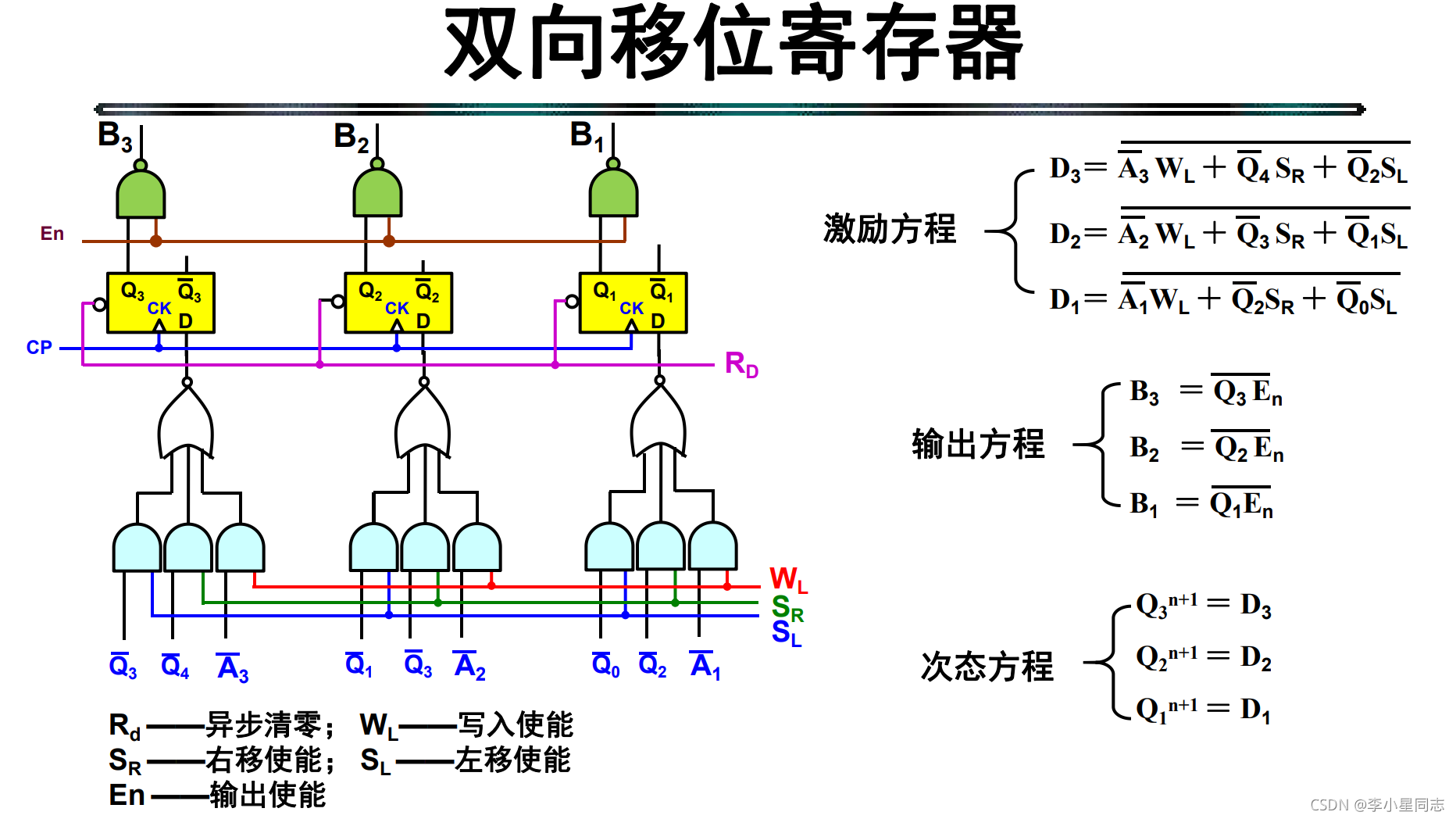

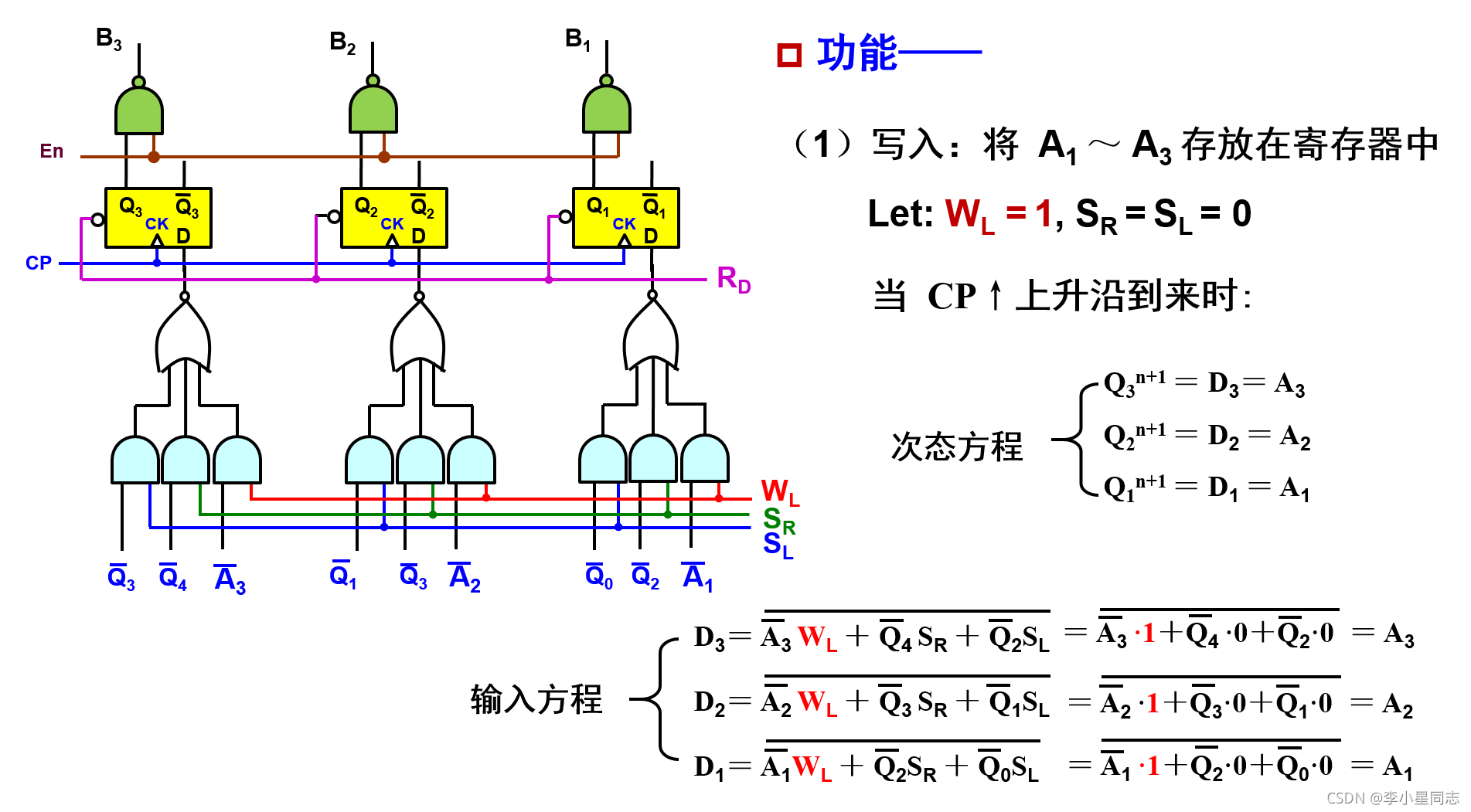

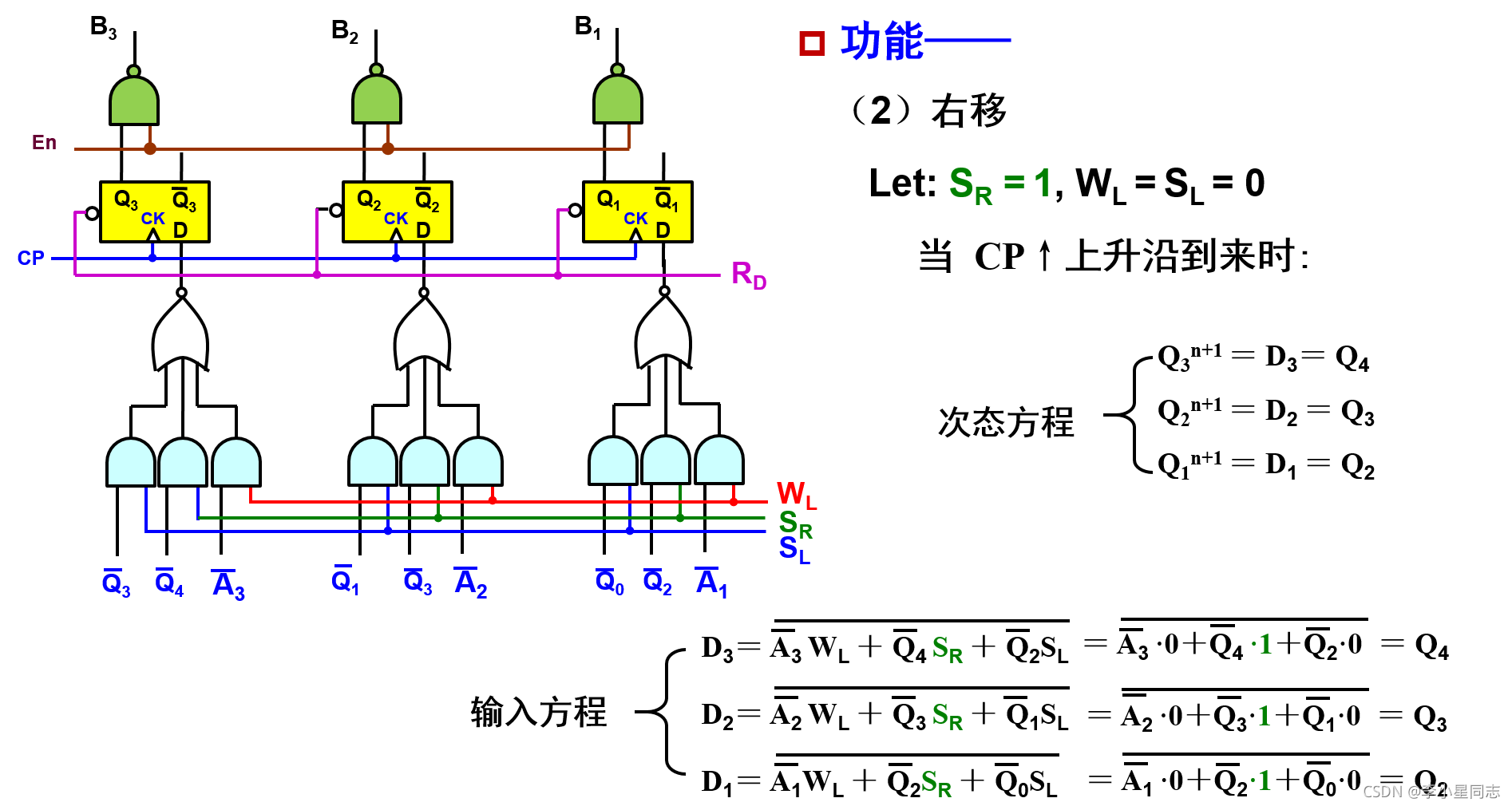

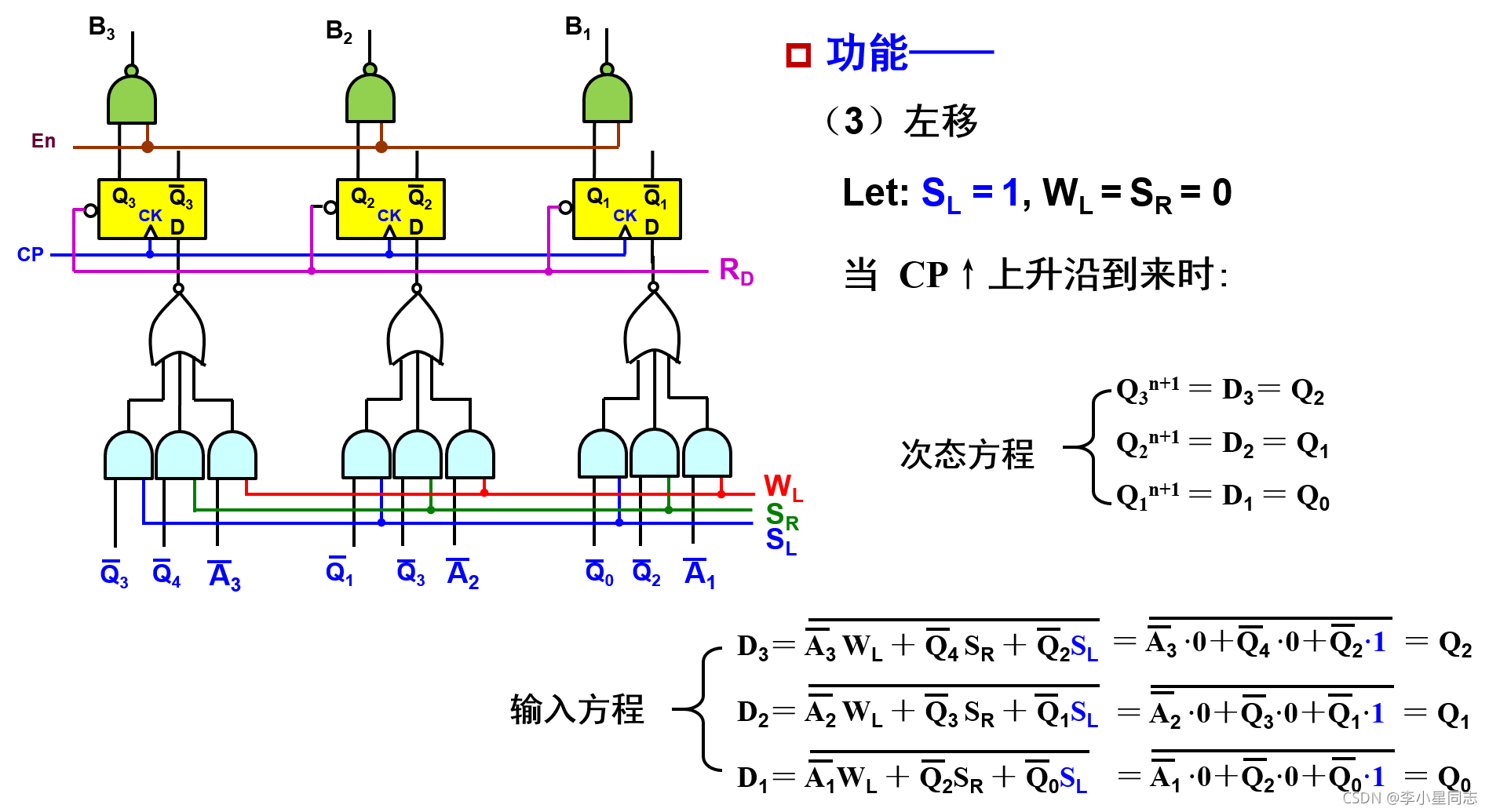

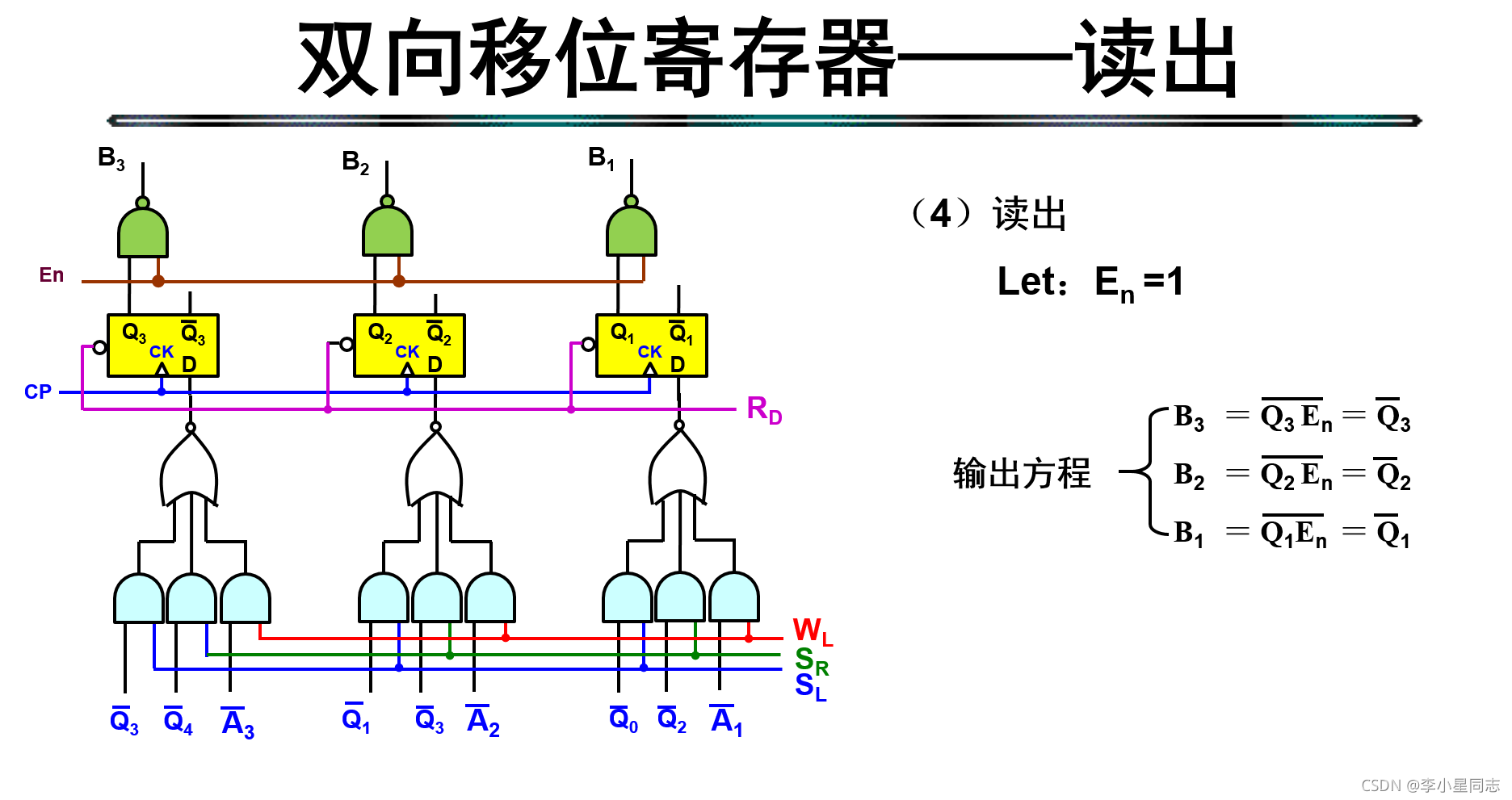

现在介绍可以双向移位的:

这个功能的实现非常复杂,可以通过算逻辑式来判断:

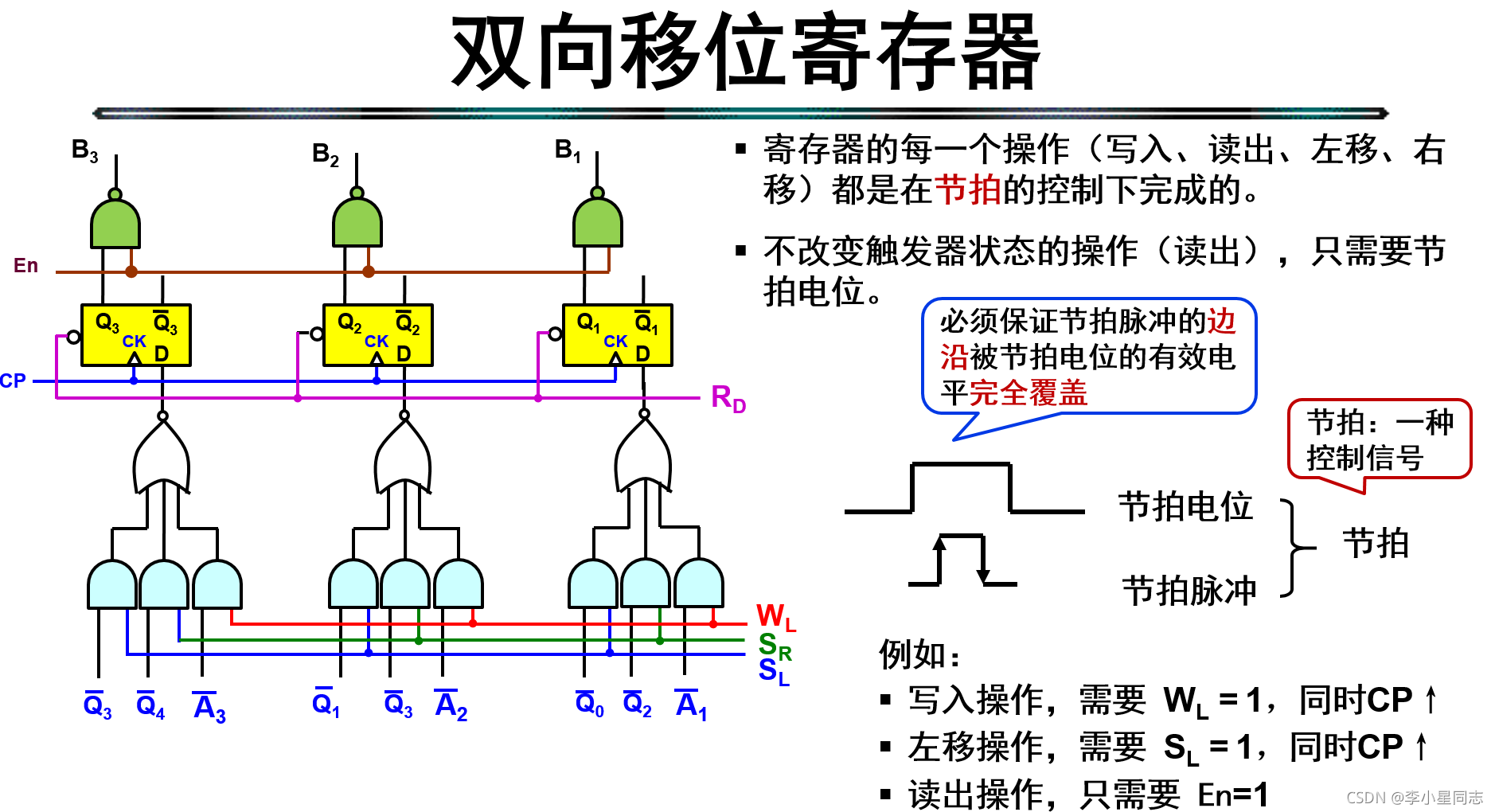

这里要注意一下,上面一直没提CLK是因为他到处都是:

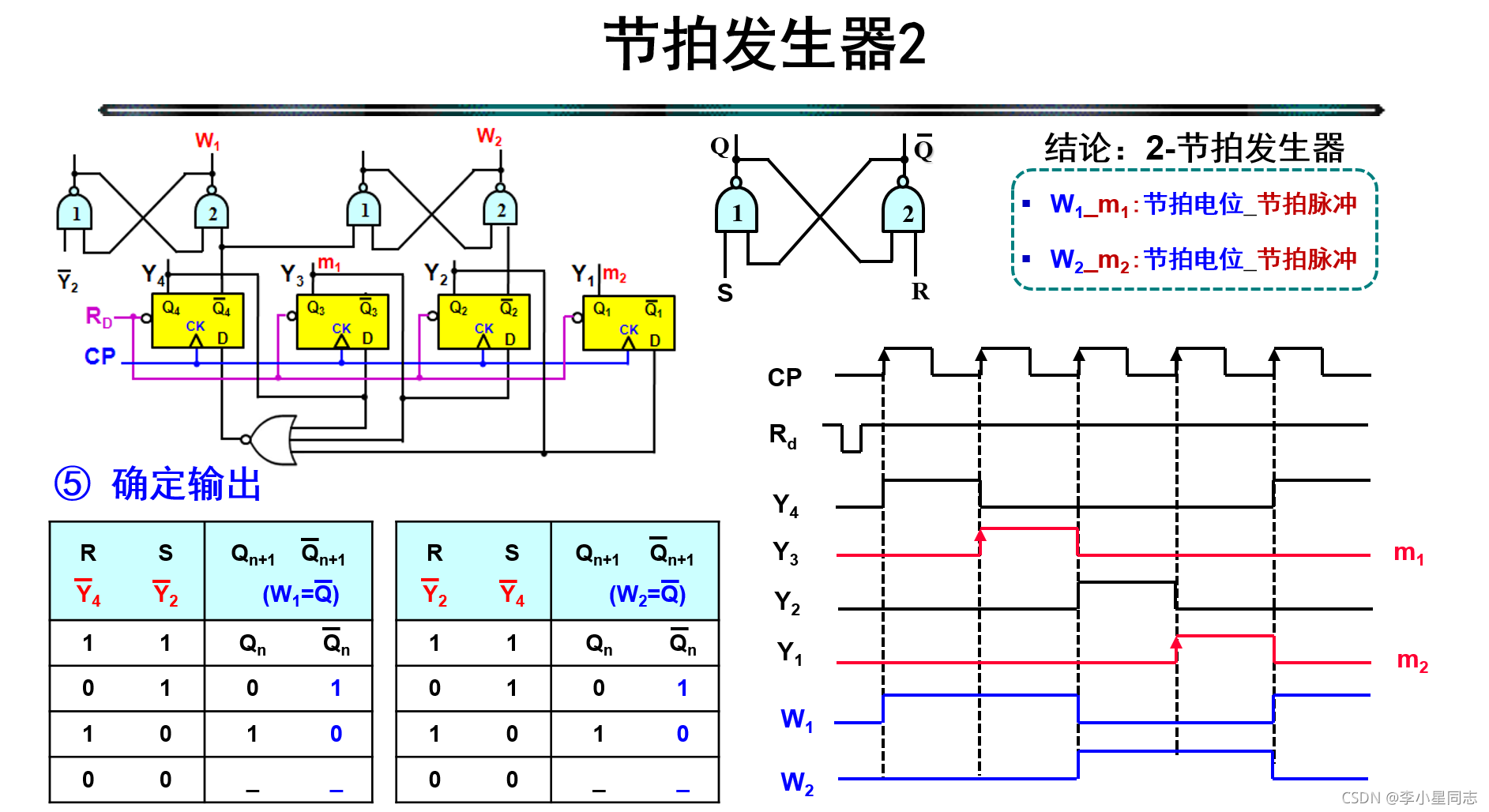

节拍的脉冲要比一个CLK要大,否则可能会输不进去,错过时机。

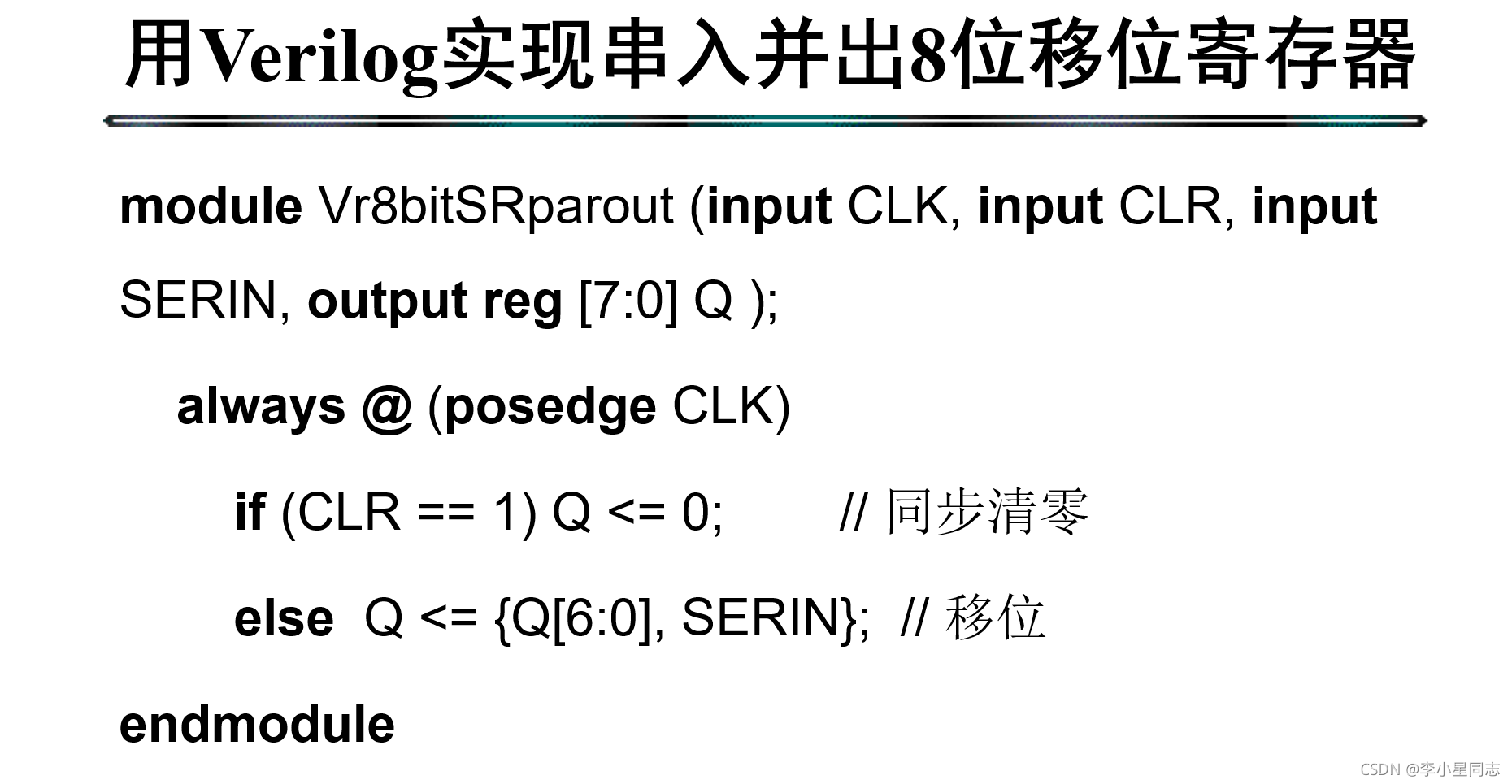

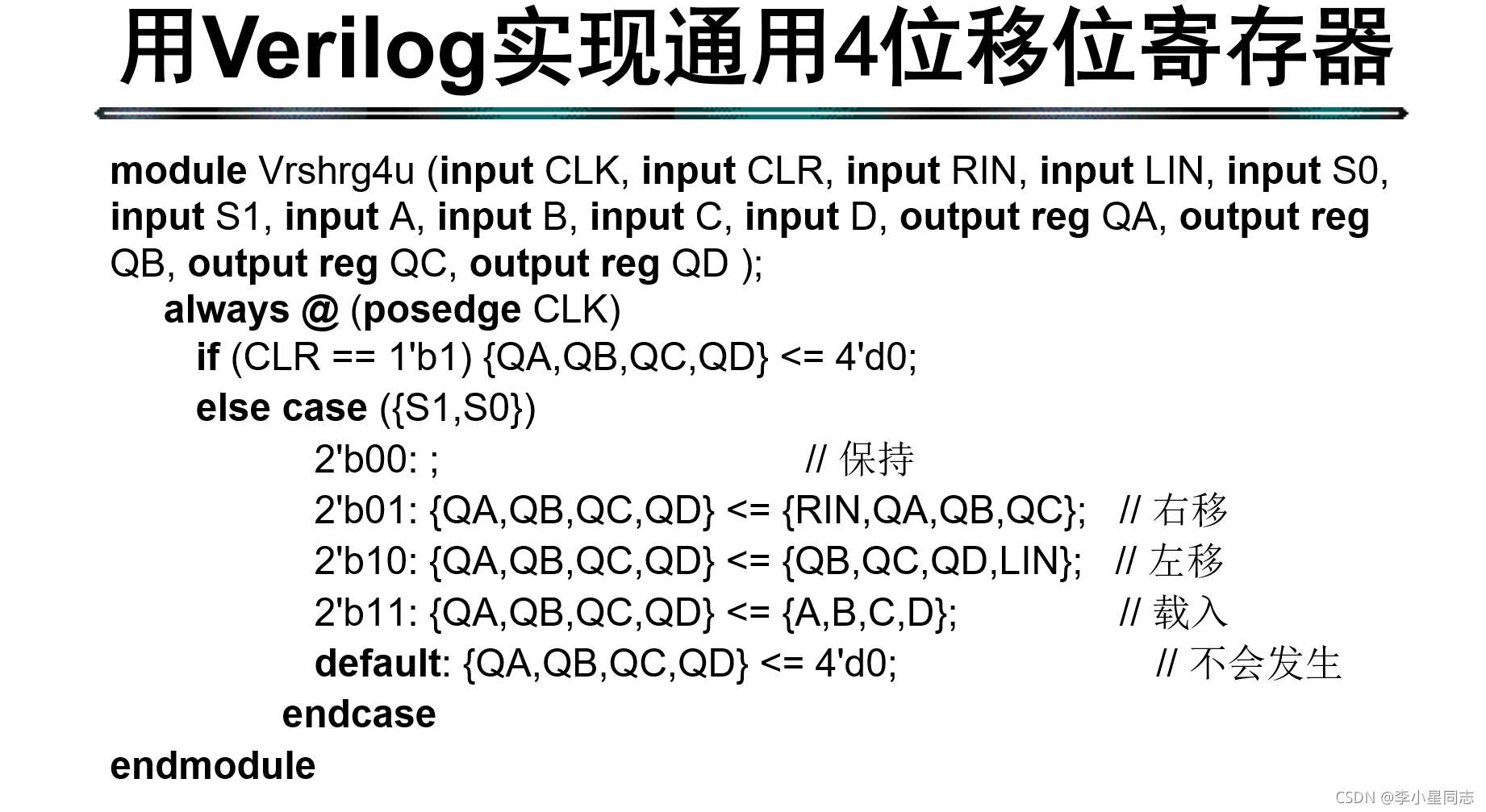

用verilog实现的例子,都很简单:

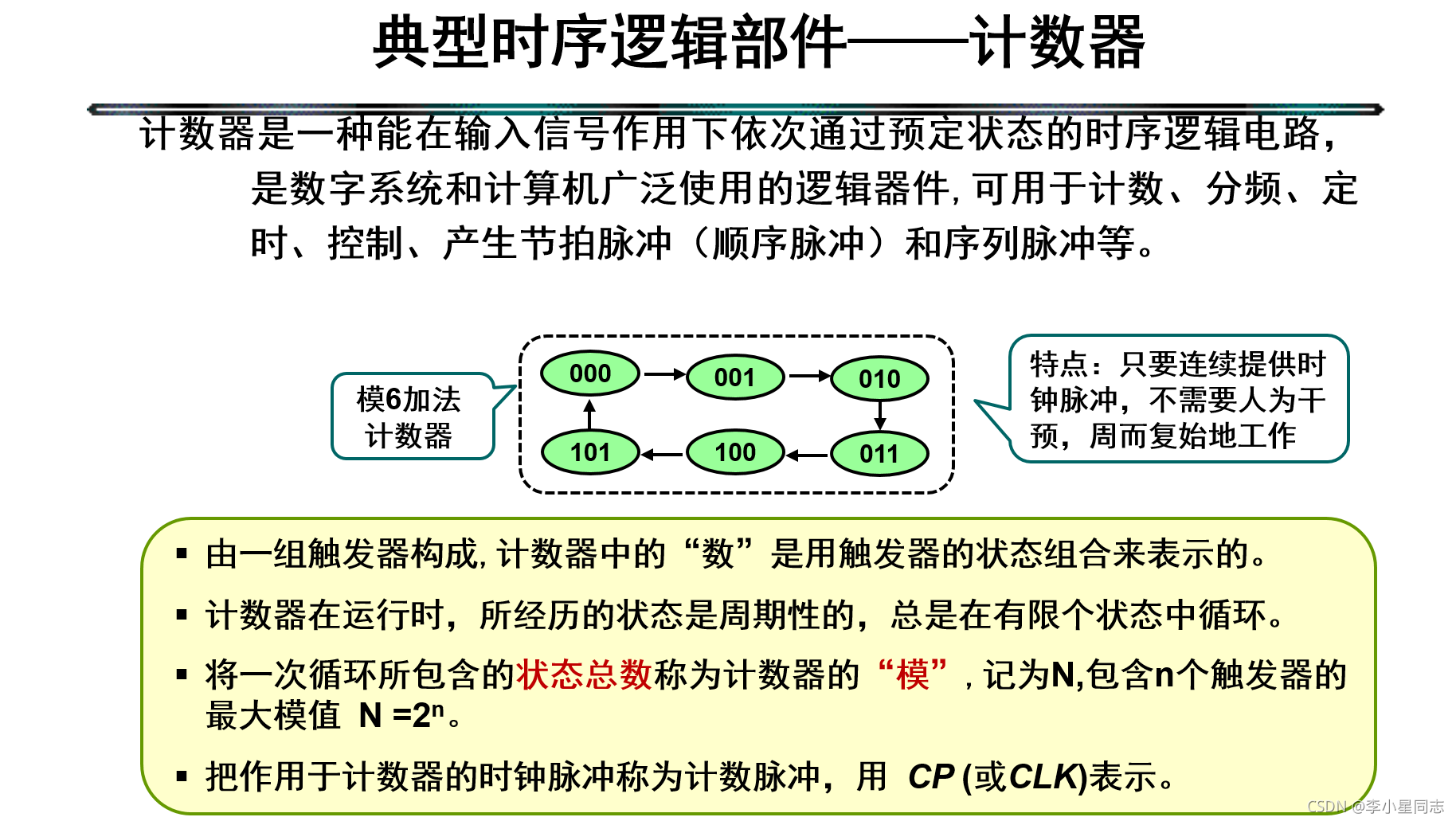

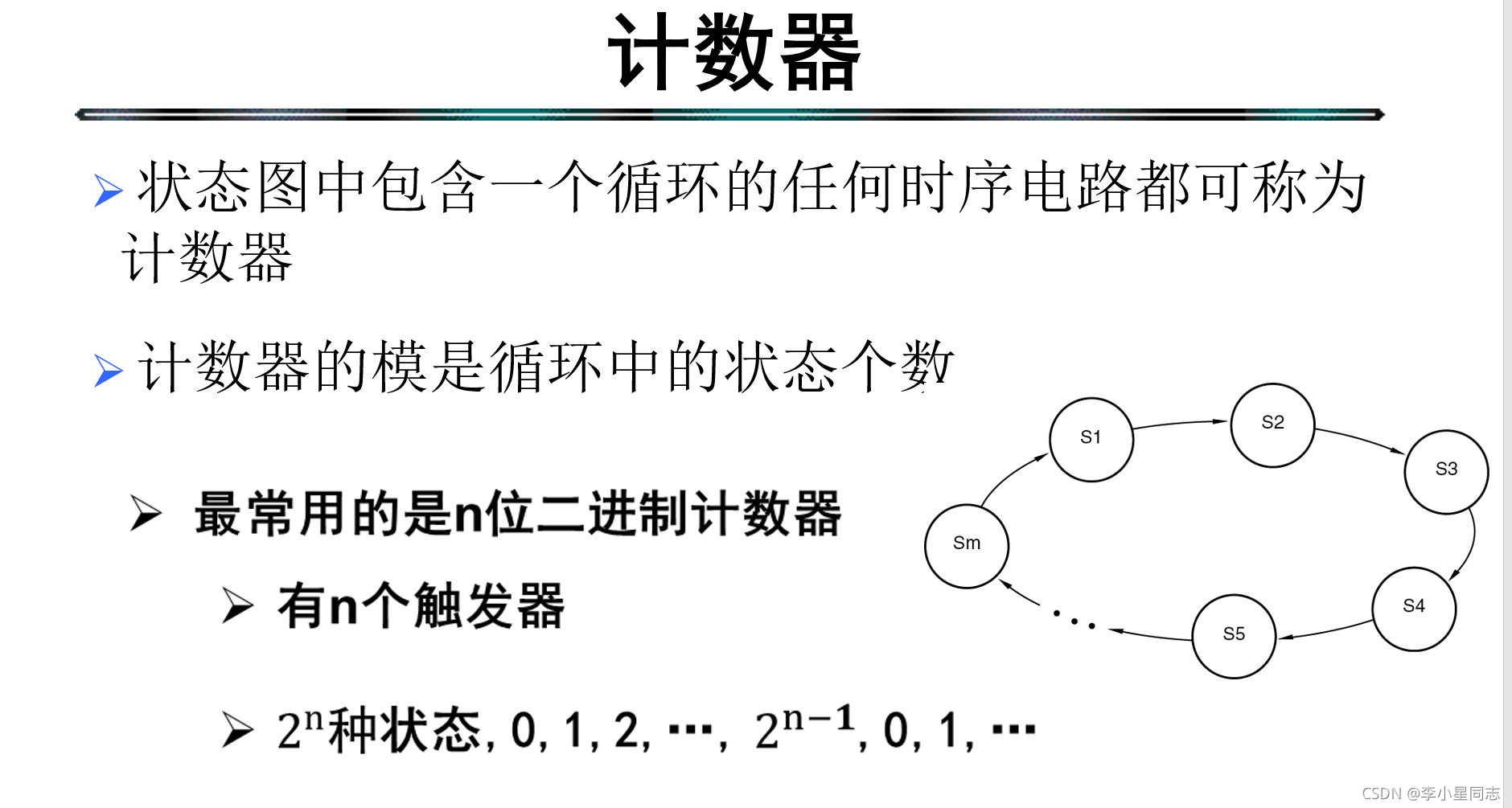

接下来学计数器:

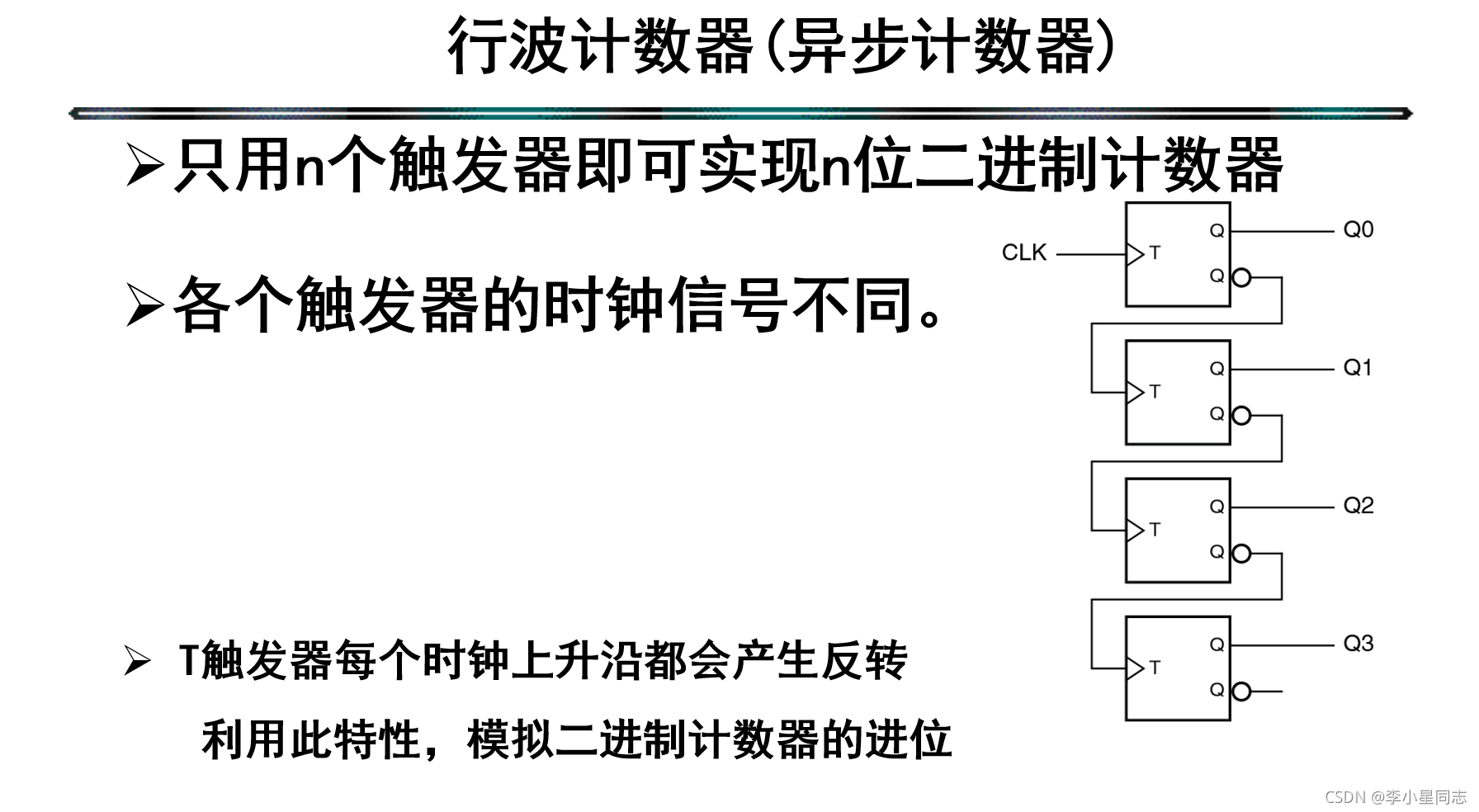

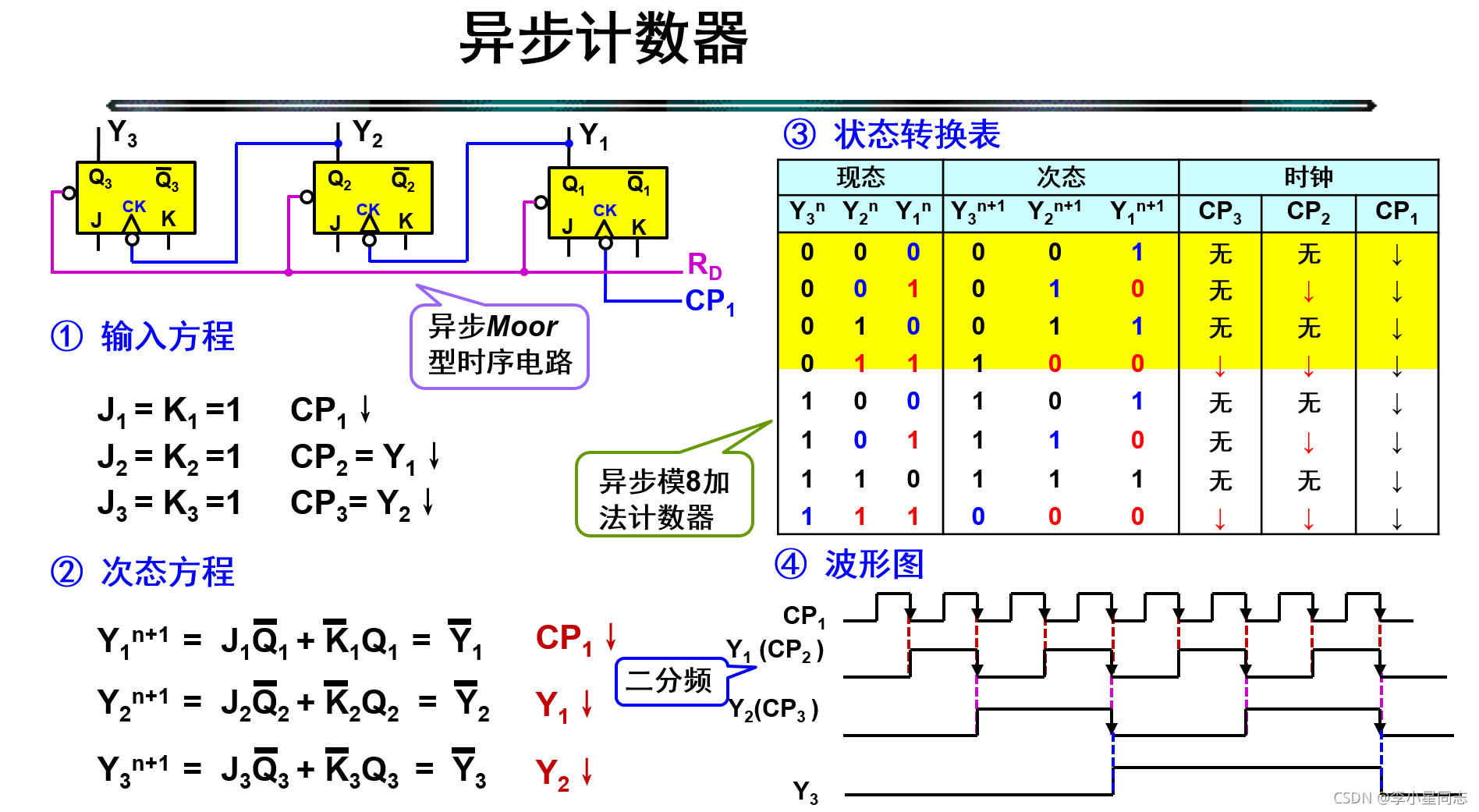

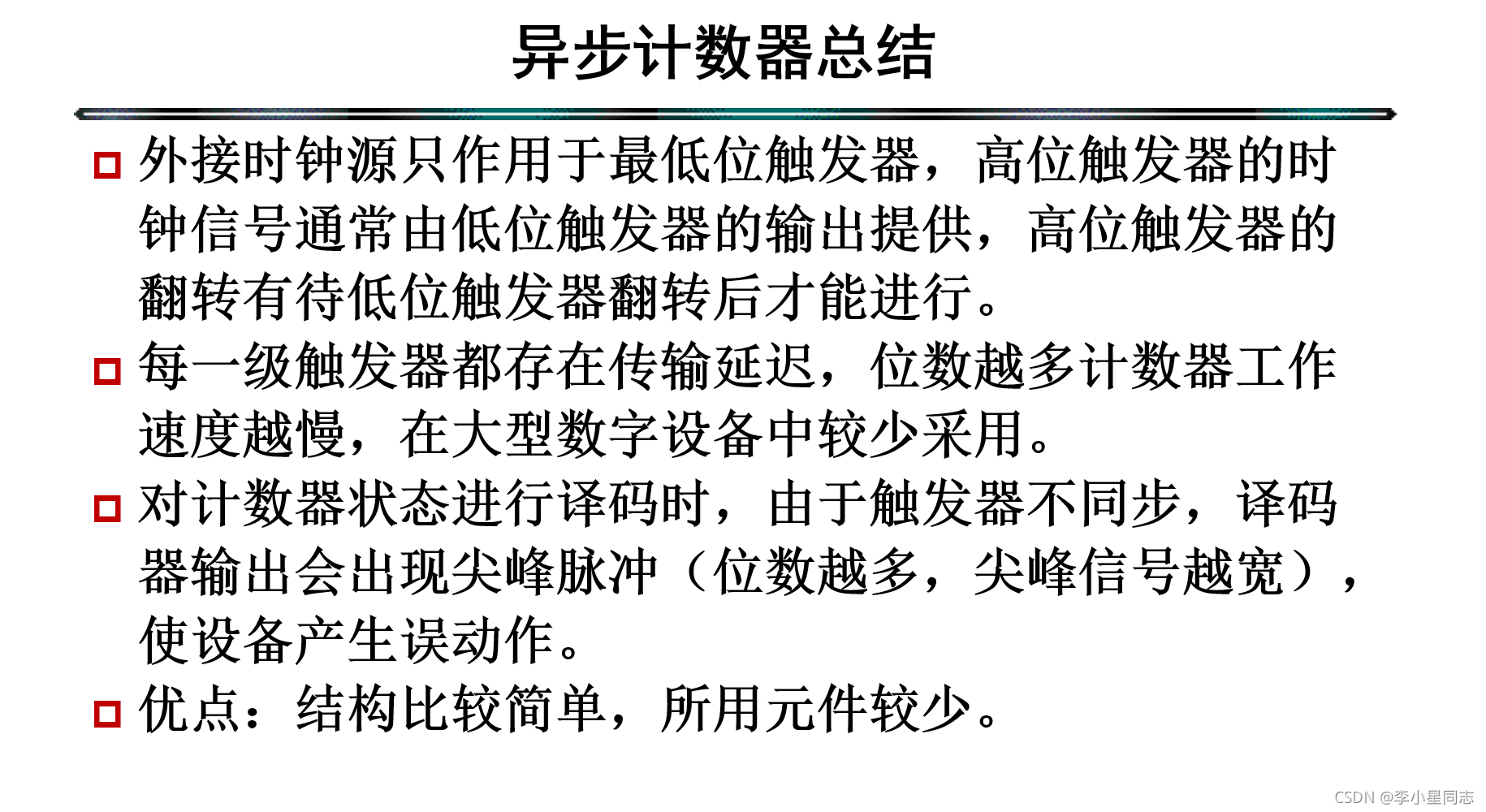

先介绍异步的:

JK始终是1,所以会一直反转,一有机会就反转。可以看到,Q2反转的机会是Q3的两倍,Q1反转的机会又是Q2的两倍,所以会有8种情况。

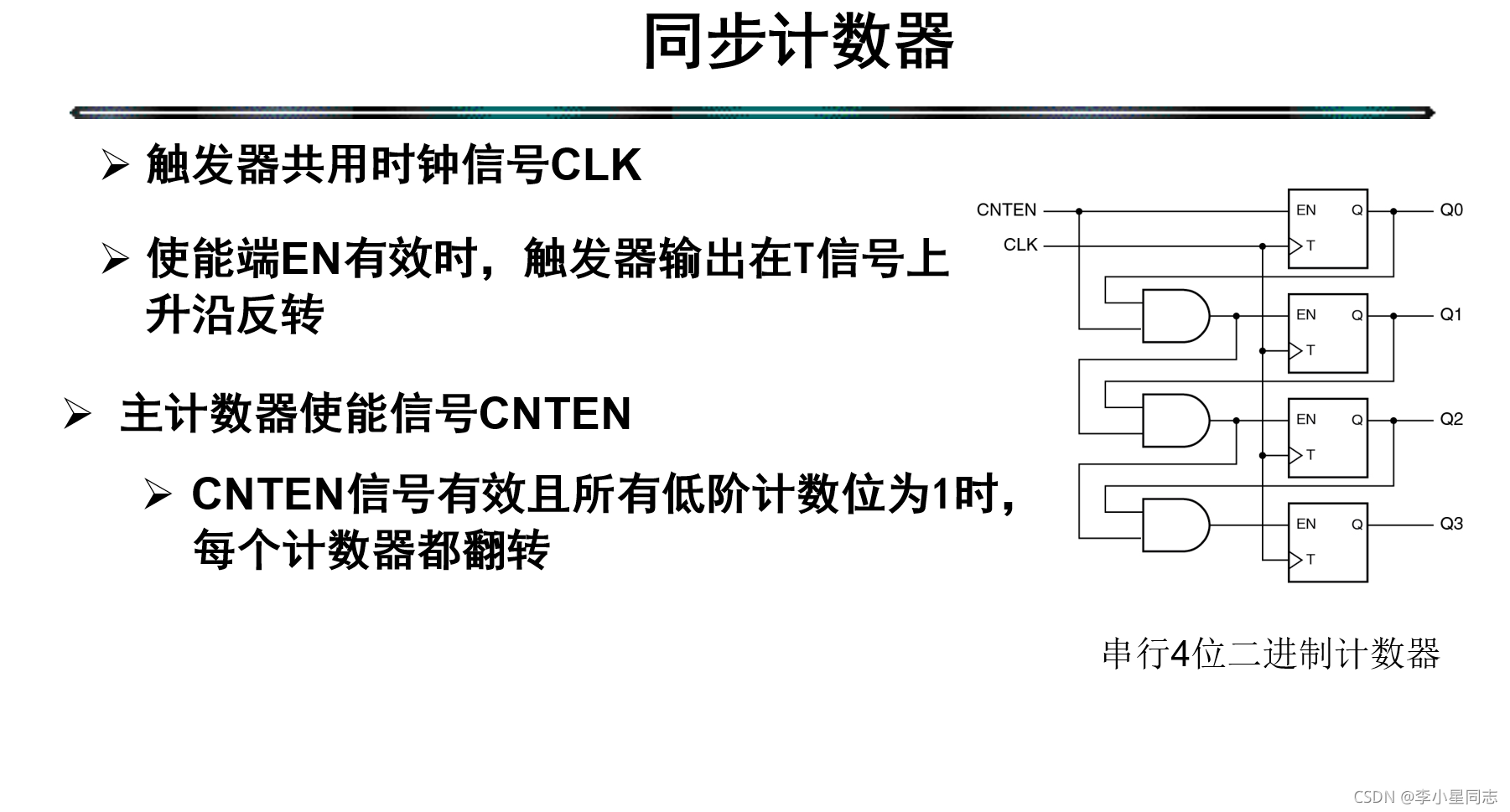

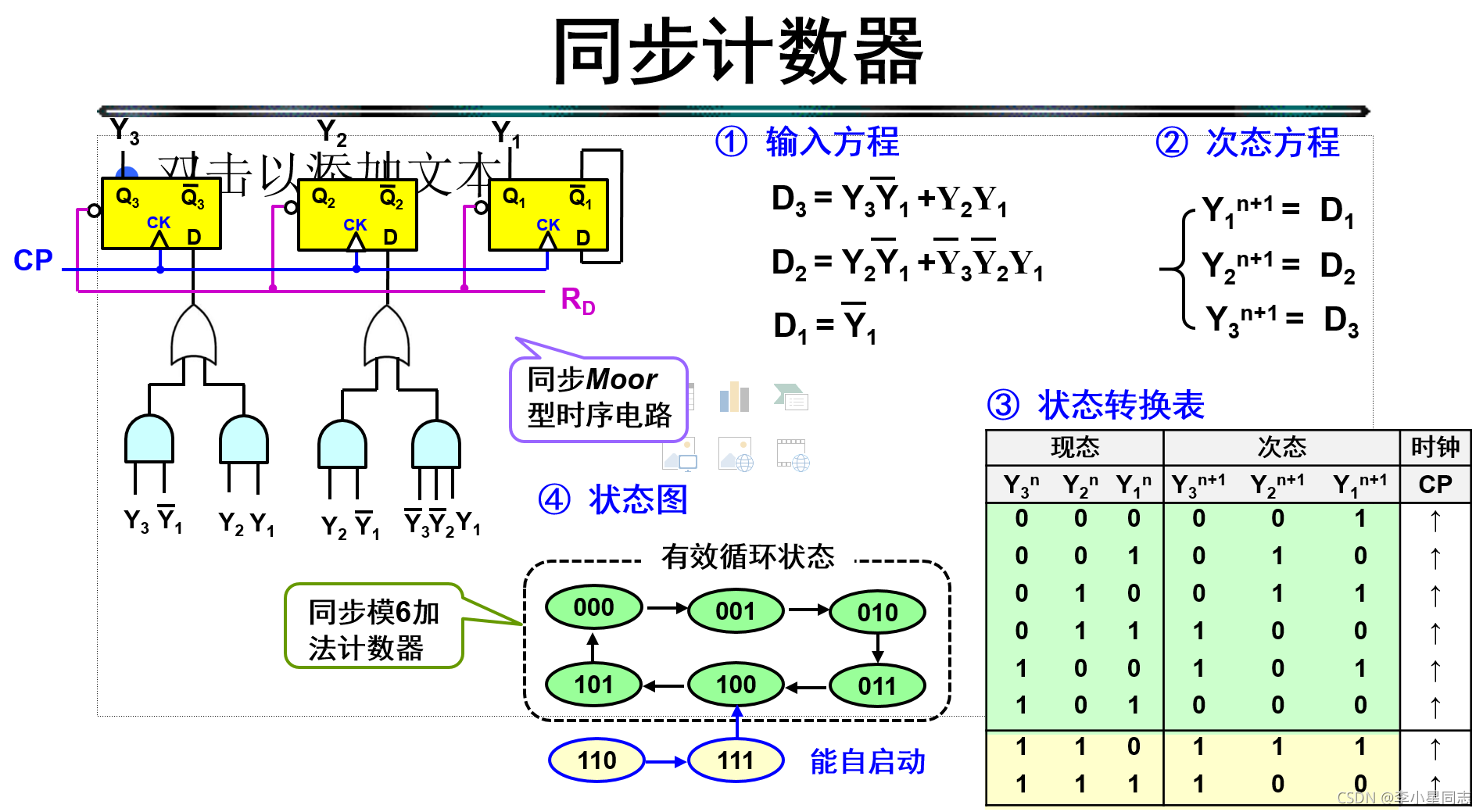

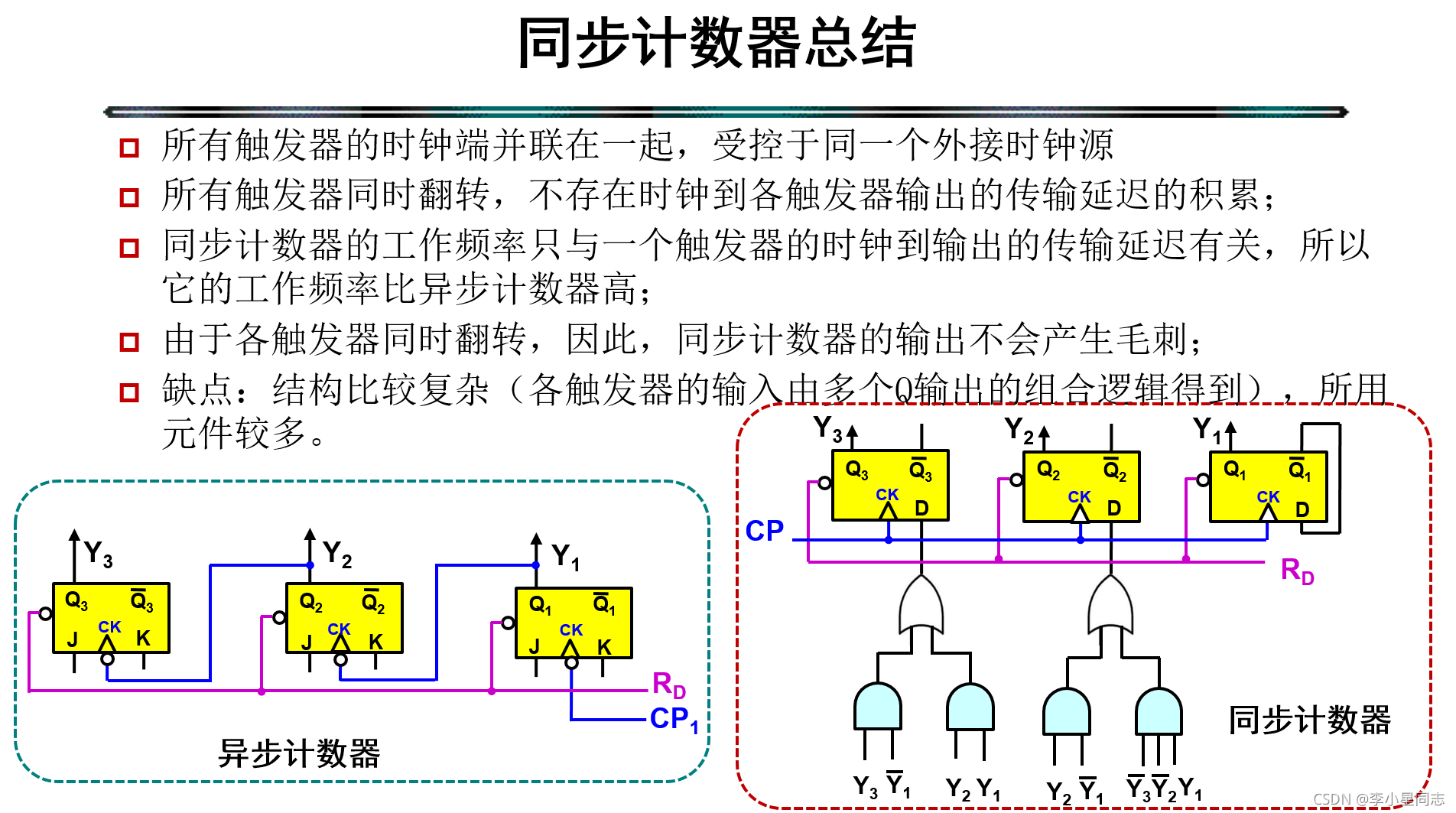

现在是同步的:

假如一开始在有效循环内,那当然好,直接开始循环了;假如不在,也不怕,这个是可以自启动的,从110到111最后自动进入循环。

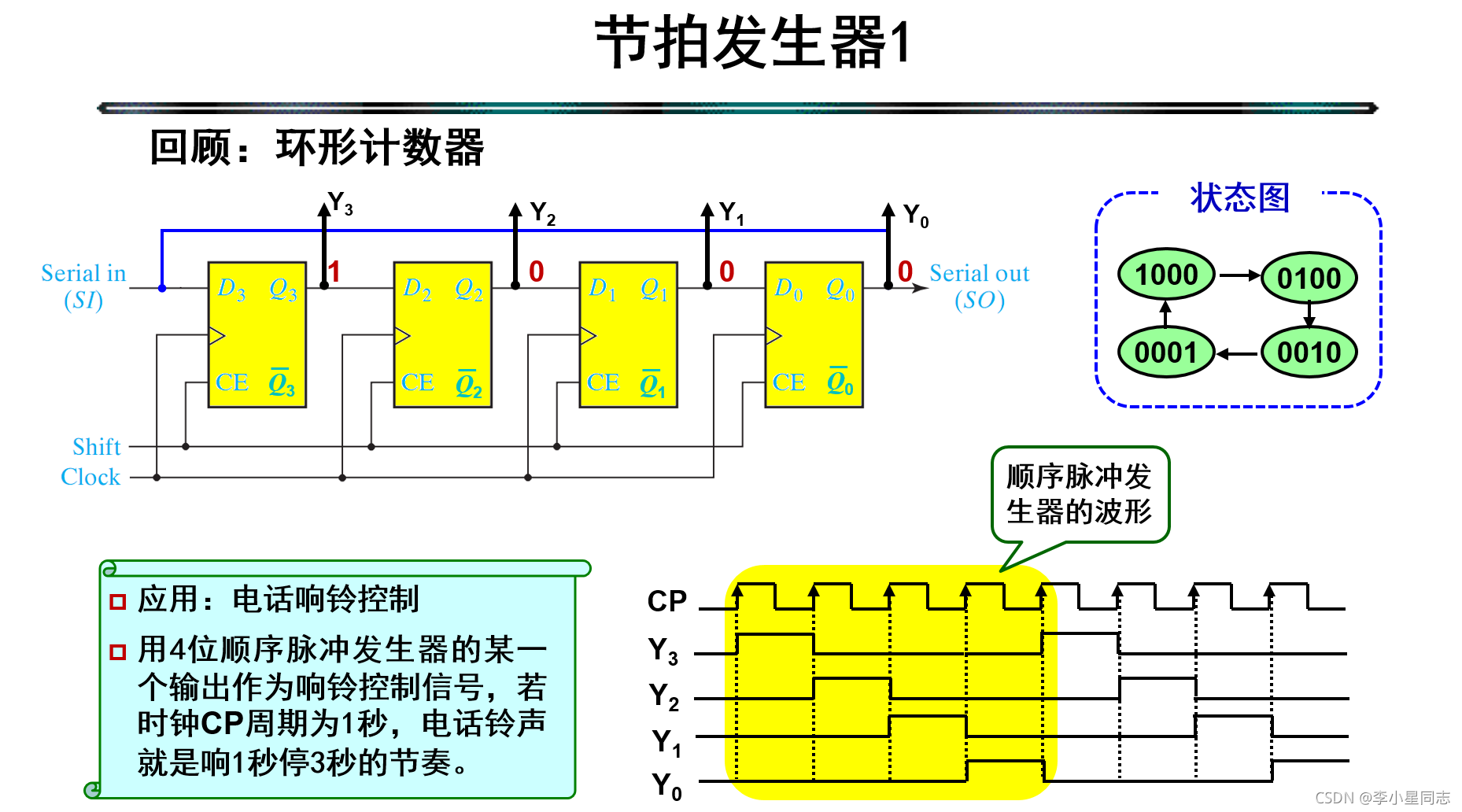

这个是刚才提到过的, 只会一直转转转(环形移位寄存器)。

可以看到,最后面那个(也就是Y0)是0的时候,就会向开头输入一个1,然后就开始不断变化·····

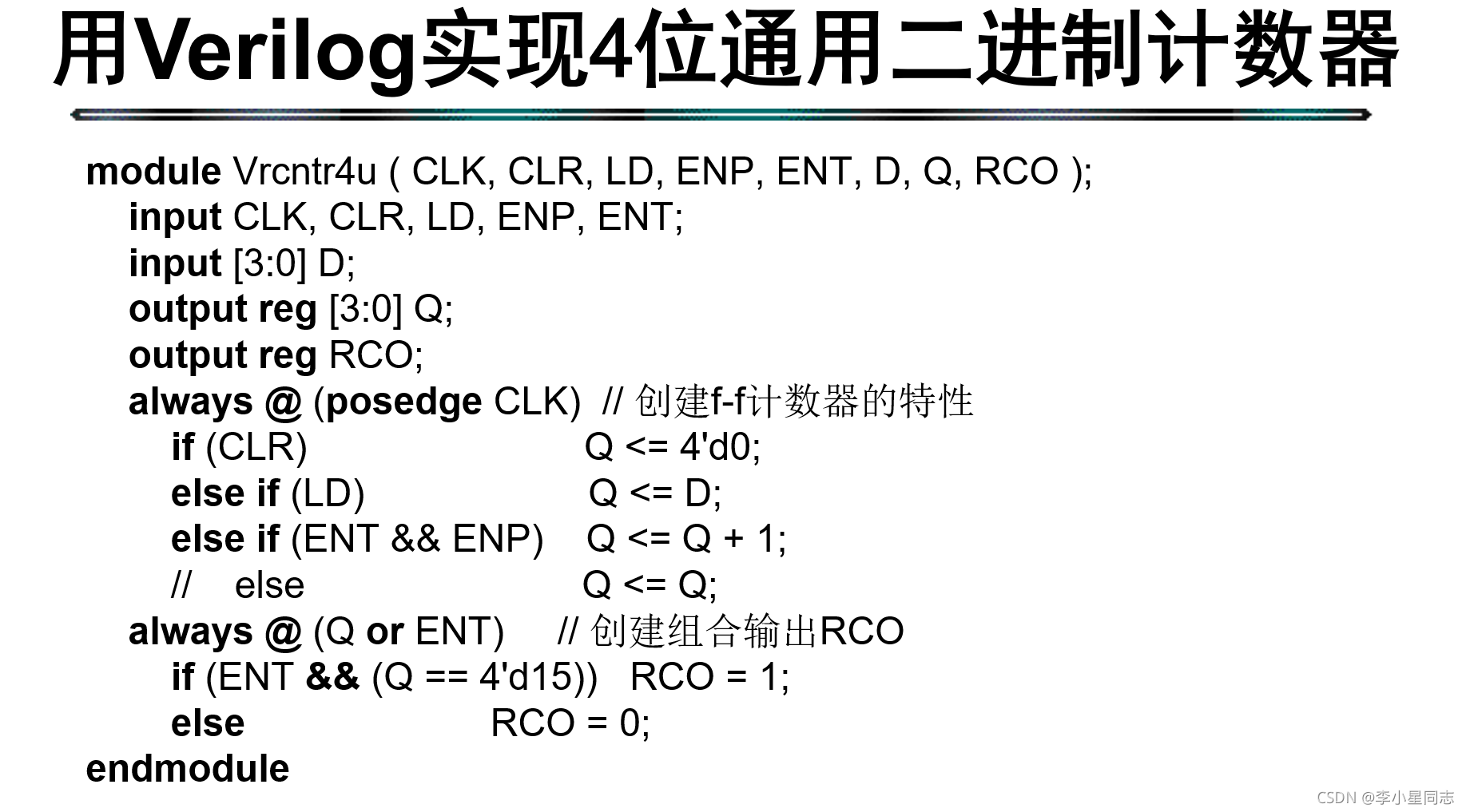

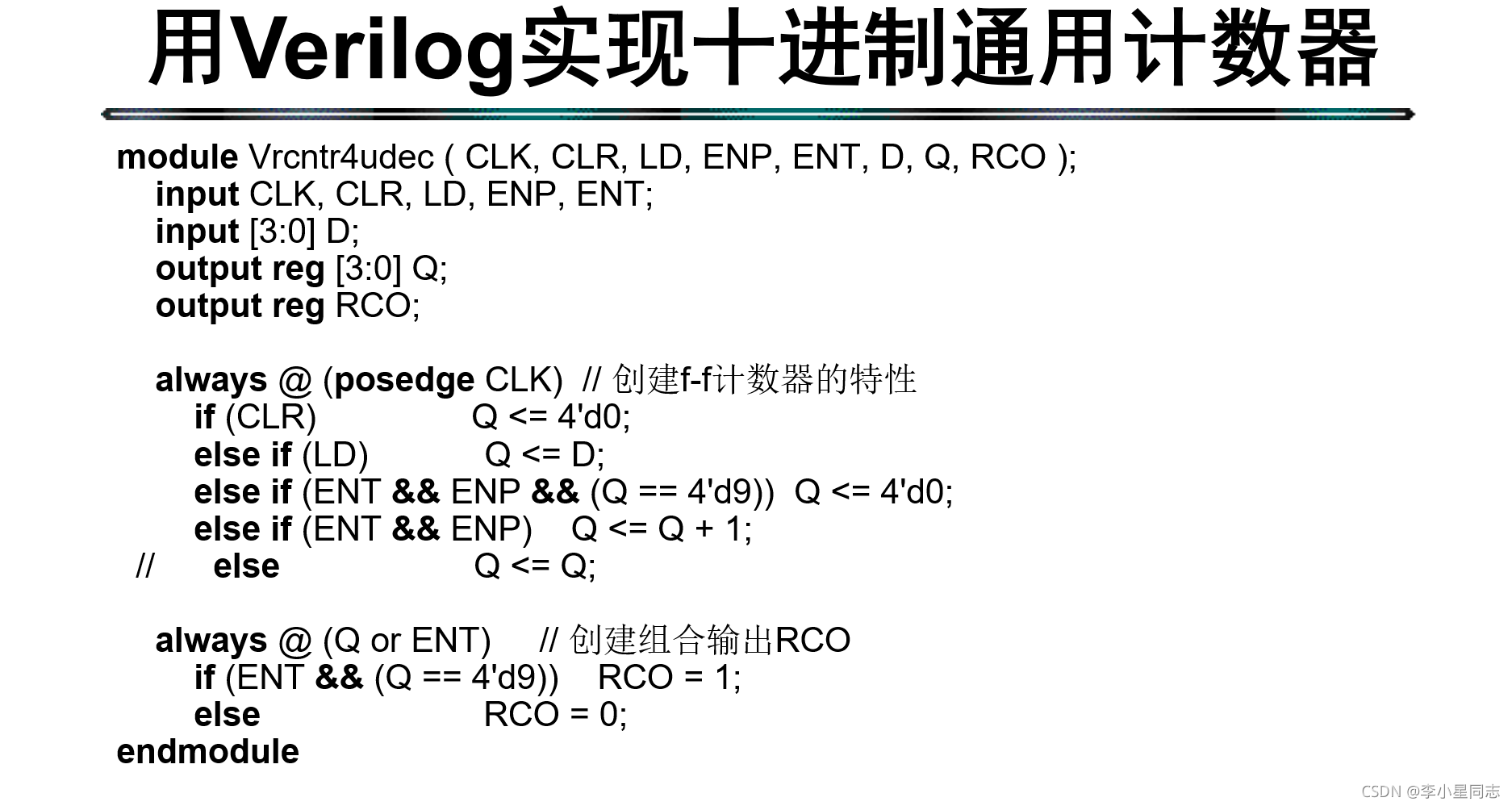

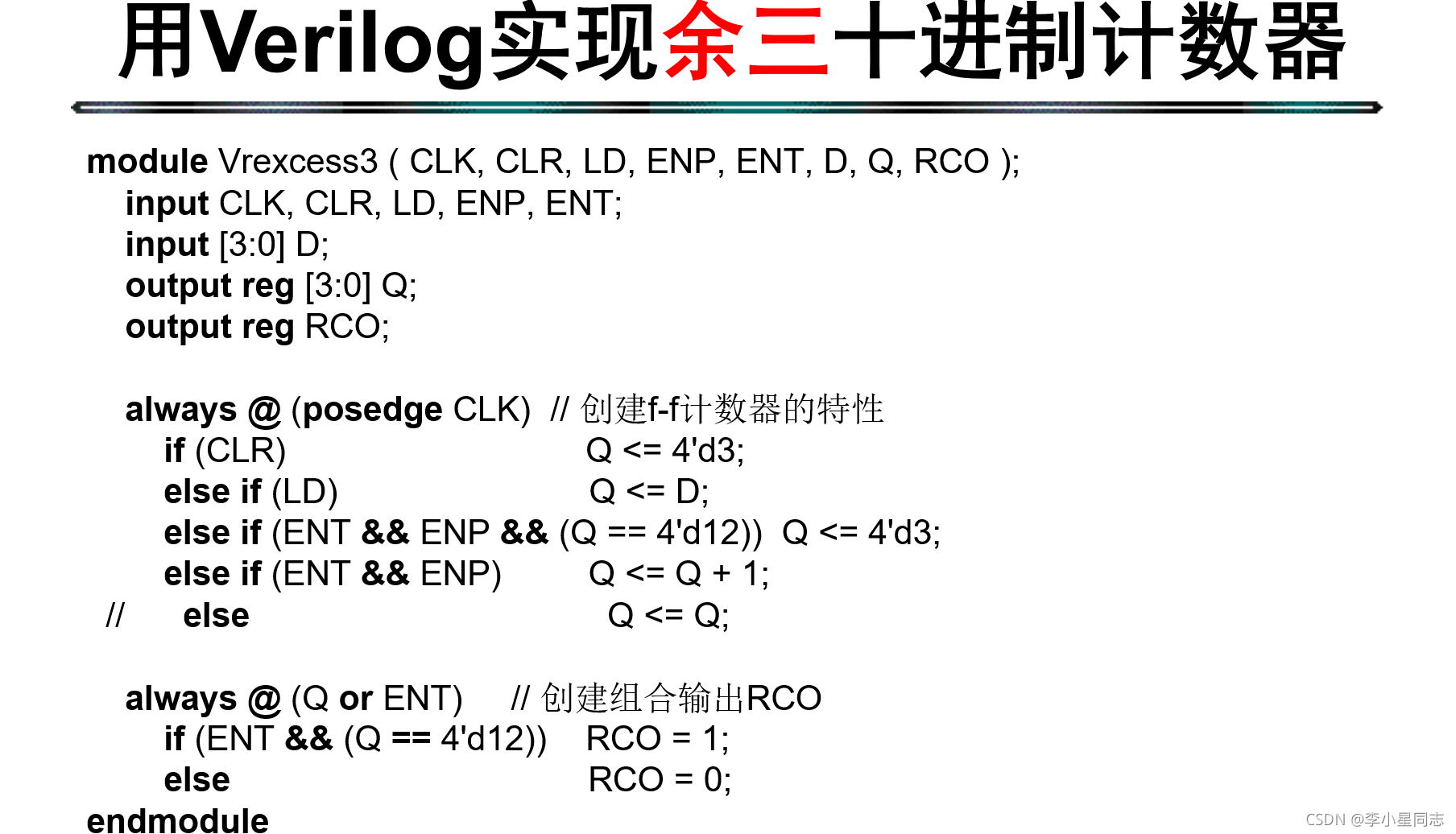

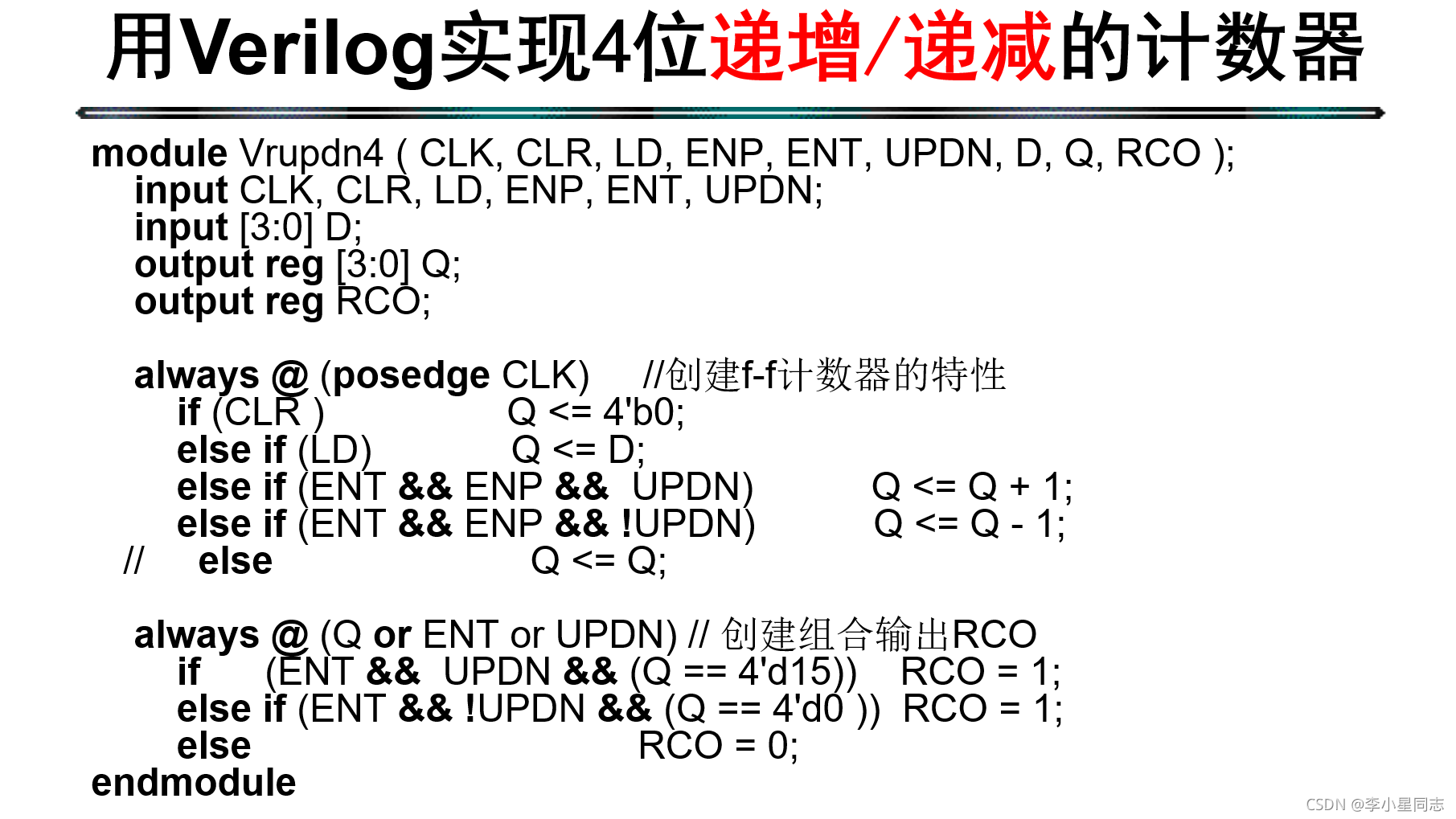

接下来就是用verilog实现的方法:

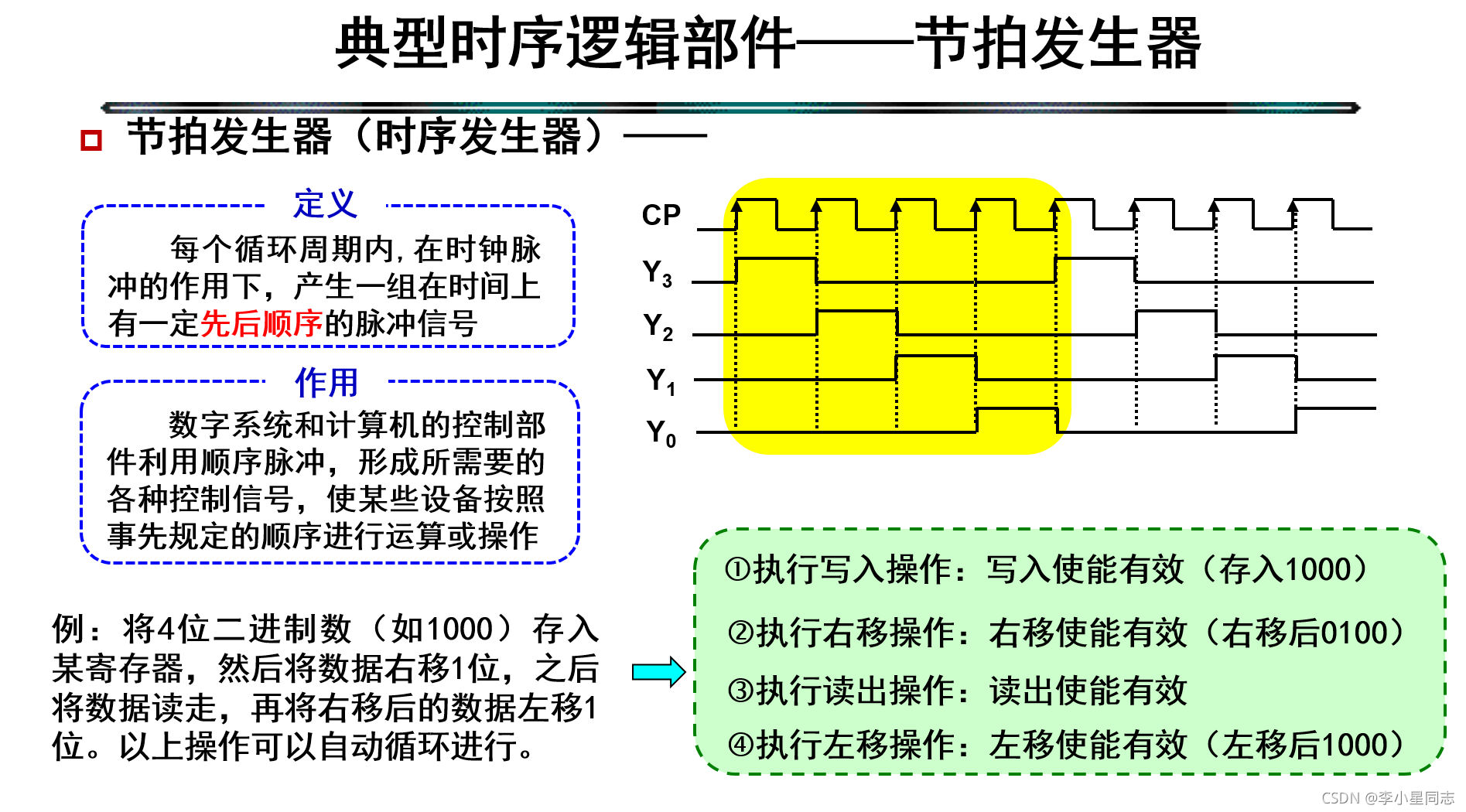

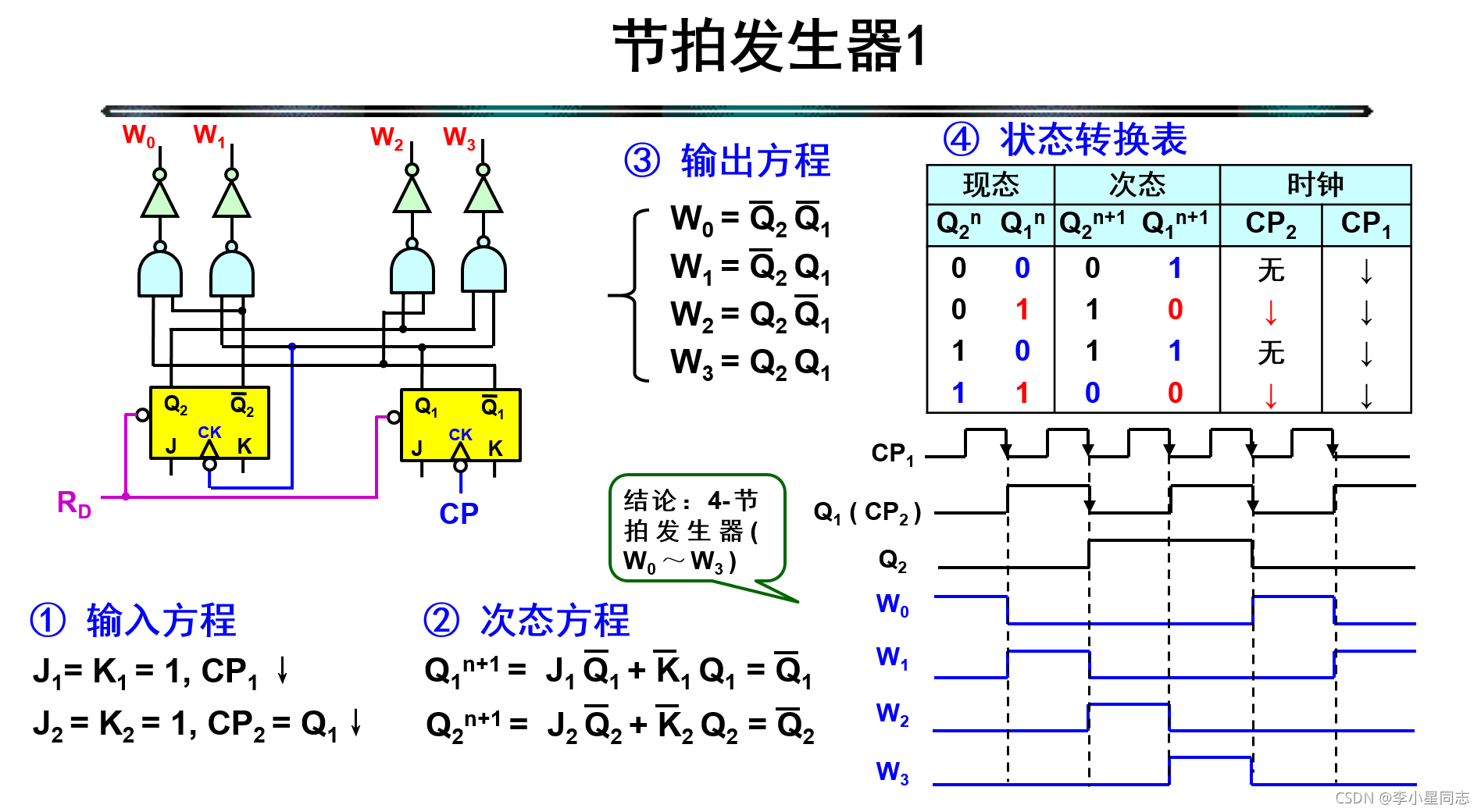

接下来讲讲节拍发生器:

感觉之前的计数器就是节拍发生器?

可见我们之前看到的环形计数器就是节拍器。

1596

1596

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?