I2S/IIS总线介绍及相关EMC问题

简介

Inter-IC Sound集成电路内置音频总线 (I2S) 是用于将数字音频器件连接在一起的串行总线接口标准。此规范来自于 Philips® Semiconductor(I2S 总线规范;1986 年 2 月,修订时间为 1996 年 6 月 5日)。

I2S 组件仅在主控模式下运行。它还可在两个方向上运行,作为发射器(Tx)和接收器(Rx)。

Tx 和 Rx 的数据是独立的字节流。字节流首先包含最高有效字节,并且第一个字的第 7 位 中存放最高有效位。用于每次采样的字节数(左/右声道的采样)是保持样品所需的最少字节数。

请注意IIS于IIC只差一个字母,但实际差距还是挺大的,关于IIC总线介绍,请点击下面文章跳转:《IIC总线介绍(软件、硬件)》

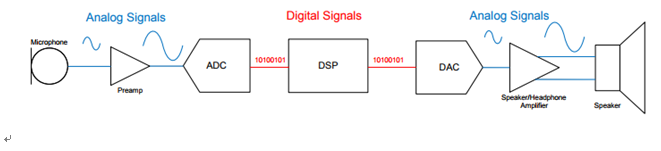

音频一般处理流程

麦克风在机械振动下将声音信号转变为电压信号,电压信号经过放大等处理,给到ADC采样,将模拟信号转化为数字信号;数字信号经过编码、存储、压缩等技术后,发送给解码器-DAC(DSP、专用解码器),将数字信号还原为模拟信号,最后给到喇叭完成声音/音频的播放。

处理流程如下:

IIS用途

飞利浦专为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专门用于音频设备之间的数据传输,目前广泛应用于各种多媒体系统。

IIS总线的信号

1、SDATA,也就是串行数据信号,使用二进制传输数字信号。请注意数据的传输形式为补码的方式。(在有些衍生的接口中包含两条数据线,即就是接收与发送)

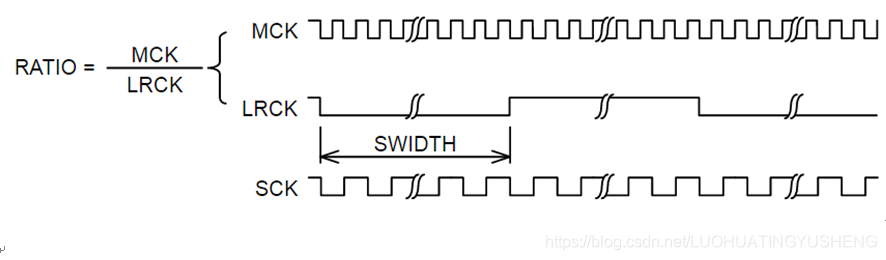

2、SCK,叫做串行时钟,也叫位时钟(BCLK),对应数字音频的每一位数据。SCLK的频率=2×采样频率×采样位数。

3、LRCK,帧时钟,也叫作WS,负责左右声道切换。如为高电平表示右声道声音数据,为低电平表示传输左声道声音数据。其频率等于采样频率。

4、MCK,主时钟,也叫作系统时钟,是采样频率的256倍、384倍、512倍或者768倍,频率范围再0.256~16MHz。

如下所示:MCK、LRCK、SCK:

主要特征:

-

主和从模式:

I2S协议规范定义了两种操作模式,Master和Slave。I2S模式决定两侧(主机或从机)中的哪一侧应提供时钟信号LRCK和SCK,这些信号始终由主机提供给从机。

-

同时双向(TX和RX)音频流:

I2S模块支持串行数据的传输(TX)和接收(RX)。

在这两种情况下,串行数据同步移位到时钟信号SCK和LRCK。在SCK的下降沿将TX数据写入SDOUT引脚,并在SCK的上升沿从SDIN引脚读取RX数据。始终首先发送最高有效位(MSB)。TX和RX均可在主模式和从模式下使用。 -

多种采样频率:

常见的有8KHz、11.025KHz、16KHz、32KHz、44.1KHz、48KHz、64KHz、88.2KHz。 -

多种采样宽度:

一般常见的为8bit、16bit、24bit。

时序

时序规范了在时钟信号的参考下,数据可以正常的传输且被从机正确的采样接收。

以下参数包含了主要的时序要求:如建立时间、保持时间、各时钟信号的频率、占空比、下降时间等。

设计注意事项(EMC相关):

因为IIS的时钟参考线有三个,分别是MCK、LRCK、SCK;请注意以上三组时钟信号的频率由小到大为,LRCK----->SCK------>MCK;

其中MCK和SCK频率比较高,最高可达到20多MHz,此时其时钟信号的谐波分量已经在EMC测试频率范围内了(EMC辐射测试范围30MHz~1GHz,谐波频率为当前时钟信号的倍数-整数倍)。

所以在原理图设计之初,在CLK信号的源端预留RC,用来防止信号完整性和EMC问题,且如果有问题,可以通过RC值来调整,RC的效果有,但是没屏蔽效果好。

实际问题:而实际上我也遇到了这个IIS实际的EMC辐射超标问题,原因出自MCK频率为24MHz,其辐射超标频点为120MHz左右,刚好是5倍频点。

问题原因:

在方案开始选择时,没有注意到此问题,因为该频率在我们这边不算高,才20多MHz,我们使用的SPI Nand Flash的SPI总线速率都可以达到50MHz,所以认为这个绝对不会有问题,但是我们注意到很重要的一个点,就是因为PCB板分开成为两个,两个板子之间刚好需要IIS总线,此时使用软排线连接,这直接导致了辐射超标问题(因为两个板子之间地连接也是细的排线,导致信号参考回流路径存在极大的寄生电感,不符合高速信号回路阻抗最小最短路径,并且因为是软排线未做屏蔽处理)。

问题解决:

板级解决:首先我们优化板级走线,原来是四层板设计,这两个时钟信号走在了了第四层和第一层,注意第二层是完整地,第三层是不完整的分割电源层,此时存在时钟信号跨层参考回流的问题,原因是电源层不完整,导致回流路径变长。

所以优化走线,将第四层的走线重新走在第三层,且做包地处理,完善信号的回流路径。

板子互联解决:

首先这个问题的解决需要考虑多方因素,方案选择(是否可以进行软件重新配置,减小时钟频率或者展频处理),板子的面积(是否方便预留开窗地方,方便后续贴导电海绵\铜箔等导电材料,旨在减小回路阻抗),连接件的选择(软排线的连接虽然轻便,但是回路阻抗不好,使用屏蔽连接排线最好,但是势必增加成本预占用空间)。

最终解决经过评估,从方案出发,将软件配置时的采样频率降低,则时钟信号频率也跟着降低,来减小辐射,最终EMC测试通过。

7698

7698

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?