目录

一、组合逻辑与时序逻辑的区别?

根据逻辑功能的不同特点,可以将数字电路分成两大类,一类称为组合逻辑电路,另一类称为时序逻辑电路。

(一)组合逻辑:

组合逻辑电路中,任一时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。这就是组合逻辑电路在逻辑功能上的共同点。

(二)时序逻辑:

时序逻辑电路中,任一时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说还与之前的输入有关。

这里的组合逻辑与时序逻辑与后面状态机的两种类型相似,可以结合起来记忆。

二、竞争与冒险。

(一)定义:

竞争与冒险是逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲(又称过渡干扰脉冲)的现象。

(1)竞争:

当一个逻辑门的两个输入端的信号同时向相反方向变化时,从变化开始到达稳定状态所需的时间不同,称为竞争。

(2)冒险:

逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲(又称过渡干扰脉冲)的现象。(有竞争不一定有冒险,有冒险一定有竞争)

(二)产生原因:

信号经过逻辑门电路都需要一定的时间,由于不同路径上的门级数不同,信号经过不同路径传输的时间也不同,或者门的级数相同但是各个门的延迟时间也有差异,也会造成传输时间不同。

简单说就是:两个反向信号到达目标门级电路的时间不一致,相互叠加可能会产生尖峰脉冲。

(三)判断方法:

(1)卡诺图:

卡诺图相切处没有其他卡诺圈。

(2)代数法:

存在相反变量就有可能存在竞争与冒险。

(3)实验法:

通过示波器进行观察。

(四)消除方法:

(1)修改逻辑设计,增加沉余项。

(2)输出端并联电容进行滤波。

(3)使用格雷码。

(4)信号同步处理。

(5)信号延迟:延迟较小的支路上加上毛刺宽度的延迟可以进行消除。

注:补充一个滤除毛刺的方法

(1)小于一个周期的毛刺

把信号打两拍,把打一拍后的信号和两拍后的信号相或。(打拍:D触发器,时序逻辑非阻塞赋值)

(2)一个周期到两个周期之间的毛刺

打三拍,把打拍后的信号相或。

三、D触发器。

边沿触发器,对边沿信号敏感。

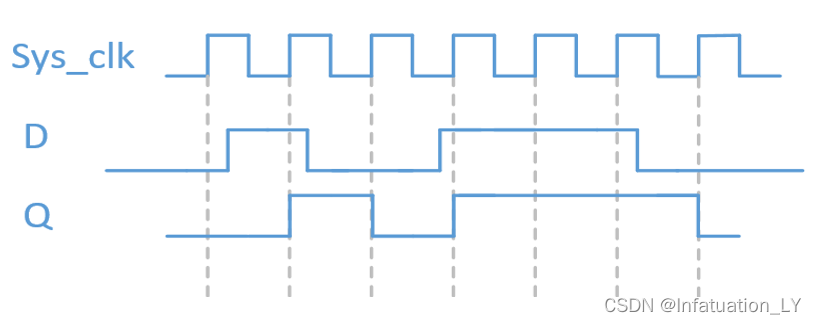

D触发器

时钟上升沿是D信号是1接下来的一个时钟周期Q就输出1,时钟上升沿是D信号是0接下来的一个时钟周期Q就输出0,再次使用D触发器就是讲Q的波形图再往后延迟一个时钟周期。

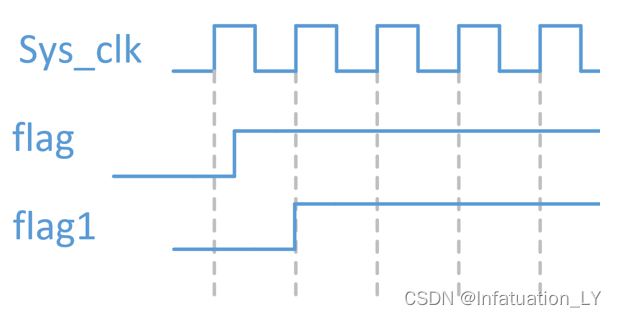

在verilog硬件描述语言,所有经过非阻塞赋值的数据,都相当于经过了一次D触发器(又称打拍)。例:

module D_CFQ

(

input sys_clk , //系统时钟为50MHz

input flag , //输入信号

output reg flag1 //经过D触发器(打拍/非阻塞赋值)的信号

);

lways@(posedge sys_clk)

flag <= flag1;

endmodule

非阻塞赋值(打拍/D触发器)

四、亚稳态 。

(一)什么是亚稳态?

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

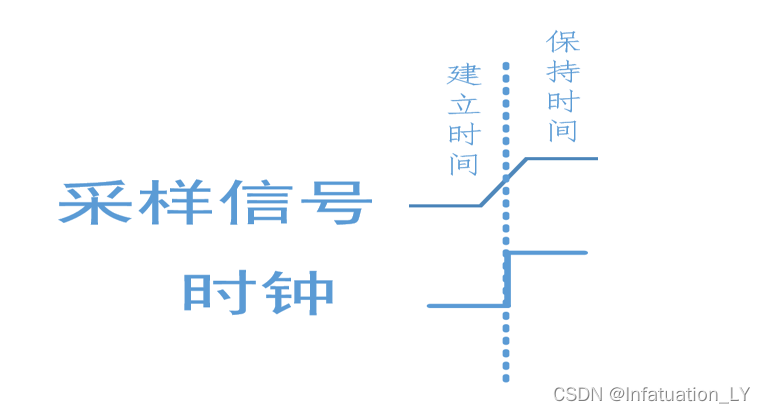

(二)产生原因:

采样信号在被采样时建立时间和保持时间没有达到要求,无法采样得到准确的值。

(三)解决办法:

将外部接收到的待处理信号在系统时钟下打拍后使用。

五、同步复位。

(一)优点:

(1)抗干扰性高,可以剔除复位信号中短于时钟周期的毛刺。

(2)有利于静态时序分析工具的分析。

(3)有利于基于周期的仿真工具的仿真。

(二)缺点:

(1)占用更多的逻辑资源。

(2)对复位信号的脉冲宽度有要求,必须大于指定的时钟周期,由于线路上的延迟,可能需要多个时钟周期的复位脉冲宽度,且很难保证复位信号到达各个寄存器的时序。

(3)同步复位依赖于时钟,如果电路中的时钟信号出现问题,无法完成复位。

六、异步复位。

(一)优点:

(1)不需要额外的逻辑资源,实现简单,而且CPLD有针对复位信号的全局布线资源,可以保证复位引脚到各个寄存器的时钟偏差最小(不是到各个寄存器的延迟最小)。

(2)复位信号不依赖于时钟。

(二)缺点:

(1)复位信号容易受到外界的干扰,并且对电路内的毛刺敏感。

(2)复位信号释放的随机性可能导致时钟时序违规,也就是复位释放时在时钟有效沿附近,会使电路处于亚稳态。

七、异步复位,同步释放。

异步复位,同步释放是指复位信号产生时不受时钟信号的控制,但是释放的时候受到时钟信号的同步。简单说就是复位信号在时钟下打拍,用打拍过后的新的复位信号进行异步复位。主要目的是防止复位信号释放时候产生亚稳态。

Verilog代码:

module rst

(

input sys_clk , //系统时钟为50MHz

input sys_rst_n , //复位信号(一般为低电平)

output wire rst_n //异步复位,同步释放后的信号

);

reg sys_rst_n0, sys_rst_n1; //打拍后的信号

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

begin

sys_rst_n0 <= 0;

sys_rst_n1 <= 0;

end

else

begin

sys_rst_n0 <= sys_rst_n;

sys_rst_n1 <= sys_rst_n0;

end

assign rst_n = sys_rst_n1;

endmodule八、锁存器(Latch)。

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个 I/O 口既能输出也能输入的问题。锁存器是利用电平控制数据的输入,它包括不带使能控制的锁存器和带使能控制的锁存器。

(一)产生:

在组合逻辑中:

(1)if...else未成对出现。

(2)case语句不完备(多为无default)。

(3)输出信号给自己赋值。

(二)危害:

(1)产生毛刺。

(2)不能异步复位。

(3)额外延时。

(4)占用资源。

2268

2268

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?