简易电压表的设计

学习资料:野火 升腾Pro《FPGA Verilog开发实战指南——基于Xilinx Artix7》2021.11.16

1. 理论知识

对模拟信号的测量需要A/D转换,常见的模/数转换器将经过与标准量比较处理后的模拟量转换为以二进制数值表示的离散信号。一般分为四个步骤,采样、保持、量化、编码。

2. 工程设计

实验目标:外部挂载的高速 AD/DA 板卡的 A/D 部分将输入其中的模拟信号转换为数字量,将数字量传入 FPGA,FPGA 将传入的数字量通过计数转化为电压数值,通过 ila 在线抓取转化后的电压值,实现模拟信号的电压测量。

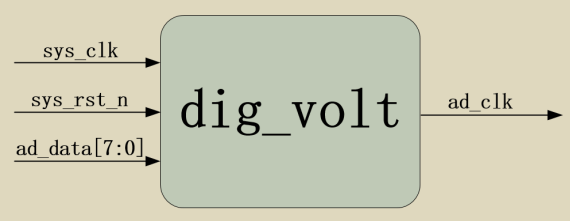

工程模块框图:

通过AD板卡模块后,会将模拟电压转换为数字值传给FPGA,通过计算得到电压值,这里通过 ila 在线抓取转化后得到测量电压值。ad_clk为传入外载板卡的时钟信号,频率为 12.5MH 中,由系统时钟信号 4 分频得到。

本实验使用的 ADC 芯片位宽为 8 位,板卡模拟电压输入范围为-5v~+5v,即电压表测量范围,最大值和最小值压降为 10v,分辨率为 10/2^8。 当 ADC 芯片采集后的电压数值 ad_data 位于 0 - 127 范围内,表示测量电压位于-5V ~ 0V 范围内,换算为电压值:Vin = - (10 / 2 ^ 8 x (127 - ad_data));当 ADC 芯片采集后的电压数值 ad_data 位于 128 - 255 范围内,表示测量电压位于 0V ~ 5V 范围内,换算为电压值:Vin= (10 / 2 ^ 8 x (ad_data - 127))。

波形图

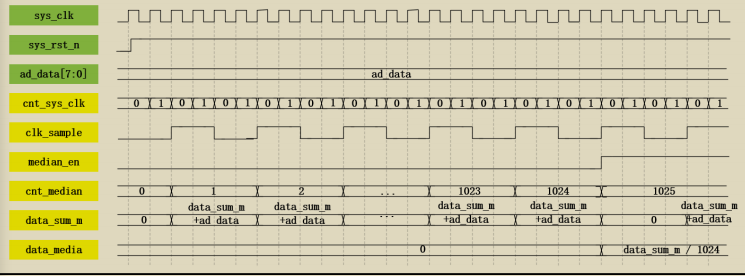

输出信号ad_clk是sys_clk四分频。并且取反得到的,所以先声明了一个工作时钟clk_sample,通过cnt_sys_clk计数得到。

为了计算中值median,声明median_en信号,前期是统计中值和,然后median_en取反后计算中值。所以需要统计多少个中值,并且需要计算累加和,所以声明了cnt_median变量和data_sum_m.

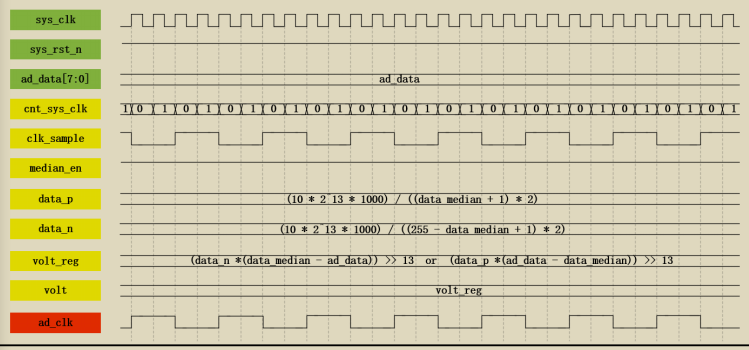

中值 data_median 确定后,开始测量电压的计算,为保证运算后的电压值更准确,我们对计算出的分辨率进行放大1000x2 ^ 13倍。

data_p和data_n是为了方便计算,提前把公因子拿出来便于简化代码。然后对测量值计算即可,不过在计算完后要除以放大倍数。

关于实验代码和仿真详见资料。

7038

7038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?