大家好,我是小悟。

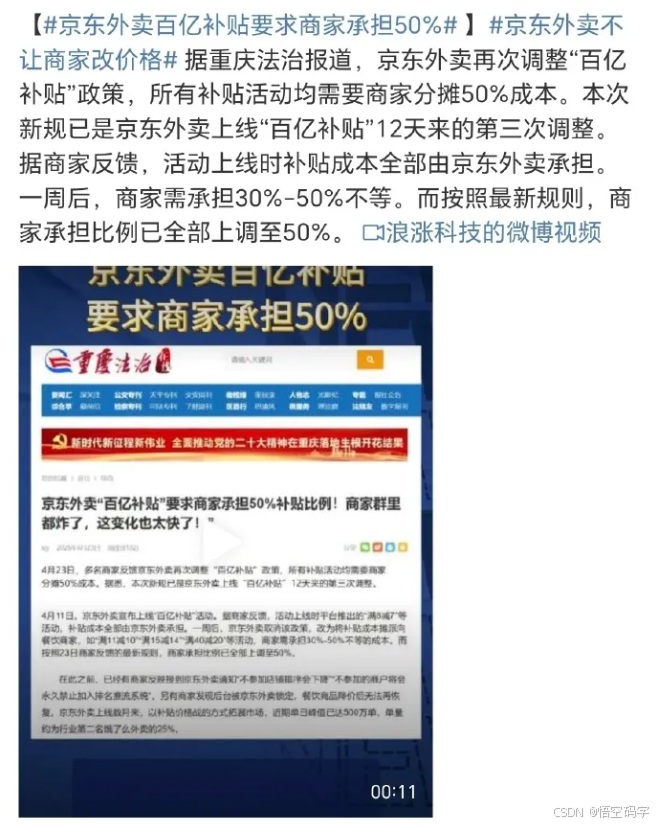

外卖圈冒出一则“大瓜”——有消息称京东外卖的“百亿补贴”突然加码,要求商家必须分摊50%的费用,甚至玩起“不参加就降排名”的潜规则。

眼看着舆论热度飙升,京东外卖迅速甩出一记辟谣声明:“纯属造谣!”并甩出实锤:平台从未强制要求商家掏钱,所有补贴政策都开放协商。

谁在搅动舆论?谣言背后总有推手。京东外卖在声明中直接点名“有组织的水军”,不难想象,这波操作或许意在制造对立,让商家对平台失去信任,甚至挑拨消费者和平台的关系。

毕竟谁不想薅点羊毛?可平台要生存、商家要利润,一味压榨某一方,市场迟早崩。

补贴不等于救命稻草,别被低价迷了眼。很多人觉得,补贴就是平台撒钱让消费者捡便宜,商家坐收订单。

补贴是吸引流量的工具,但流量能否转化为长期生意,还得看商家自身的竞争力。如果商家把补贴当“药罐子”,只顾低价走量,忽略了品质和服务,最后烧光钱也留不住人。

合作本应共赢,别搞“零和博弈”。真正健康的外卖生态,不该是平台赚所有钱,也不是商家单方面承压。

京东外卖的“双低”(低佣金+补贴)模式,初期确实让部分商家尝到甜头。“一单利润顶别家好几单。”

其实,商家的不满未必全是补贴分摊,而是怕平台突然变卦、算计太多。若补贴规则能保持稳定、沟通渠道畅通,商家也会更安心。

互联网行业的博弈,总伴随着真假难辨的传闻。我们更需要一颗平常心。遇到传言要冷静对待。

平台、商家、消费者本是利益共同体,与其互相猜忌,不如多些理解与协作。毕竟,外卖这盘饭,大家一起才能端得稳。

谢谢你看我的文章,既然看到这里了,如果觉得不错,随手点个赞、转发、在看三连吧,感谢感谢。那我们,下次再见。

您的一键三连,是我更新的最大动力,谢谢

山水有相逢,来日皆可期,谢谢阅读,我们再会

我手中的金箍棒,上能通天,下能探海

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?