系列文章目录

XHCI 1.2b 规范摘要(一)

XHCI 1.2b 规范摘要(二)

XHCI 1.2b 规范摘要(三)

XHCI 1.2b 规范摘要(四)

XHCI 1.2b 规范摘要(五)

XHCI 1.2b 规范摘要(六)

XHCI 1.2b 规范摘要(七)

XHCI 1.2b 规范摘要(八)

XHCI 1.2b 规范摘要(九)

XHCI 1.2b 规范摘要(十)

XHCI 1.2b 规范摘要(11)

XHCI 1.2b 规范摘要(12)

XHCI 1.2b 规范摘要(13)

XHCI 1.2b 规范摘要(14)

XHCI 1.2b 规范摘要(15)

文章目录

- 系列文章目录

- 5 寄存器接口(Register Interface)

- 5.1 寄存器约定(Register Conventions)

- 5.2 PCI 配置寄存器 (USB)

- 5.3 Host Controller 功能寄存器

5 寄存器接口(Register Interface)

可扩展的 USB 主机控制器包含许多软件可访问的硬件寄存器。大部分 registers 显示为 Memory-mapped Host Controller Registers 。其他 registers 可能使用非 memory address 机制出现,例如基于 PCI 或 PCIe 的 Host Controller 。对于这些 designs,需要实现相应规范定义的 required registers 。

请注意, xHCI 不需要支持独占访问机制 (例如 PCI LOCK) 来访问内存映射寄存器空间。因此,如果软件尝试对 host controller memory-mapped register space 进行独占访问,则结果是不确定的。

有关 xHCI 扩展功能寄存器集的细目,请参阅表 7-2。

5.1 寄存器约定(Register Conventions)

如果 xHC 支持 64 位寻址 (AC64 = ‘1’),则软件应仅使用 Qword 访问来写入 64 位寄存器。如果系统无法发出 Qword 访问,则应使用 2 个 Dword 访问来写入 64 位地址字段;先写入低 Dword,然后写入高 Dword。

如果 xHC 支持 32 位寻址 (AC64 = ‘0’),则包含 64 位地址字段的寄存器的高 Dword 未使用,软件应仅使用 Dword 访问来写入地址。

注意:USB 传统支持 (USBLEGSUP) 扩展功能需要支持信号量地址的字节访问,请参阅第 7.1 节。

所有多字节寄存器字段都遵循小端顺序;也就是说,较低的地址包含字段的最低有效部分。字段内的字节/字符应采用小端顺序,即,字符串的第一个字符在最低有效字节,第二个字符在下一个有效字节,依此类推。

5.1.1 属性(Attributes)

以下表示法用于描述 register 访问属性:

5.1.2 电源井注意事项(Power Well Considerations)

请参阅第 4.23.1 节。

5.2 PCI 配置寄存器 (USB)

PCI Configuration Registers (USB) 。

专为在基于 PCI 的系统中运行而设计的 xHC 应实现符合 PCI 规范或 PCIe 规范的 PCI 配置空间,具体取决于目标操作环境。实施者应参考 PCI 特别兴趣小组 (SIG) (http://www.pcisig.com) 发布的相应规范。

5.2.1 Type 0 PCI Header

图 5-1 描述了 xHC 的 PCI 配置空间。基于 PCI 的 xHC 需要实现 PCI,即 0 类 PCI 设备标头,如下所示。xHC 还需要至少实现前两个基址寄存器(BAR 0 和 BAR 1)才能启用 64 位寻址。这些 Base Address Registers 用于指向主机控制器的内存映射 Input/Output (MMIO) 寄存器空间的开头。

寄存器指向关系:

5.2.2 类代码寄存器(Class Code Register)

此 register 包含与 Sub-Class Code 和 Base Class Code 定义相关的器件编程接口信息。此寄存器还标识 Base Class Code 和与 Base Class Code 相关的函数子类。

5.2.3 串行总线版本号寄存器 (SBRN)

Serial Bus Release Number Register (SBRN) 。

该寄存器包含该通用串行总线主控制器模块所符合的通用串行总线规范的版本。

5.2.4 帧长调整寄存器 (FLADJ)

Frame Length Adjustment Register (FLADJ) 。

该寄存器位于辅助电源井中。此功能用于调整与生成驱动 SOF 计数器的时钟的时钟源之间的任何偏移。当将新值写入这六个位时,将调整由 xHC 实现的所有 USB 总线的帧长度。其初始编程值取决于硬件 USB 时钟的准确性,并由系统软件(通常是 BIOS)初始化。仅当 USBSTS 寄存器中的 HCHalted (HCH) 位为“1”时才应修改此寄存器。在主机控制器运行时更改此寄存器的值会产生未定义的结果。

5.2.5 默认尽力服务延迟 (DBESL)

Default Best Effort Service Latency (DBESL) 。

该寄存器包含对 PORTPMSC 最佳努力服务延迟 (BESL) 字段进行编程的最佳值。有关详细信息,请参阅第 4.23.5.1.1.1 节。

如果不支持 BESL LPM(HLC =“0”或 BLC =“0”),则保留此寄存器。

5.2.6 默认尽力服务延迟深度 (DBESLD)

Default Best Effort Service Latency Deep (DBESLD) 。

该寄存器包含对 PORTPMSC 最佳努力服务延迟 - 深度 (BESLD) 字段进行编程的最佳值。有关更多信息,请参阅第 4.23.5.1.1.1 节。

如果不支持 BESL LPM(HLC =“0”或 BLC =“0”),则保留此寄存器。

5.2.7 PCI 电源管理接口(PCI Power Management Interface)

下图是 PCI 电源管理功能(PCI Power Management Capability)中定义的寄存器的描述。xHCI 兼容主机控制器应实现 PCI 规范中定义的 PCI Power Management Capability,该寄存器与 PCI PM 规范中定义的结构几乎相同,但有一些额外的要求。有关 PCI 电源管理的其他 xHCI 操作要求,请参阅附录 A.1。

5.2.7.1 PCI 电源管理寄存器(PCI Power Management Registers)

所有字段在完全通电时都会重置。退出 D3cold 状态时,除 PME_En 和 PME_Status 之外的所有 PCI PM PMCSR 寄存器字段都会重置。如果没有提供辅助电源,则退出 D3cold 状态时 PME_En 和 PME_Status 字段也会重置。

PCI 功能列表用于为软件提供查找和使用 PCI 电源管理的标准方法。有关电源管理寄存器块的定义,请参阅 PCI PM 规范中的第 3.2 节。

5.2.8 消息信号中断(MSI & MSI-X)功能

Message Signaled Interrupts (MSI & MSI-X) Capability 。

以下是 PCI Message Signaled Interrupt (MSI,消息信号中断) 功能中定义的寄存器的描述。如果 xHC 支持 PCI 或 PCIe,则它应实现 PCI 规范中定义的 PCI MSI 和/或 MSI-X 功能。

5.2.8.1 配置 MSI(MSI configuration)

图 5-3 说明了 Message Signaled Interrupt (MSI) Configuration 功能布局,它由 7 个字段组成。有关 MSI 功能结构的定义,请参阅 PCI 规范中的第 6.8.1 节。

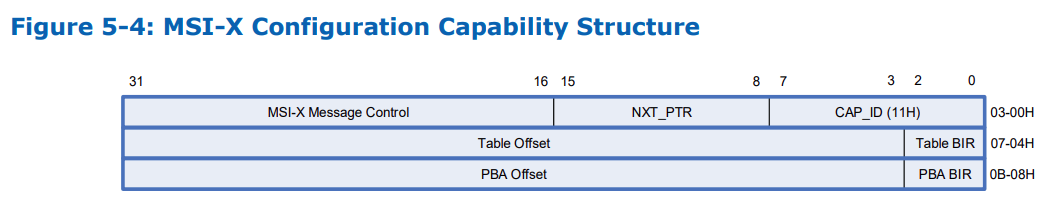

5.2.8.2 配置 MSI-X(MSI-X configuration)

MSI-X 功能结构如图 5-4 所示。每个功能禁止使用多个 MSI-X 配置功能结构,但允许一个功能同时具有 MSI 和 MSI-X 功能结构。

与直接包含功能向量的所有控制/状态信息的 MSI 功能结构不同,MSI-X 功能结构指向 MSI-X 表结构和 MSI-X 待处理位阵列 (PBA) 结构,每个结构都驻留在内存空间中。

每个结构都由属于该功能的基址寄存器 (BAR) 映射,位于配置空间的 10h 处。BAR 指示寄存器 (BIR) 指示哪个 BAR,Qword 对齐偏移量指示结构相对于与 BAR 关联的基址的起始位置。BAR 可以是 32 位或 64 位,但必须映射内存空间。允许函数将两个结构映射到同一个 BAR,或者将每个结构映射到不同的 BAR。

MSI-X 表结构通常包含多个条目,每个条目由几个字段组成:消息地址、消息上位地址、消息数据和向量控制。每个条目都能够指定一个唯一的向量。

待处理位阵列 (PBA) 结构包含函数的待处理位,每个表条目一个,以 Qword 内的位封装阵列形式组织。

最后一个 QWORD 不一定完全填充。

有关 MSI-X 功能和表结构的定义,请参阅 PCI 规范中的第 6.8.2 节。以下小节描述了与 xHC 相关的 MSI-X 实现问题。

5.2.8.3 MSI-X 表(MSI-X Table)

MSI-X Capability Table Offset 字段指向 MSI-X 表。有关 MSI-X Table Entry 字段的定义,请参阅 PCI 规范中的第 6.8.2.6 至 6.8.2.9 节。注意:xHC 架构支持的最大中断器数量为 1024。实现所需的 MSI-X Table Entry 的实际数量由 HCSPARAMS1 寄存器 MaxIntrs 字段决定。有关 Table Entry 寻址,请参阅第 5.2.8.5 节。

5.2.8.4 MSI-X PBA

MSI-X Capability PBA Offset 指向 PBA(待处理位阵列,Pending Bit Array)。有关 MSI-X 表条目待处理位的定义,请参阅 PCI 规范中的第 6.8.2.10 节。

注意:xHC 架构支持的最大中断器数量为 1024。因此,只实现了一个 PBA Qword,并且(最多)只实现了低阶 1023 位。实际实现的待处理位数量由 HCSPARAMS1 寄存器 MaxIntrs 字段决定。有关待处理位寻址,请参阅第 5.2.8.5 节。

5.2.8.5 访问 MSI-X 表和 MSI-X PBA

Accessing the MSI-X Table and MSI-X PBA 。

5.2.9 PCI Express Capability

下面描述的结构代表 PCI Express 功能结构,该结构应针对任何设计为在支持 PCIe 的系统内作为 PCIe 设备运行的 xHC 实施。请参阅 PCIe 规范的第 7.8 节,了解有关此结构实现的详细信息。

5.2.10 SR-IOV 扩展能力(SR-IOV Extended Capability)

5.3 Host Controller 功能寄存器

Host Controller Capability Registers 。

所有 Capability Registers 都是只读 (RO) 的。这些 registers 的偏移量都是相对于主机控制器的 MMIO 地址空间的开头的。在本文档中,主机控制器的 MMIO 地址空间的开头称为 “Base” 。

5.3.1 功能寄存器长度 (CAPLENGTH)

Capability Registers Length (CAPLENGTH) 。

地址: Base + (00h)

属性:RO

大小:8 bits

5.3.2 主机控制器接口版本号 (HCIVERSION)

Host Controller Interface Version Number (HCIVERSION) 。

地址: Base + (02h)

属性:RO

大小:16 bits

例如,0100h 对应于 xHCI 版本 1.0.0,或者 0110h 对应于 xHCI 版本 1.1.0,依此类推。

5.3.3 结构参数1 (HCSPARAMS1)

Structural Parameters 1 (HCSPARAMS1) 。

地址: Base + (04h)

属性:RO

大小:32 bits

5.3.4 结构参数2 (HCSPARAMS2)

Structural Parameters 2 (HCSPARAMS2) 。

地址: Base + (08h)

属性:RO

大小:32 bits

5.3.5 结构参数3 (HCSPARAMS3)

Structural Parameters 3 (HCSPARAMS3) 。

地址: Base + (0Ch)

属性:RO

大小:32 bits

5.3.6 能力参数1 (HCCPARAMS1)

Capability Parameters 1 (HCCPARAMS1) 。

地址: Base + (10h)

属性:RO

大小:32 bits

5.3.7 门铃偏移 (DBOFF)

Doorbell Offset (DBOFF) 。

地址: Base + (14h)

属性:RO

大小:32 bits

此 register 定义 Doorbell Array 基址与 Base 的偏移量。

5.3.8 运行时寄存器空间偏移 (RTSOFF)

Runtime Register Space Offset (RTSOFF) 。

地址: Base + (18h)

属性:RO

大小:32 bits

此 register 定义 xHCI Runtime Registers 与 Base 的偏移量。

5.3.9 功能参数 2 (HCCPARAMS2)

Capability Parameters 2 (HCCPARAMS2) 。

地址: Base + (1Ch)

属性:RO

大小:32 bits

5.3.10 基于虚拟化的可信 IO 寄存器空间偏移 (VTIOSOFF)

Virtualization Based Trusted IO Register Space Offset (VTIOSOFF) 。

地址: Base + (20h)

属性:RO

大小:32 bits

☆

838

838

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?