系列文章目录

XHCI 1.2b 规范摘要(一)

XHCI 1.2b 规范摘要(二)

XHCI 1.2b 规范摘要(三)

XHCI 1.2b 规范摘要(四)

XHCI 1.2b 规范摘要(五)

XHCI 1.2b 规范摘要(六)

XHCI 1.2b 规范摘要(七)

XHCI 1.2b 规范摘要(八)

XHCI 1.2b 规范摘要(九)

XHCI 1.2b 规范摘要(十)

XHCI 1.2b 规范摘要(11)

XHCI 1.2b 规范摘要(12)

XHCI 1.2b 规范摘要(13)

XHCI 1.2b 规范摘要(14)

XHCI 1.2b 规范摘要(15)

文章目录

- 系列文章目录

- 5 寄存器接口(Register Interface)

- 5.4 Host Controller 操作寄存器

- 5.5 Host Controller 运行时寄存器

- 5.6 门铃寄存器(Doorbell Registers)

- 5.7 VTIO 寄存器(VTIO Registers)

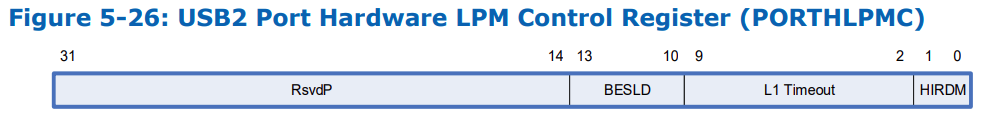

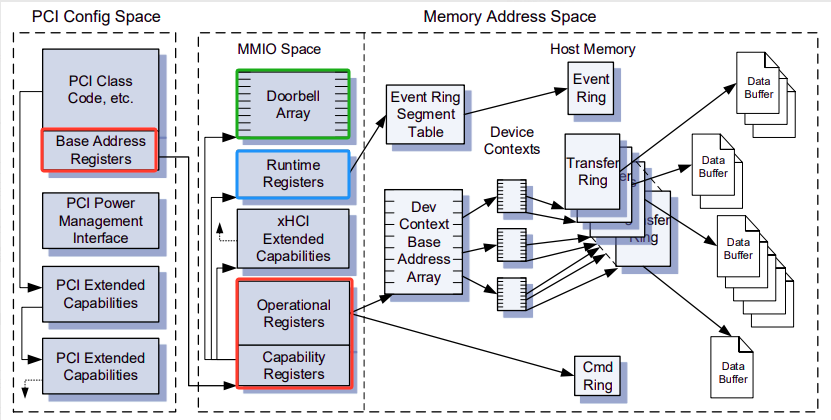

5 寄存器接口(Register Interface)

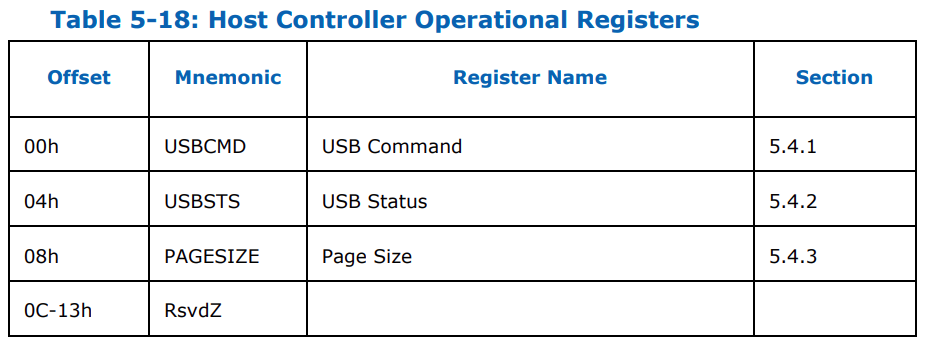

5.4 Host Controller 操作寄存器

Host Controller Operational Registers 。

此寄存器空间的基址称为 Operational Base (操作基地址)。Operational Base 应与 Dword 对齐,并通过将 Capability Registers Length (CAPLENGTH) 寄存器的值(参见第 5.3.1 节)与 Capability Base 地址相加来计算。所有 registers 都是 32 位长度的倍数。

除非另有说明,否则在读取时应使用适当的软件掩码以 32 位宽度访问所有寄存器(如果需要)。应调用软件读取/修改/写入机制进行部分写入。

注意:HCSPARAMS1 寄存器中的 MaxPorts 值定义端口寄存器集的数量(例如,PORTSC、PORTPMSC 和 PORTLI 寄存器集)。PORTSC、PORTPMSC 和 PORTLI 寄存器集是分组的(连续的 Dword)。请参阅其各自的部分以了解其寻址。

表 5-18 中引用的偏移量是从 Operational Register 空间开头的偏移量。

Operational Register 位于功能寄存器(Capabilities Registers)的正偏移处(请参阅第 5.3 节)。

当虚拟功能 (VF) 公开操作寄存器时,VMM 会为所选 VF 提供的 xHC 实例模拟和管理这些寄存器。VMM 可以完全决定写入这些寄存器将如何影响 VF 的操作以及 VF 返回的读取数据的值,但在适当的情况下会提供建议。有关更多信息,请参阅第 8 章。

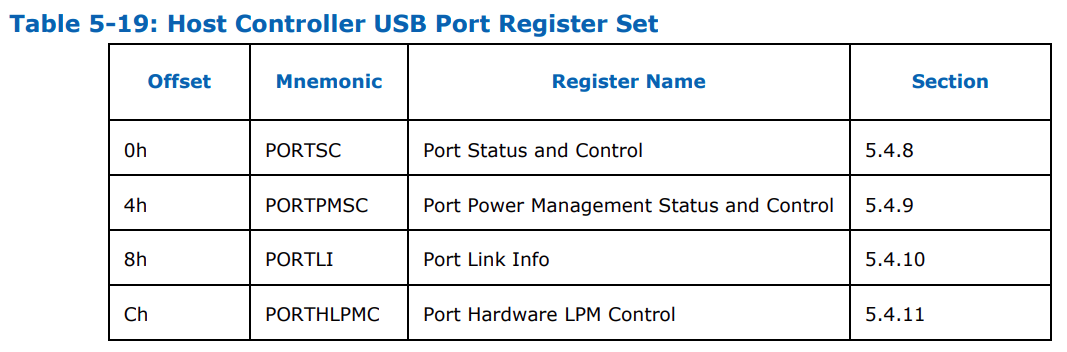

5.4.1 USB 命令寄存器 (USBCMD)

USB Command Register (USBCMD) 。

地址: Operational Base + (00h)

属性:RO, RW (field dependent)

大小:32 bits

Command Register 表示串行总线主控制器要执行的命令。写入 register 会导致执行命令。

5.4.1.1 运行/停止(R/S)

Run/Stop (R/S) 。

软件将 R/S 写入“0” 后,xHC 完成所有当前或排队的命令或 TD(以及与它们相关的 USB 上的任何主机启动事务),然后停止并设置 HCH(HCHalted) = “1”。xHC 停止所需的时间取决于许多因素,但是,如果许多 TD 在传输环上排队,则 xHC 可能需要很长时间才能完成所有未完成的工作并停止。

为了加快 xHC 停止过程,软件应在清除 R/S 位之前确保以下事项:

- 所有端点都处于停止状态或处于运行状态的空闲状态,并且已收到与它们相关的所有传输事件。

- 命令传输环处于停止状态(CRR = “0”)或空闲状态(即命令传输环为空),并且已收到与它们相关的所有命令完成事件。

软件应应用以下规则来确定繁忙传输环何时变为空闲:

- 对于 Isoch 端点:

- 等待环欠载或环超载传输事件,或者,

- 发出停止端点命令并等待相关的命令完成事件。

- 对于非 Isoch 端点:

- 如果在传输环上的最后一个 TRB 中设置了 IOC 标志,则等待其传输事件。

- 如果在传输环上的最后一个 TRB 中未设置 IOC 标志,则当环上的最后一个 TRB 完成时不会生成传输事件,因此软件应发出停止端点命令并等待相关的命令完成事件和停止传输事件。请参阅第 4.6.9 节。

注意:软件应确保在 R/S 清除为 “0” 之前完成 USB2 端口上的任何待处理重置。

注意:xHC 被强制在 16 毫秒内停止。软件将 R/S 位清除为 “0”,而不考虑任何排队传输或命令环活动。如果软件不遵循上述 “暂停过程” 建议,则可能会发生未定义的行为,例如,xHC 命令或待处理的 USB 事务可能会丢失、中止等。

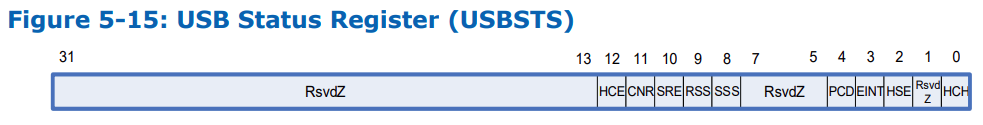

5.4.2 USB 状态寄存器 (USBSTS)

USB Status Register (USBSTS) 。

地址: Operational Base + (04h)

属性:RO, RW, RW1C, (field dependent)

大小:32 bits

该寄存器指示待处理的中断和主机控制器(Host Controller)的各种状态。串行总线上的事务产生的状态未在该寄存器中指示。软件通过向该寄存器写入“1” (RW1C) 来将该位设置为 “0” 。有关 USB 中断条件的更多信息,请参阅第 4.17 节。

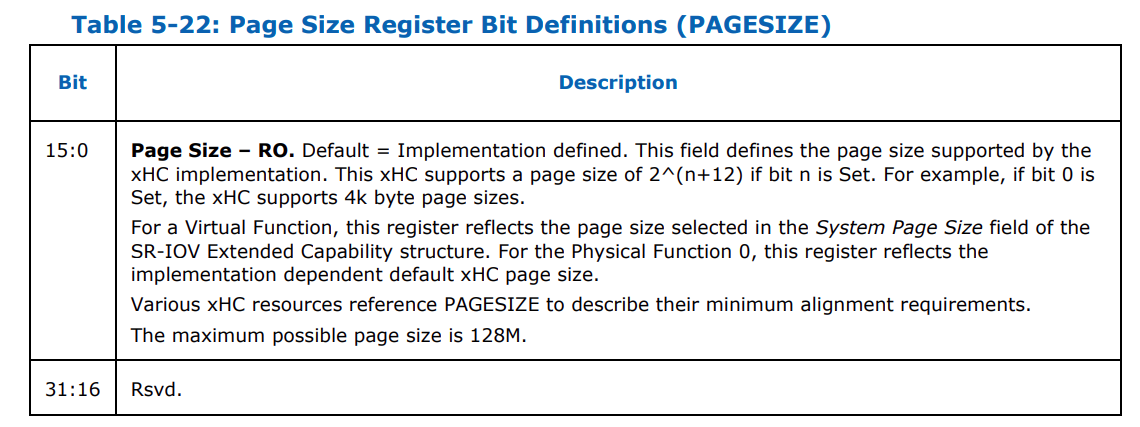

5.4.3 页面大小寄存器 (PAGESIZE)

Page Size Register (PAGESIZE) 。

地址: Operational Base + (08h)

属性:RO

大小:32 bits

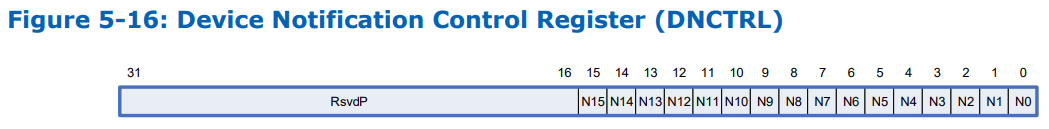

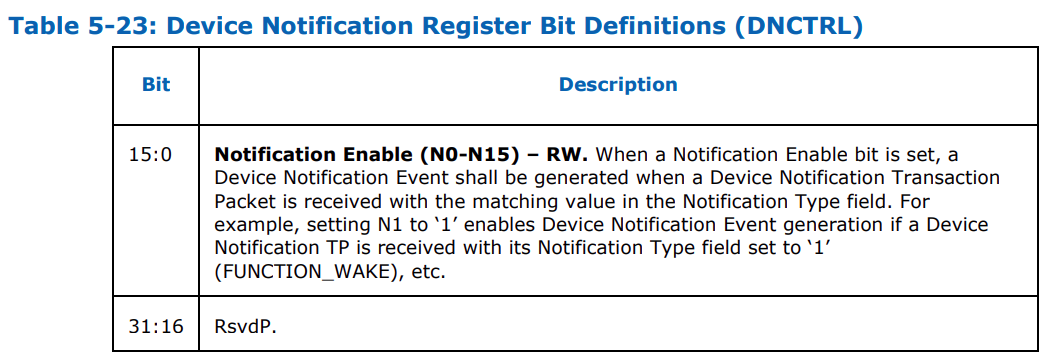

5.4.4 设备通知控制寄存器 (DNCTRL)

Device Notification Control Register (DNCTRL) 。

地址: Operational Base + (14h)

属性:RW (Writes shall be Dword)

大小:32 bits

软件使用此寄存器来启用或禁用特定 USB 设备通知事务包接收的报告(USB Device Notification Transaction Packets)。为 16 种可能的设备通知类型中的每一种都定义了一个通知启用 (Nx,其中 x = 0 至 15) 标志。如果为特定通知类型设置了标志,则在收到相应的通知包时应生成设备通知事件(Device Notification Event)。重置后,所有通知均被禁用。请参阅第 6.4.2.7 节。

此寄存器应写入为 Dword。字节写入会产生未定义的结果。

注意:在当前定义的 USB3 设备通知类型中,只有 FUNCTION_WAKE 类型不应由 xHC 自动处理。只有在调试条件下,软件才会将 DNCTRL 寄存器写入除 0002h 以外的值。有关通知类型的更多信息,请参阅 USB3 规范中的第 8.5.6 节。如果定义了新的设备通知类型,软件可以通过设置相应的通知启用位来接收它们。

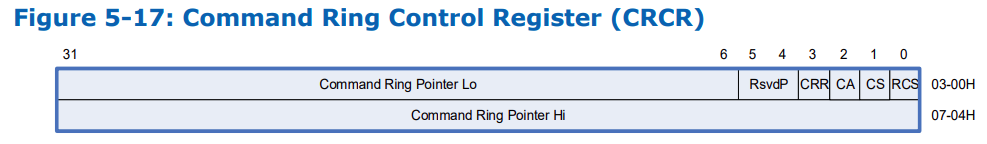

5.4.5 命令环控制寄存器 (CRCR)

Command Ring Control Register (CRCR) 。

地址: Operational Base + (18h)

属性:RW

大小:64 bits

命令环控制寄存器提供命令环(Command Ring)控制和状态功能,并识别命令环出队指针(Command Ring Dequeue Pointer)的地址和循环位(Cycle bit)状态。

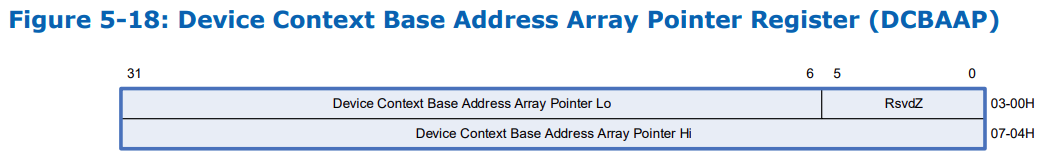

5.4.6 设备上下文基址数组指针寄存器 (DCBAAP)

Device Context Base Address Array Pointer Register (DCBAAP) 。

地址: Operational Base + (30h)

属性:RW

大小:64 bits

设备上下文基地址数组指针寄存器(Device Context Base Address Array Pointer Register)标识 Device Context Base Address Array 。此物理内存指针引用的内存结构假定为物理连续且 64 字节对齐。

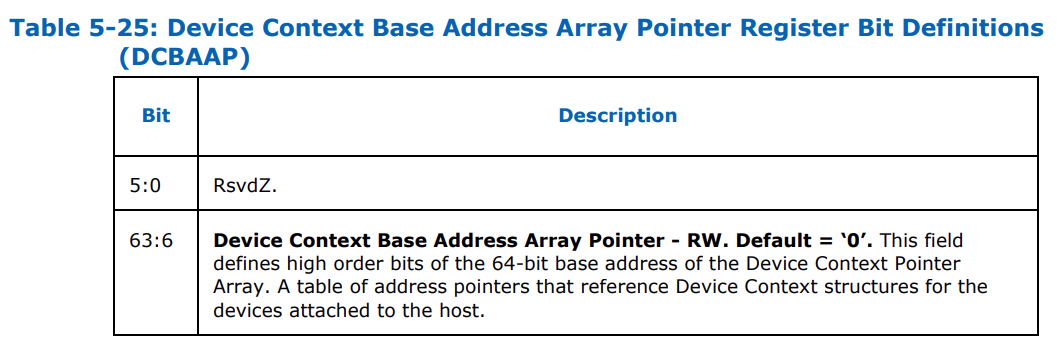

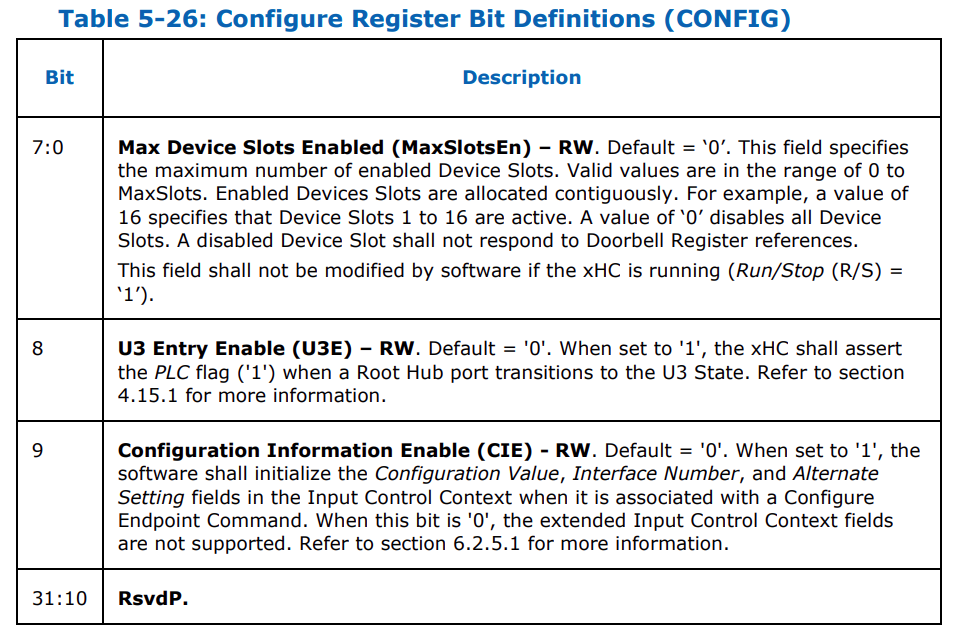

5.4.7 配置寄存器 (CONFIG)

Configure Register (CONFIG) 。

地址: Operational Base + (38h)

属性:RW

大小:32 bits

该寄存器定义运行时(runtime) xHC 配置参数。

注意:将非零值写入最大设备槽启用 (MaxSlotsEn) 字段,向 xHC 发出信号,表示已加载 xHC 的主控制器驱动程序。可以检查 USBCMD 寄存器中的运行/停止 (R/S) 标志,以确定驱动程序是否正在运行。

注意:在不需要支持全部槽( xHC 硬件支持的全部槽)的情况下,最大设备槽启用 (MaxSlotsEn) 字段的值可能允许软件缩减其内存使用量。xHC 还可以使用它来修改内部算法以分配其内部资源,即每个槽有更多的数据缓冲,修改其端点调度算法等。

注意:如果停止 xHC 以减少 MaxSlotsEn 值,软件应确保没有活动设备槽(即未处于禁用状态)被禁用,否则可能会发生未定义的行为。例如,如果 MaxSlotsEn 从 16 更改为 8,则在更改 MaxSlotsEn 之前,设备插槽 9 到 16 应处于禁用状态。

Note: If the xHC is stopped to reduce the MaxSlotsEn value, software shall ensure that no active Device Slots (that is, not in the Disabled state) are being disabled, otherwise undefined behavior may occur. For example, if MaxSlotsEn is being changed from 16 to 8, Device Slots 9 through 16 shall be in the Disabled state before MaxSlotsEn is changed.

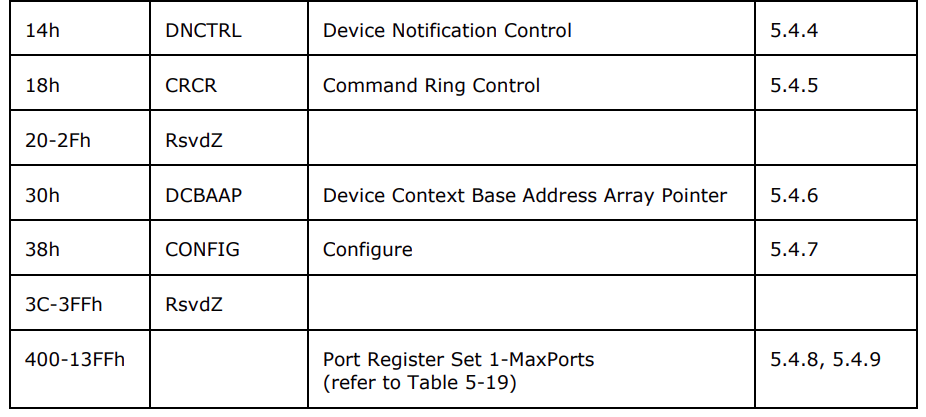

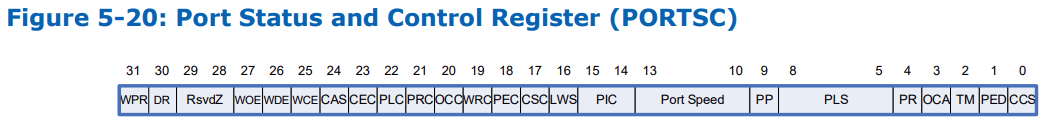

5.4.8 端口状态和控制寄存器 (PORTSC)

Port Status and Control Register (PORTSC) 。

地址: Operational Base + (400h + (10h * (n–1)))

其中:n = 端口号(有效值为 1、2、3、…MaxPorts)

属性:RO、RW、RW1C(取决于现场)

大小:32 bits

主机控制器应实现一个或多个端口寄存器。主机控制器的特定实例实现的端口寄存器数量记录在 HCSPARAMS1 寄存器中(第 5.3.3 节)。软件使用此信息作为输入参数来确定需要服务多少个端口。所有端口都具有下面定义的结构。

此寄存器位于辅助电源井中。它仅在冷复位期间或响应主机控制器复位 (HCRST) 时由平台硬件复位。端口的初始条件在第 4.19 节中描述。

注意:如果 xHC 已停止(HCHalted (HCH) = ‘1’),则无法生成端口状态更改事件。有关更改标志的更多信息,请参阅第 4.19.2 节。

注意:在尝试写入此寄存器之前,软件应确保 xHC 正在运行(HCHalted (HCH) = ‘0’)。

除非端口电源 (PP) 被置位(“1”),否则软件无法更改端口状态,无论端口电源控制 (PPC) 功能如何(第 5.3.6 节)。主机必须在 PP 从“0”转换为“1”后的 20 毫秒内使端口电源稳定。如果 PPC =“1”,则软件负责在置位 PP 后等待 20 毫秒,然后再尝试更改端口状态。

注意:如果已将端口分配给调试功能,则当端口电源标志为 “1” 时,端口不得报告设备已连接(即 CCS =“0”)并已启用。有关 xHCI 调试功能操作的更多信息,请参阅第 7.6 节。

5.4.8.1 USB2 到 USB3 端口状态映射

USB2 to USB3 Port State Mapping 。

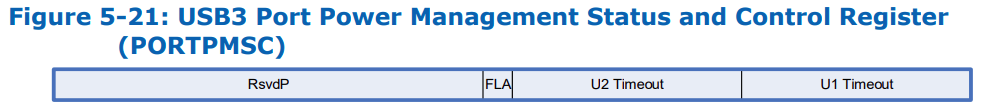

5.4.9 端口 PM 状态和控制寄存器 (PORTPMSC)

Port PM Status and Control Register (PORTPMSC) 。

Port Power Management Status and Control Register (PORTPMSC) 。

地址: Operational Base + (404h + (10h * (n–1)))

其中:n = 端口号(有效值为 1、2、3、…MaxPorts)

属性:RWS

大小:32 bits

PORTPMSC 寄存器中字段的定义取决于端口支持的 USB 协议。

此寄存器位于辅助电源井(Aux Power well)中。它仅在冷复位期间或响应主机控制器复位 (HCRST) 时由平台硬件复位。

5.4.9.1 USB3 协议 PORTPMSC 定义

USB3 Protocol PORTPMSC Definition 。

USB3 端口电源管理状态(Port Power Management Status)和控制(Control)寄存器控制增强型超高速(Enhanced SuperSpeed) USB 链路 U-State 超时。有关链路电源管理的更多信息,请参阅 USB3 规范的第 11 节。

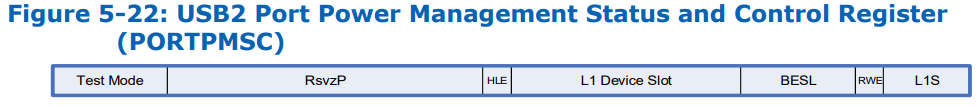

5.4.9.2 USB2 协议 PORTPMSC 定义

USB2 Protocol PORTPMSC Definition 。

USB2 端口电源管理状态和控制寄存器提供 xHC 生成 LPM 令牌给下游设备所需的 USB2 LPM 参数。有关 xHCI 链路电源管理功能的更多信息,请参阅第 4.23.5.1 节。有关 USB2 链路电源管理的更多信息,请参阅 USB2 LPM ECR。

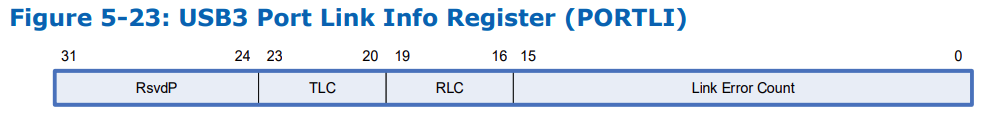

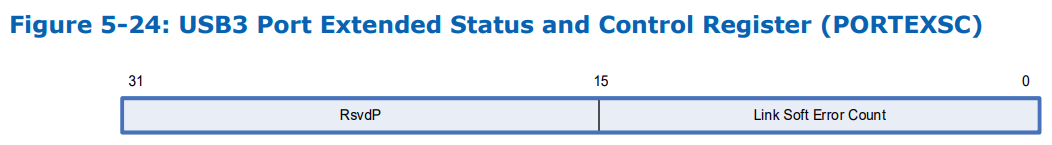

5.4.10 端口链路信息寄存器 (PORTLI)

Port Link Info Register (PORTLI) 。

地址: Operational Base + (408h + (10h * (n–1)))

其中:n = 端口号(有效值为 1、2、3、…MaxPorts)

属性:RO

大小:32 bits

PORTLI 寄存器中字段的定义取决于端口支持的 USB 协议。

5.4.10.1 USB3 协议 PORTLI 定义

USB3 Protocol PORTLI Definition 。

USB3 端口链路信息(Port Link Info)寄存器报告链路错误计数。有关链路错误计数报告的更多信息,请参阅 USB3 规范的第 10.14.2.5 节。

5.4.10.2 USB2 协议 PORTLI 定义

USB2 Protocol PORTLI Definition 。

USB2 Port Link Info 寄存器是保留的,应被软件视为 RsvdP。

5.4.11 端口硬件 LPM 控制寄存器 (PORTHLPMC)

Port Hardware LPM Control Register (PORTHLPMC) 。

地址: Operational Base + (40Ch + (10h * (n–1)))

其中:n = 端口号(有效值为 1、2、3、…MaxPorts)

属性:RWS

大小:32 bits

PORTHLPMC 寄存器中字段的定义取决于端口支持的 USB 协议。

此寄存器位于辅助电源井(Aux Power well)中。它仅在冷复位期间或响应主机控制器复位 (HCRST) 时由平台硬件复位。

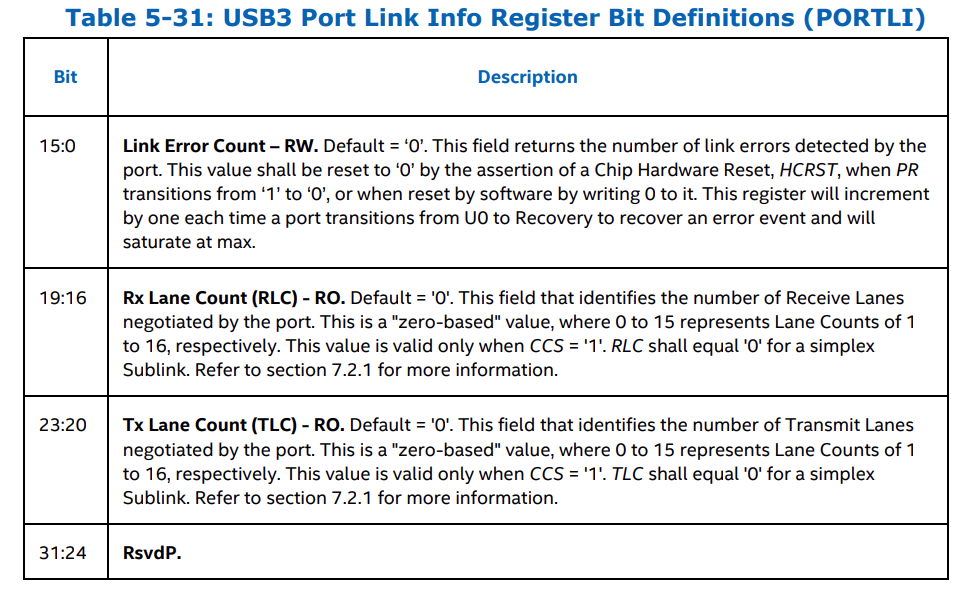

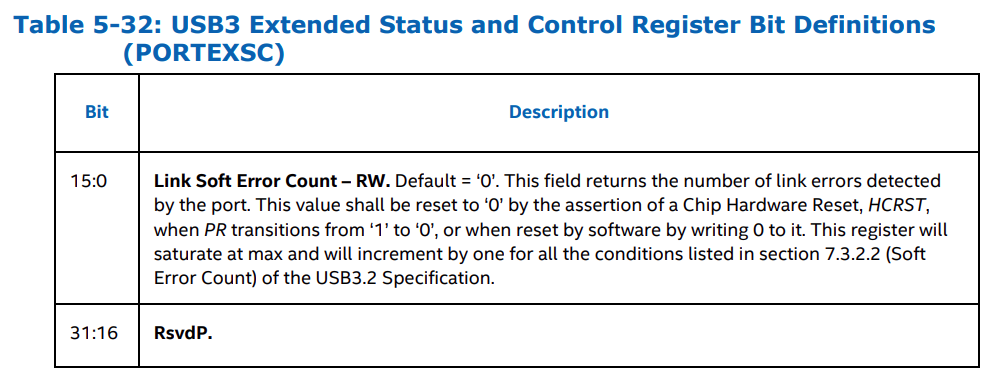

5.4.11.1 USB3 协议 PORTEXSC 定义

USB3 Protocol PORTEXSC Definition 。

USB3 端口扩展状态(Port extended status)和控制(control)寄存器根据 USB3.1 和 USB3.2 规范定义,为单个端口提供软错误。如果 XHCI 控制器不支持链路软错误(LSECC = 0),则该寄存器将被保留。

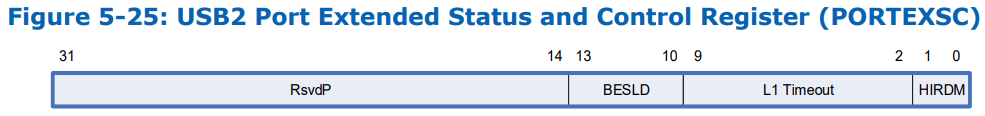

5.4.11.2 USB2 协议 PORTEXSC 定义

USB2 Protocol PORTEXSC Definition 。

可选的规范性 USB2 端口 PORTEXSC 寄存器提供 xHC 自动生成 LPM 令牌给下游设备所需的 USB2 LPM 参数。如果不支持 LPM(HLC = ‘0’),则此寄存器被保留。有关更多信息,请参阅第 4.23.5.1.1.1 节。

5.4.11.3 USB3 协议 PORTHLPMC 定义

USB3 Protocol PORTHLPMC Definition 。

USB3 Protocol Port Hardware LPM Control Register Definition 。

USB3 端口硬件 LPM 控制寄存器被保留,并应由软件视为 RsvdP。

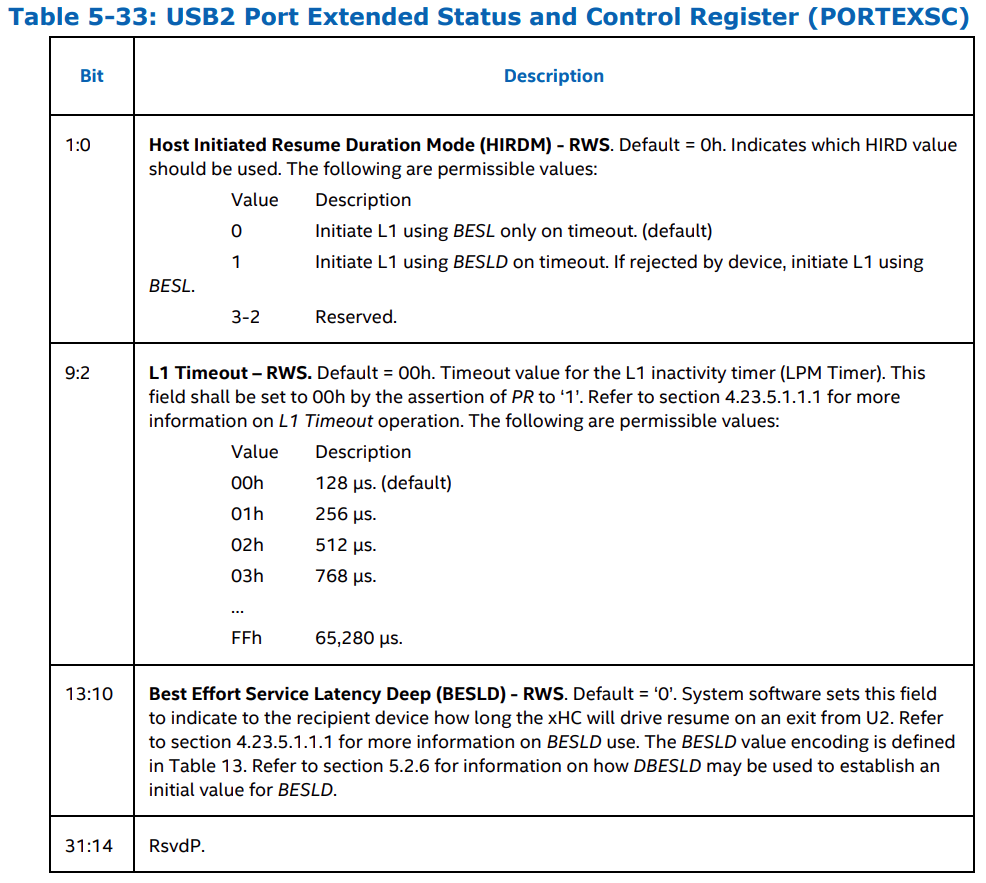

5.4.11.4 USB2 协议 PORTHLPMC 定义

USB2 Protocol PORTHLPMC Definition 。

USB2 Protocol Port Hardware LPM Control Register Definition 。

可选的规范性 USB2 端口硬件 LPM 控制寄存器提供 xHC 自动生成 LPM 令牌给下游设备所需的 USB2 LPM 参数。如果不支持 LPM(HLC = ‘0’),则此寄存器被保留。有关更多信息,请参阅第 4.23.5.1.1.1 节。

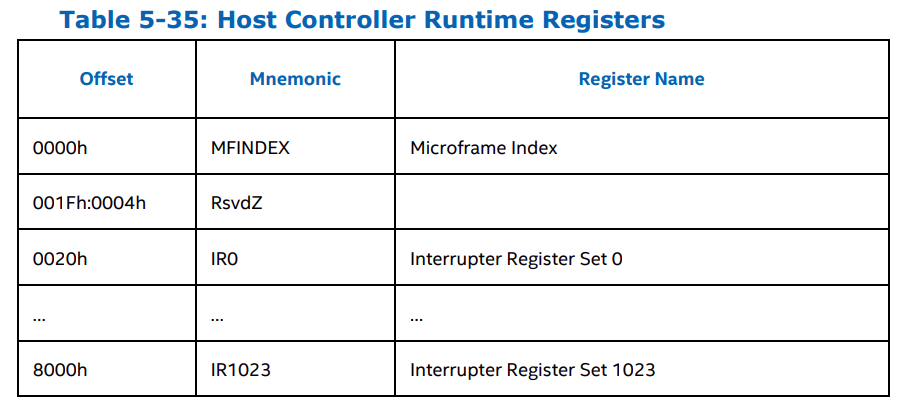

5.5 Host Controller 运行时寄存器

Host Controller Runtime Registers 。

本节定义 xHCI 运行时(Runtime)寄存器空间。此寄存器空间的基地址称为运行时基地址( Runtime Base )。运行时基地址应为 32 字节对齐,计算方法是将 Runtime Register Space Offset 寄存器的值(参见第 5.3.8 节)添加到 Capability Base 地址。所有运行时寄存器的长度均为 32 位的倍数。

除非另有说明,否则所有寄存器都应在读取时使用 Dword 引用进行访问,并在需要时使用适当的软件掩码。应调用软件读取/修改/写入机制进行部分写入。

软件应仅使用 Qword 引用写入包含 Qword 地址字段的寄存器。如果系统无法发出 Qword 引用,则应使用 2 个 Dword 引用对 Qword 地址字段进行写入;低 Dword 优先,高 Dword 其次。

表 5-35 中引用的 Offset 是从 Runtime Register 空间开头的偏移量。

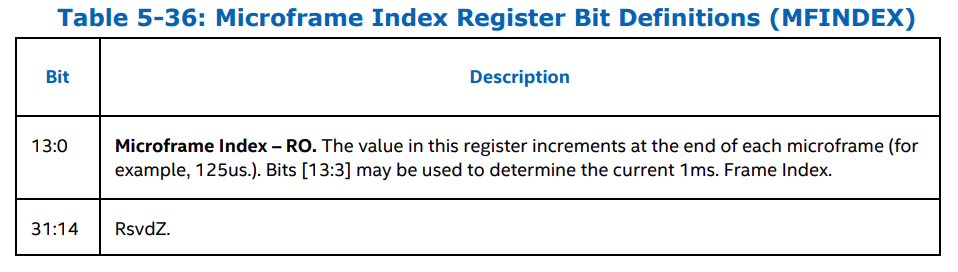

5.5.1 微帧索引寄存器 (MFINDEX)

Microframe Index Register (MFINDEX) 。

地址: Runtime Base

属性:RO

大小:32 bits

系统软件使用此寄存器来确定当前周期帧。寄存器值每 125 微秒递增一次(每个微帧一次)。仅当运行/停止 (R/S) = “1” 时,此寄存器才会递增。

此寄存器的值会影响 USB2 总线实例生成的 SOF 值。有关详细信息,请参阅第 4.14.2 节。另请参见图 4-21。

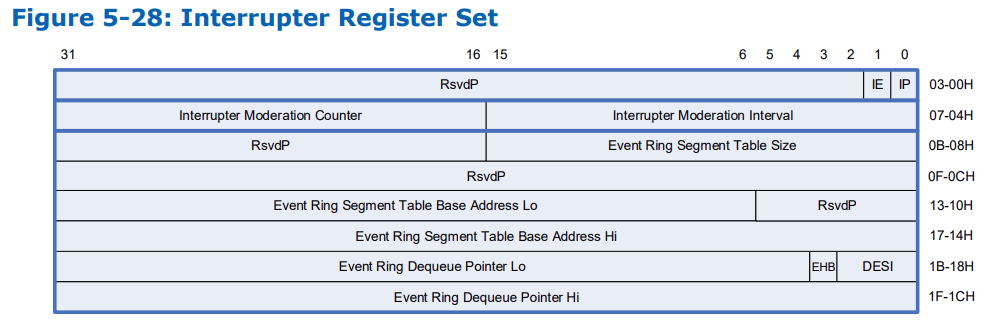

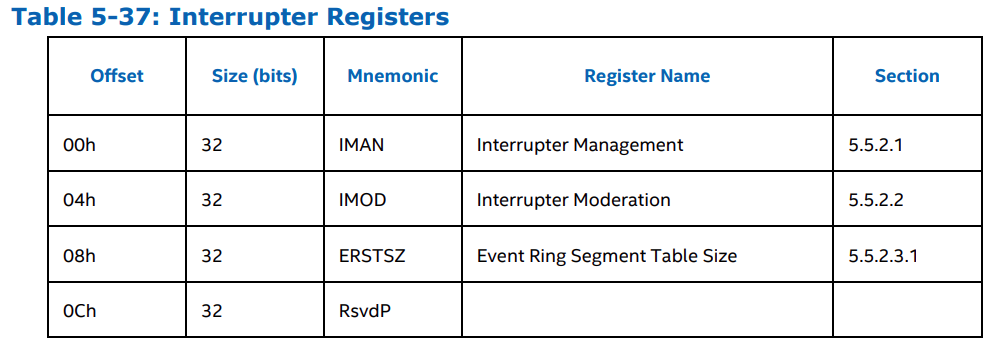

5.5.2 中断寄存器设置(Interrupter Register Set)

中断器逻辑由 Interrupter Management Register(中断器管理寄存器)、Interrupter Moderation Register (中断器调节寄存器)和 Event Ring Registers (事件环寄存器)组成。中断器与 MSI-X 向量之间定义一对一映射。最多支持 1024 个中断器。

有关主中断器和次级中断器和事件环的讨论,请参阅第 4.9.4.3 节。

注意:在将 USBCMD 寄存器中的运行/停止 (RS) 标志设置为 “1” 之前,应初始化主中断器的所有寄存器。辅助中断器可以在 RS = “1” 后初始化,但是所有辅助中断器寄存器都应在生成针对它们的事件之前初始化。不遵守这些规则将导致未定义的 xHC 行为。

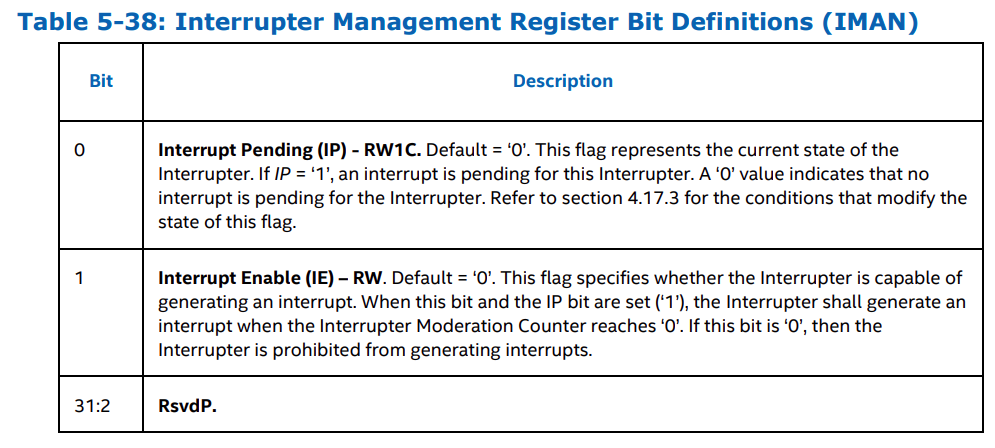

5.5.2.1 中断者管理寄存器(IMAN)

Interrupter Management Register (IMAN) 。

地址: Runtime Base + 020h + (32 * Interrupter)

其中:Interrupter 为 0, 1, 2, 3, …1023

属性:RW

大小:32 bits

Interrupter Management 寄存器允许系统软件启用、禁用和检测 xHC 中断。

注意:在不支持 MSI 或 MSI-X 的系统中,可以通过向 IP 位写入 “1” 来清除该位。大多数系统都有写入缓冲区以尽量减少开销,但这可能需要读取操作来保证写入已从已发布的缓冲区中刷新。有关更多信息,请参阅第 4.17.2 节。

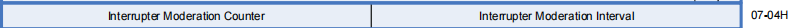

5.5.2.2 中断器调节寄存器 (IMOD)

Interrupter Moderation Register (IMOD) 。

地址: Runtime Base + 024h + (32 * Interrupter)

其中:Interrupter 为 0, 1, 2, 3, …1023

属性:RW

大小:32 bits

Interrupter Moderation Register 控制 Interrupter 的 “中断调节” 功能,允许系统软件限制 xHC 生成的中断速率。

软件可以使用此寄存器来调整(或均衡)向主机 CPU 发送中断的速度。无论 USB 流量状况如何,此寄存器都可以保证 xHC 发出的中断之间的中断间延迟。为了独立验证配置设置,软件可以使用以下算法将中断间间隔值转换为常见的“中断/秒”性能指标:

i n t e r r u p t s / s e c = 1 / ( 250 × 1 0 − 9 s e c × I n t e r v a l ) interrupts/sec = 1/(250×10^{-9}sec × Interval) interrupts/sec=1/(250×10−9sec×Interval)

例如,如果间隔设置为 500,则 xHC 可保证 CPU 在上次中断后的 125 微秒内不会被中断。xHC 的最大可观察中断率不应超过每秒 8000 次中断。

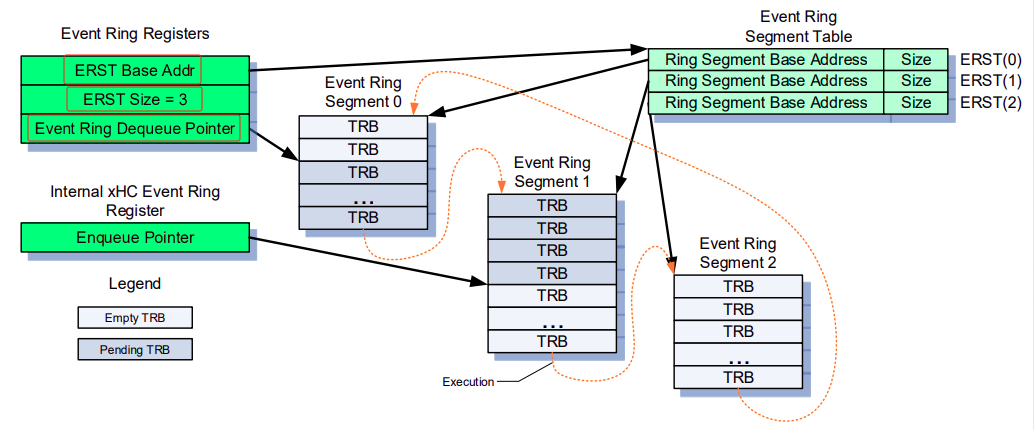

5.5.2.3 事件环寄存器(Event Ring Registers)

有关事件环管理的更多信息,请参阅第 4.9.4 节。有关事件环段表及其条目的更多信息,请参阅第 6.5 节。

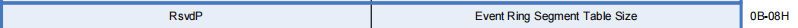

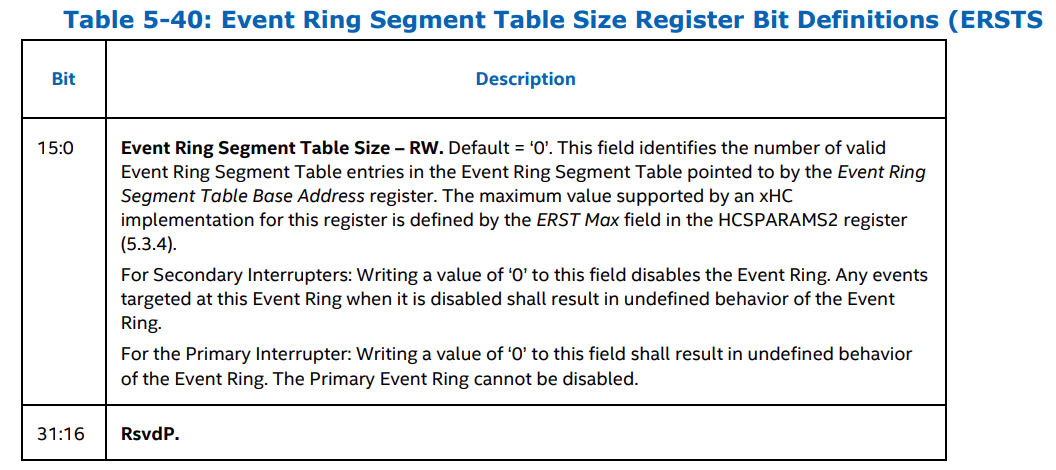

5.5.2.3.1 事件环段表大小寄存器 (ERSTSZ)

Event Ring Segment Table Size Register (ERSTSZ) 。

地址: Runtime Base + 028h + (32 * Interrupter)

其中:Interrupter 为 0, 1, 2, 3, …1023

属性:RW

大小:32 bits

Event Ring Segment Table Size Register 定义 Event Ring Segment Table 支持的段数。

注意:事件环段表大小可以设置为最大为 ERST Max 的任意值,但是软件应为事件环段表分配一个缓冲区,并将其大小四舍五入到最接近的 64B 边界,以允许完整的缓存行访问。

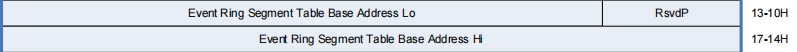

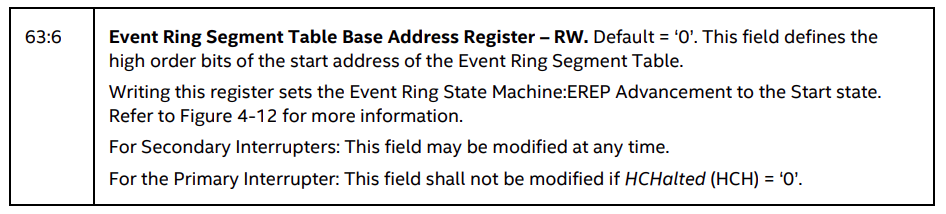

5.5.2.3.2 事件环段表基址寄存器 (ERSTBA)

Event Ring Segment Table Base Address Register (ERSTBA) 。

地址: Runtime Base + 030h + (32 * Interrupter)

其中:Interrupter 为 0, 1, 2, 3, …1023

属性:RW

大小:64 bits

事件环段表基地址寄存器标识事件环段表 (ERST) 的起始地址。有关 ERST 条目的定义,请参阅第 6.5 节。

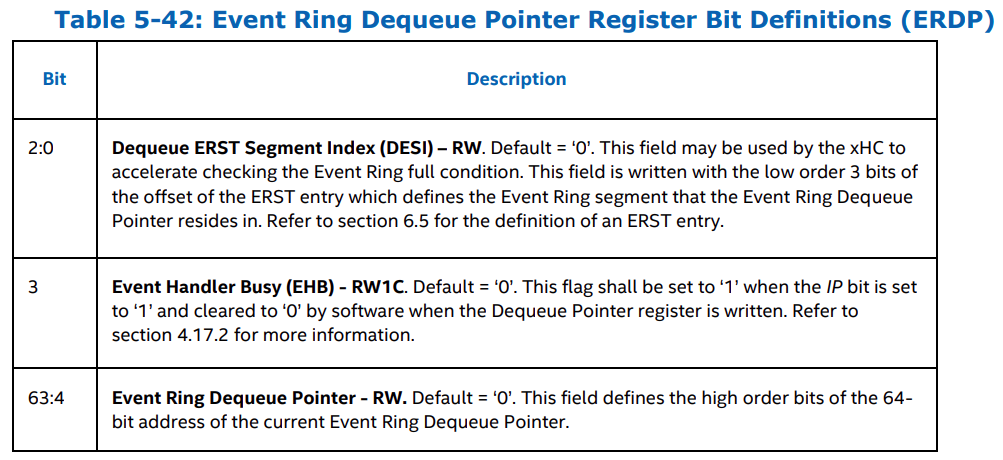

5.5.2.3.3 事件环出队指针寄存器 (ERDP)

Event Ring Dequeue Pointer Register (ERDP) 。

地址: Runtime Base + 038h + (32 * Interrupter)

其中:Interrupter 为 0, 1, 2, 3, …1023

属性:RW

大小:64 bits

事件环出队指针寄存器(Event Ring Dequeue Pointer Register)由软件写入,用于定义事件环出队指针在 xHC 中的位置。当软件完成对事件环上事件的评估时,它会更新此指针。

出队 ERST 段索引 (DESI) 用法:当软件完成处理事件 TRB 时,它会将该事件 TRB 的地址写入 ERDP。在将事件入队之前,xHC 应检查事件环上是否有可用空间。如果 xHC 当前正在将事件 TRB 入队到与软件用于出队事件的 ERST 段不同的 ERST 段中,则可以跳过此检查。

为了实现此优化,软件在写入 ERDP 时,通过使用 ERDP 所在段的索引的低位写入出队 ERST 段索引 (DESI),向 xHC 提供提示。xHC 可以将此值与入队指针的 ERST 段索引进行比较,以确定是否应检查事件环已满情况。

例如,假设一个定义了多个段 (ERSTSZ > 1) 的 ERST,并且软件正在 ERST 的第一个段中出队事件 TRB。在这种情况下,出队 ERST 段索引 (DESI) 字段应写入值“0”(即相关事件环段表条目数据结构的索引)。如果出队指针引用第二个段中的事件 TRB,则出队 ERST 段索引 (DESI) 字段应写入值“1”,依此类推。

注意:如果 ERSTSZ > 8,则出队 ERST 段索引 (DESI) 应提供实际写入的 ERST 段的别名。例如,ERST 段索引 (2:0)。

注意:除非事件环从 FULL 推进到 EMPTY,否则软件不得连续写入相同值的 ERDP。

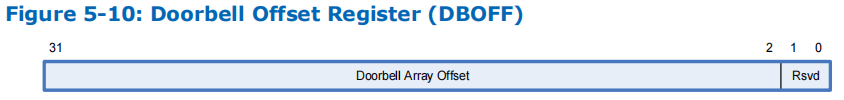

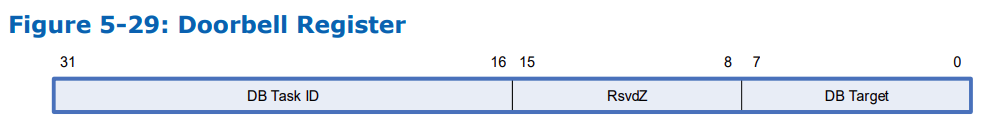

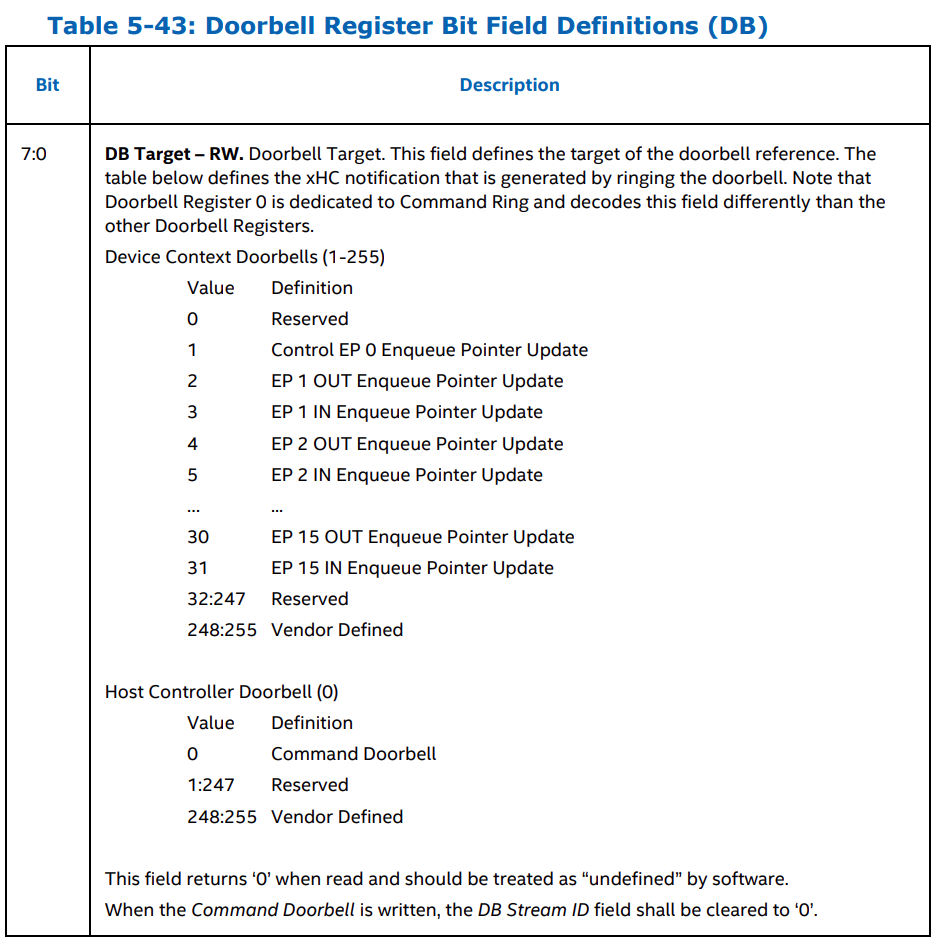

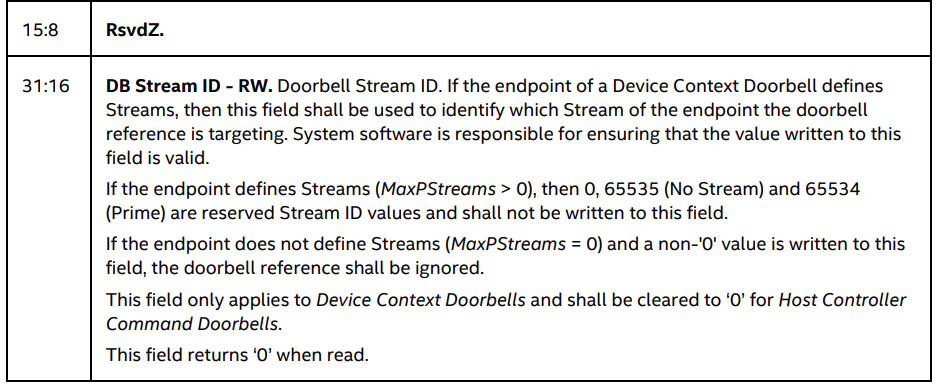

5.6 门铃寄存器(Doorbell Registers)

这些寄存器由 xHC 功能寄存器空间中的 Doorbell Offset Register (DBOFF) 指向。门铃阵列基址应与 Dword 对齐,计算方法是将 DBOFF 寄存器(第 5.3.7 节)中的值与 “Base”( xHCI 功能寄存器地址空间的基址)相加。

门铃阵列被组织为一个最多包含 256 个门铃寄存器的阵列。阵列中为每个设备槽( Device Slot)定义了一个 32 位门铃寄存器。系统软件利用门铃寄存器通知 xHC 它有与设备槽相关的工作需要 xHC 执行。

主机控制器特定实例实现的门铃寄存器数量记录在 HCSPARAMS1 寄存器的设备槽数量 (MaxSlots) 字段中(第 5.3.3 节)。

这些寄存器由 xHC 功能寄存器空间中的 Doorbell Offset Register (DBOFF,门铃偏移寄存器) 指向。门铃阵列基址应为 Dword 对齐,通过将 DBOFF 寄存器中的值(第 5.3.7 节)与 “Base”(xHCI 功能寄存器地址空间的基址)地址相加来计算。有关门铃寄存器的更多信息,请参阅第 4.7 节。

注意:软件只有在为端点发出配置端点命令(Configure Endpoint Command)并收到成功的命令完成事件(Command Completion Event)后,才能写入端点的门铃。

注意:如果支持虚拟化,xHC 实现应确保无效值不会影响其他功能(VFx 的 PF0)。

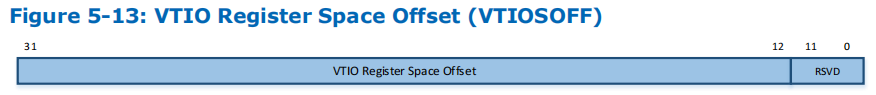

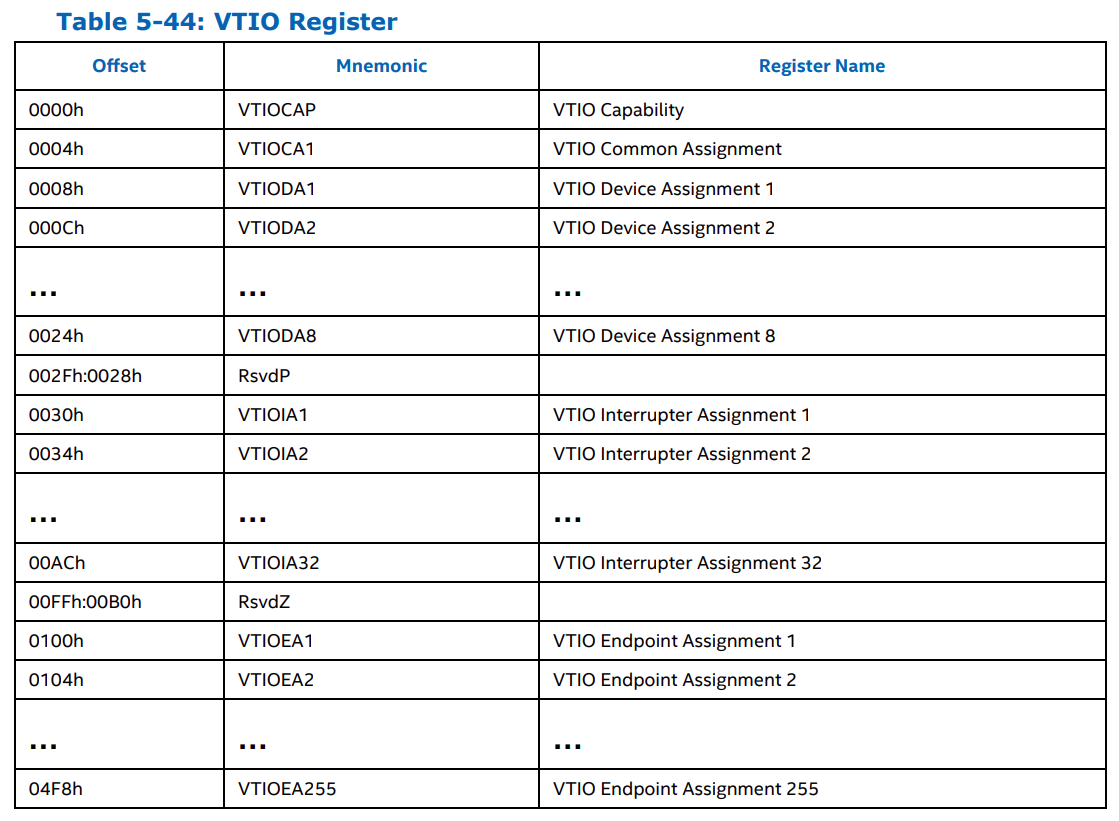

5.7 VTIO 寄存器(VTIO Registers)

本节定义 xHCI VTIO 寄存器空间。此寄存器空间的基址称为 VTIO Base 。VTIO Base 应与 D-word 对齐,计算方法是将 VTIO Register Space Offset 的值(参见第 5.3.10 节)与 Capability Base 地址相加。所有 VTIO 寄存器的长度都是 D-word 的倍数。

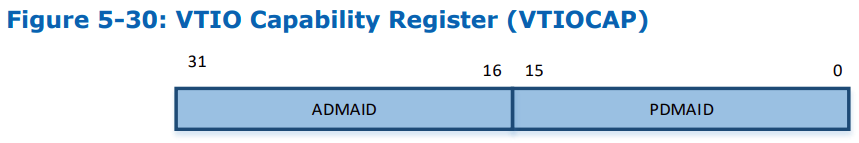

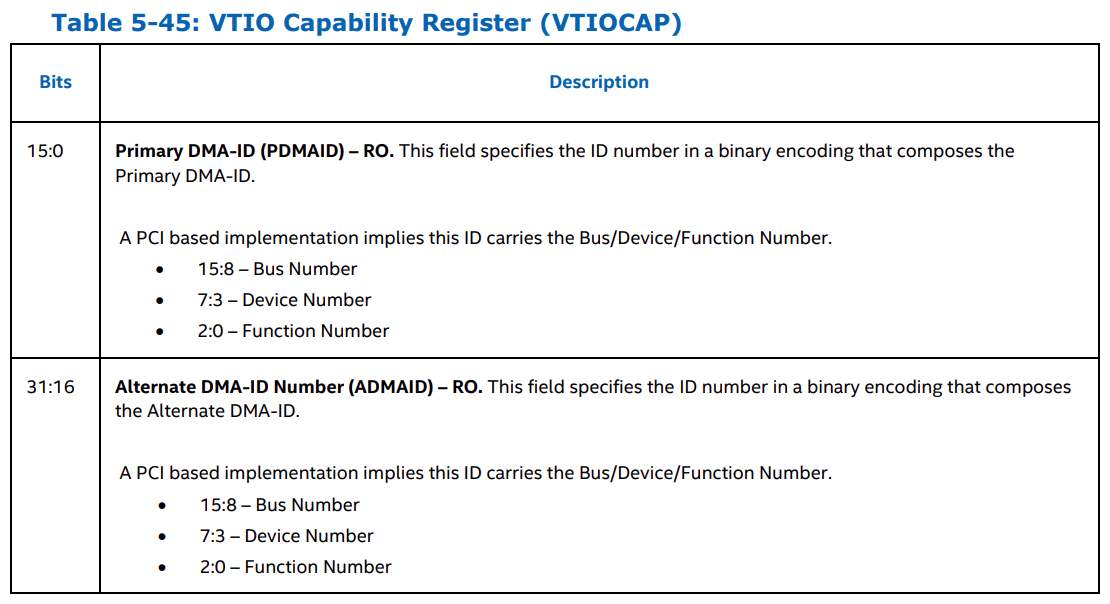

5.7.1 VTIO 功能寄存器 (VTIOCAP)

VTIO Capability Register (VTIOCAP) 。

地址: VTIO Base + 00h

属性:RO

大小:32 bits

系统软件使用此寄存器来确定 Primary 和 Alternate Bus、Device 和 Function 编号。

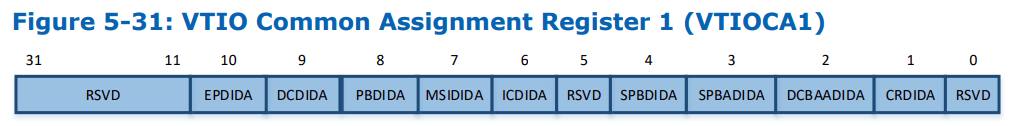

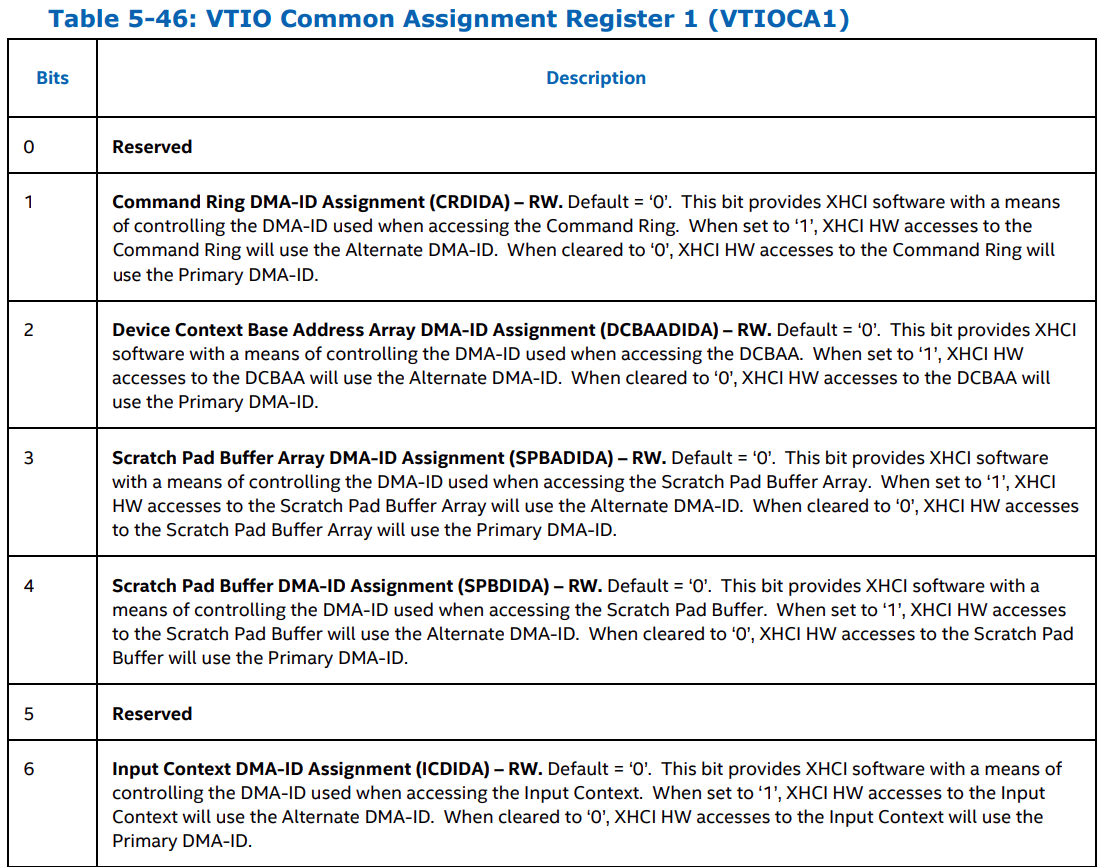

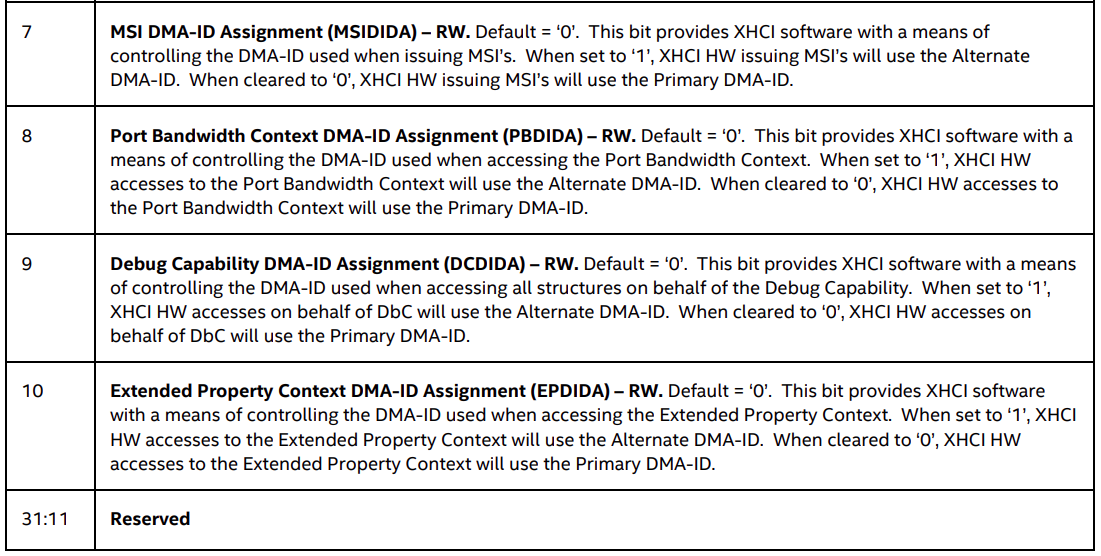

5.7.2 VTIO 公共分配寄存器 1 (VTIOCA1)

VTIO Common Assignment Register 1 (VTIOCA1) 。

地址: VTIO Base + 04h

属性:RW

大小:32 bits

系统软件使用此寄存器来确定 Primary 和 Alternate Bus、Device 和 Function 编号。

此寄存器位于辅助电源井(Aux Power well)中。它仅在冷复位期间或响应主机控制器复位 (HCRST) 时由平台硬件复位。端口的初始条件在第 4.19 节中描述。

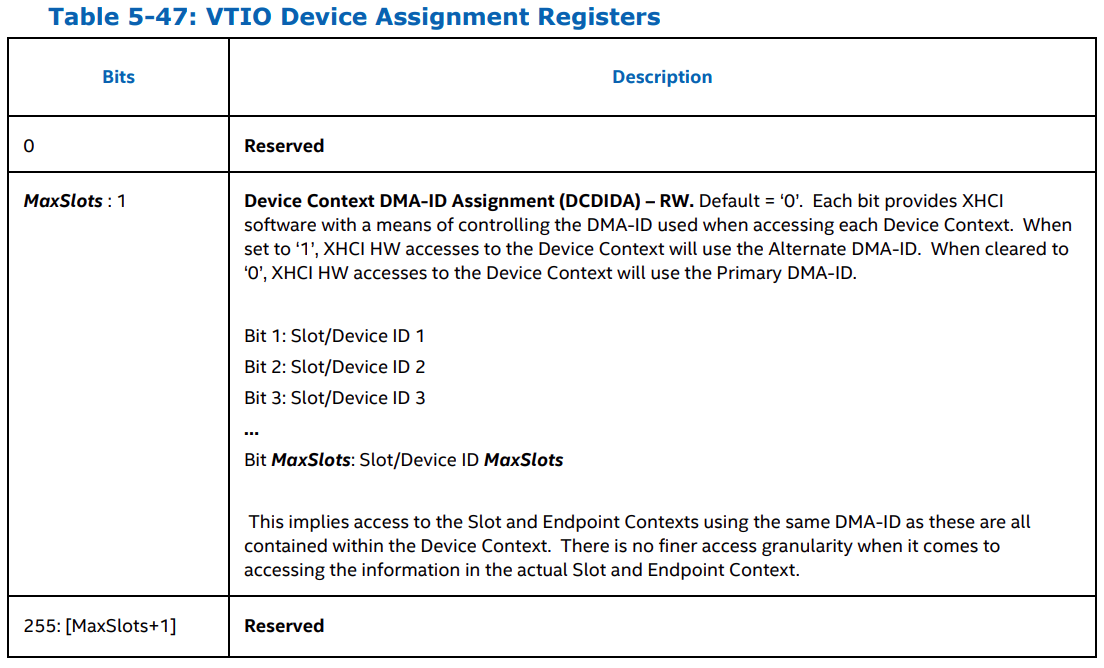

5.7.3 VTIO 器件分配寄存器 1 至 8 (VTIODA{1…8})

VTIO Device Assignment Registers 1 to 8 (VTIODA{1…8}) 。

地址: VTIO Base + 08h

属性:RW

大小:256 bits (8 32b registers)

该寄存器阵列被组织为最多八个 32b 寄存器的阵列。每个位在阵列中针对每个设备上下文定义,最多可达 MaxSlots。系统软件利用此阵列为每个设备分配备用功能编号,以便访问每个设备特定的结构,例如设备上下文。

该寄存器位于核心电源井中。它仅在冷复位期间或响应主机控制器复位 (HCRST) 时由平台硬件复位。端口的初始条件在第 4.19 节中描述。

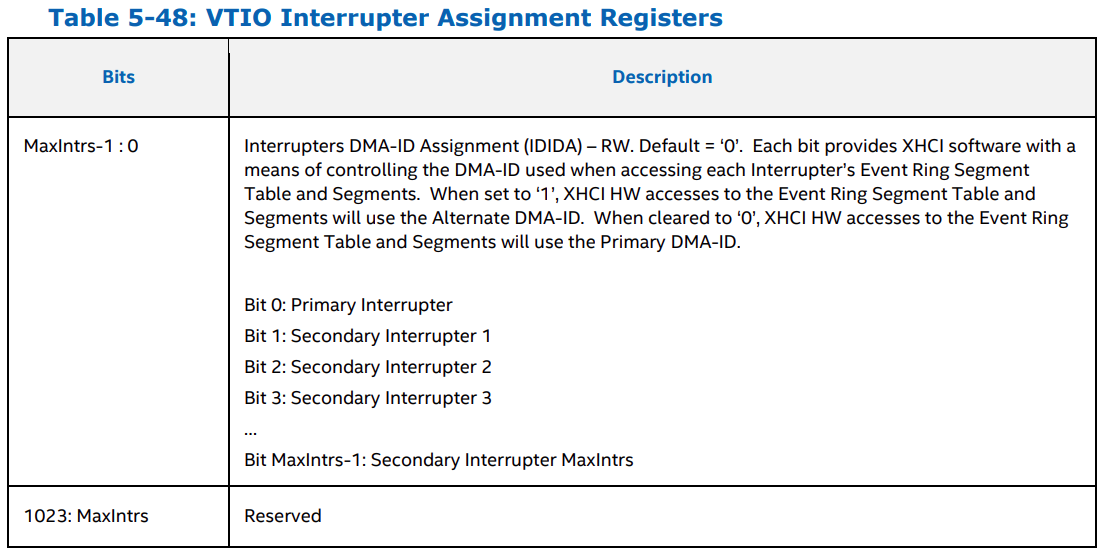

5.7.4 VTIO 中断分配寄存器 1 至 32 (VTIOIA{1…32})

VTIO Interrupter Assignment Registers 1 to 32 (VTIOIA{1…32}) 。

地址: VTIO Base + 30h

属性:RW

大小:1024 bits (32 32b registers)

该寄存器阵列被组织为最多 32 个 32b 寄存器的阵列。每个中断器的每个位在阵列中定义,最多为 MaxIntrs。系统软件利用此阵列为每个中断器分配备用功能编号,以访问每个中断器的事件环段表和段结构。

该寄存器位于核心电源井中。它仅在冷复位期间或响应主机控制器复位 (HCRST) 时由平台硬件复位。端口的初始条件在第 4.19 节中描述。

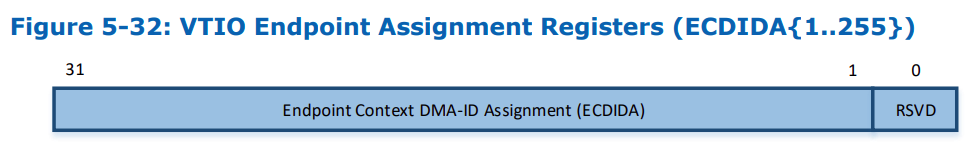

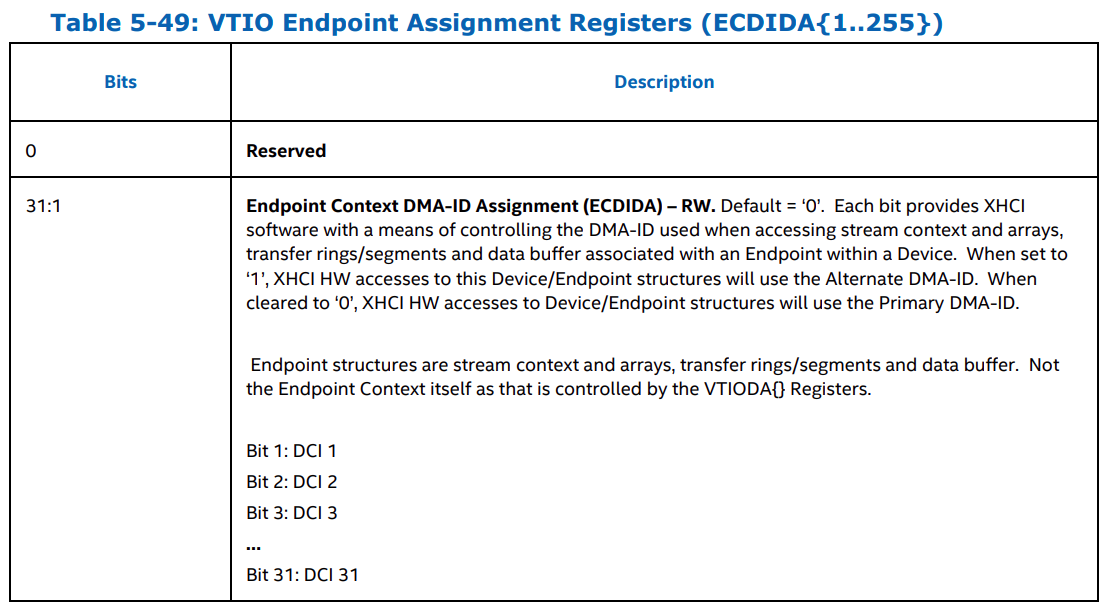

5.7.5 VTIO 端点分配寄存器 1 至 255 (VTIOEA{1…255})

VTIO Endpoint Assignment Registers 1 to 255 (VTIOEA{1…255}) 。

地址: VTIO Base + 100h + (04h * Device)

其中:Device 为 0, 1, 2, …MaxSlots-1 (最大插槽数-1)

属性:RW

大小:32 bits

该寄存器阵列被组织为一个最多包含 255 个 32b 寄存器的阵列。每个寄存器代表与设备/插槽关联的端点。32b 寄存器中的每个位都针对每个设备的每个端点结构定义,最多可达 MaxSlots。系统软件利用此阵列为每个端点分配备用 DMA-ID 编号,以便访问每个端点特定的结构,例如流上下文和数组、传输环/段和数据缓冲区。

该寄存器位于核心电源井中。它仅在冷复位期间或响应主机控制器复位 (HCRST) 时由平台硬件复位。端口的初始条件在第 4.19 节中描述。

☆

935

935

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?