前言

低压(110kV - 10kV)电力保护测控设备主要用于监测和保护低压电力系统(配电系统),确保其安全、稳定运行。近年来,随着配电网的不断进步及智能化水平的显著提升,低压电力保护测控设备市场迎来了快速发展。相较于高压电力设备,低压电力保护测控设备在技术门槛和市场准入方面要求相对较低,吸引了越来越多的企业进入该领域,导致市场竞争日益激烈。在这种背景下,为了保持产品的竞争力,企业不仅需要高度重视产品质量,还要严格控制成本。同时,由于近年来各行业对芯片的需求急剧增加,尤其是在新能源汽车、智能家居、工业自动化等领域的飞速发展,导致了芯片供应日益紧张,而国际关系、贸易摩擦等因素,又进一步加剧了芯片供应链的不确定性,特别是国外厂商芯片的供应,主控芯片的供货问题已成为产品研发生产过程中一大困难点。考虑上述因素,目前不少设备厂都加大国产化芯片的适配和使用。因此,我们在开发中,选择了瑞芯微的RV1106芯片,进行了开发平台的设计。

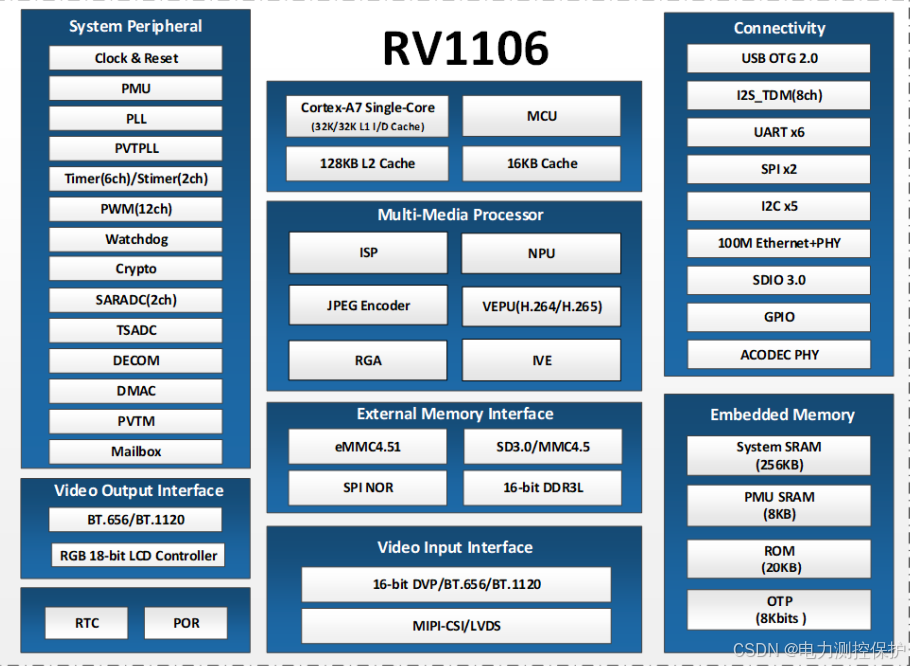

RV1106芯片简介

瑞芯微(rockchip)生产的RV1106G3芯片,其单核cortex-a7,最高主频1.2G, 另有riscv mcu 和 1TOPS 处理性能的NPU,内置128-256M DDR3内存,工作温度范围-40 ~ +125℃,售价约人民币35元。

RV1106处理器架构:

RV1106的SOC资源以及性能可满足低压电力保护测控设备需求,并且价格相对低廉,在成本上具有优势。

RV1106开发平台设计

平台资源与性能

针对低压电力保护测控设备需求,对RV1106外设功能分配如下:

| 外设 | 功能 |

| Cortex-A7 | 运行RTOS,实现主要的保护测控功能 |

| MCU | 开关量去抖采集,LED灯驱动等慢速IO处理 |

| FSPI | AD转换器数据采集 |

| PWM | 系统tick中断,触发AD转换,时间同步时间戳 |

| SDMMC0 | 固件存储以及系统闪存盘 |

| RTC | 实时时钟 |

| WDT | 设备看门狗 |

| UART | 调试串口,通讯管理串口 |

| GMAC | 100M网口 |

| USB2.0 | 扩展网口以4G模块接口 |

| SPI | 铁电存储器,DI/LED多路驱动 |

最终完成的主板可作为1个功能完善的测控保护设备开发平台,具有如下性能:

| 项目 | 描述 |

| 模拟采集 | 2片AD7606B,16通道;需要时可以扩展为32路 4000点/S(80点/周波) |

| 开关量输入 | 最大160路 |

| 开关量输出 | 14路,含2路启动继电器 |

| 10/100网口 | 3个,RV1106G3自带的GMAC支持GOOSE 收发 另外2个用USB 转以太网芯片实现 |

| 存储容量 | 内存256M, 闪存512M(可以上4G-16G) |

| 液晶面板 | 占用1个串口 |

| 串口 | 调试串口,4个通讯管理串口 |

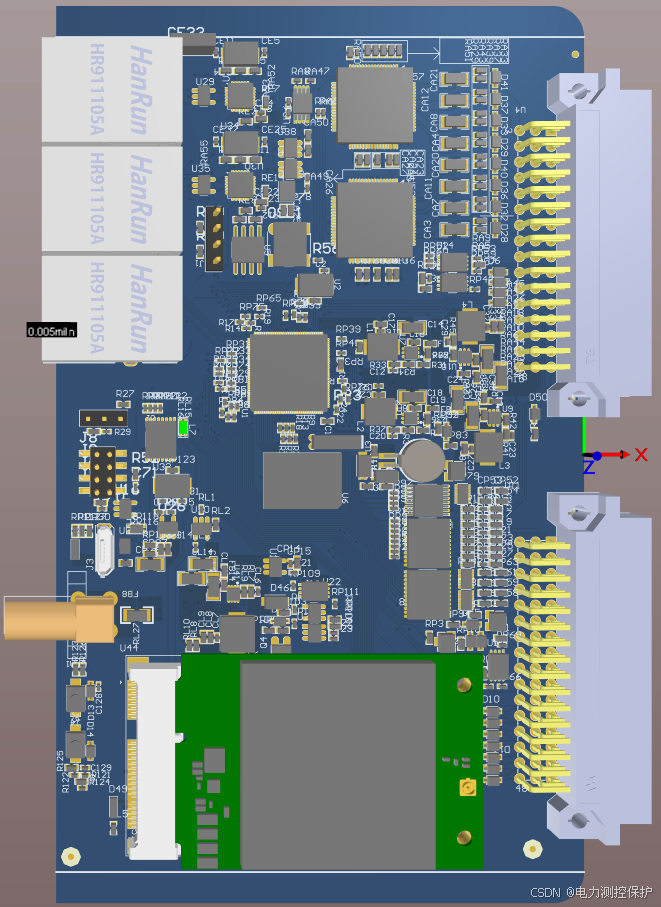

测控保护设备开发平台3D图:

平台软硬件设计中的困难点

为节省成本,依靠 RV1106G3 自带的外设,配合少量逻辑门电路完成了所有的功能,以下是软硬件设计中的困难点:

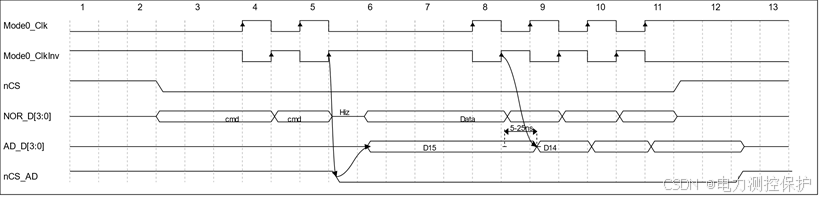

FSPI接入AD7606B设计

平台使用FSPI而不是SPI作为与AD7606B的接口,主要是为了提高数据传输带宽,可以使用FSPI的4位数据线传输数据,如果用SPI 1位数据传输,多个AD7606B 芯片需要多次控制传输,传输/占用中断的时间过长。

主要思路:

1. AD7606B初始化,由软件模拟时序,实现配置数据读写。

FSPI的D0-D3引脚配置为GPIO 输入;CS 和 CLK 引脚配置为GPIO 输出;1个单独的GPIO并接各个 AD7606B 的SDI引脚。

2. 运行时, FSPI配置为4位地址,4位数据宽度; FSPI 地址字节数设置为0,在中断中启动FSPI读取数据。为了规避FSPI CLK 前面2个周期D[3:0]输出的时命令字节数据,需要将CS片选延迟,并设置idle clk 数量为1-2周期。

CS延迟的方法可以用RC延迟电路或2个D触发器,用D触发器可靠性较好。

时间同步设计

为达到us级的时间同步性能,需要使用PWM模块的时间戳,RV1106G3的PWM capture mode时具有8个脉冲宽度数据FIFO,这个时间戳数据FIFO记录的是上个输入信号边沿到本次信号边沿的24MHz时钟计数值,是1个相对值,虽然软件可以对每个触发记录值累计来得到客观计数器值,但信号快速变化时会导致FIFO满溢出,进而导致计数值错误,为此无法直接用作为客观时间戳计数器来使用,变通使用的方法如下:

1)设备另外有1个PWM通道作为AD同步采样触发信号输出,上升沿触发AD转换,下降沿触发采样中断(PWM Continuous mode时无法产生中断,只能把信号接回1个GPIO来产生中断),AD中断可以模拟1个步长为250us,时钟频率24M的32位计数器。

2)硬件电路中设计有1个2选1选择器,用GPIO选择 time-sync 输入或AD同步采样触发信号输入到capture mode的PWM通道引脚。

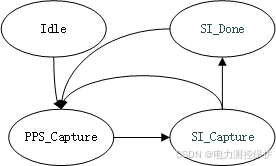

3)设置1个简单的状态机,每采样中断执行一次:

图中:

a)Idle :AD采样中断开启前置起始状态为Idle,进入采样中断,执行时间同步信号处理时直接转为PPS_Capture状态;PWM选择time-sync输入信号作为输入,开启中断前先清空PWM时间戳FIFO。

b)PPS_Capture :等待time-sync输入信号沿。PWM时间戳FIFO有且仅有1个数据认为收到正确的边沿信号,转到SI_Capture状态;选择AD 同步采样触发信号作为PWM输入,否则清空FIFO后,保持在PPS_Capture状态。

c)SI_Capture : 等待AD 同步采样触发信号的下降沿。根据前面time-sync 输入信号的上升或下降沿的不同,FIFO的有效数据 time-sync上升沿应当为3个,下降沿应当有2个, 这些数据之和即为time-sync输入信号的边沿到本次AD采样中断信号沿的时间差选择time-sync输入信号作为PWM输入,如果当前是time-sync的下降沿,直接转到PPS_Capture状态;否则转到SI_done。

d)SI_done : 完成time-sync的上升沿切换。应当有1个FIFO的有效数据,状态转PPS_Capture状态。选择time-sync输入信号作为PWM输入不变。

模拟32位计数器值减去上面的时间差 = time-sync信号边沿相对采样中断边沿的时间戳值,从而可以实现相对采样中断边沿的时间同步。

操作系统适配

RV1106 官方仅支持Linux系统,该部分系统适配较为简单,相关开发板以及参考资料相对较多。

但是保护测控设备一般使用RTOS,RV1106 官方对RTOS无支持,需要自行移植RTOS系统;目前芯片较为详细的参考资料很少,移植难度比较大。

这里选用了Thread-X 可靠性非常高的系统,移植最困难的是外设驱动开发,以RK3568-AMP SDK的hal支持包为基础(其支持RV1106),目前已完成了DMA、GIC、FSPI、PWM、SDMMC、RTC、WDT、UART、GMAC、SPI、USB等驱动。

设备业务功能方面,现已成功完成目前我们正在使用的保护测控开发组态平台的移植。

JTAG调试

复位时SDMMC0_DET 拉高,JTAG(SWD)使能,引脚使用Pin17 / Pin18(SDMMC0_D2/D3),此时可以用 CMSIS-DAP直接调试。

我所使用的PCB板SDMMC0已外接了贴片的SD-NAND,复位后无法直接使用JTAG pin 连接仿真器,需要将UART2的引脚配置成JTAG,而调试串口改用UART3,为此需要对DDR初始化bin映像进行修改,将调试串口由UART2改为3。

为了在启动JTAG调试前,DDR完成初始化和以及JTAG引脚功能被正确设置,需要自行开发1个load.bin,然后用boot_merger生成Download.bin,每次在开始调试前用SocToolKit高级功能:下载此Download.bin,才能开始调试。

开发此私有的Download.bin时,无法在自己的PCB板上调试,而用网上购买的开发板使用SD卡转接板连接调试器进行调试,测试功能正常,再生成Download.bin,就可以在自己的PCB板上用JTAG调试了。

总结

目前已完成了基于RV1106的低压电力保护测控设备开发平台设计,该平台主要特点:

- 平台选用RV1106G3,该芯片内核为cortex-a7,主频最高可达1.2G,并且支持NEON,其保护测控计算性能良好,简单测控保护的快速保护计算时间约50~80us(每1ms计算一次);

- RV1106G3有256M的片内内存,可以满足保护测控、通讯管理机一体的设备;

- 平台成本低,基于该平台开发低压电力保护测控设备,可降低产品成本;

- 平台可实现小型化设计;

- 平台已适配Linux和RTOS系统。

希望这篇文章对你有所帮助,有不足之处本人水平有限请谅解,欢迎批评指正。

2260

2260

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?