异步复位同步释放

数字IC经典电路设计

经典电路设计是数字IC设计里基础中的基础,盖大房子的第一部是打造结实可靠的地基,每一篇笔者都会分门别类给出设计原理、设计方法、verilog代码、Testbench、仿真波形。然而实际的数字IC设计过程中考虑的问题远多于此,通过本系列希望大家对数字IC中一些经典电路的设计有初步入门了解。能力有限,纰漏难免,欢迎大家交流指正。快速导航链接如下:

一、前言

电路的任何一个寄存器、存储器结构和其他时序单元都必须附加复位逻辑电路,以保证电路能够从错误状态中恢复、可靠地工作。对于综合实现的真实电路,通过复位使电路进入初始状态或者其他预知状态。复位在数字IC设计中是不可缺少的一部分,故一定要清楚掌握深入理解复位的作用。

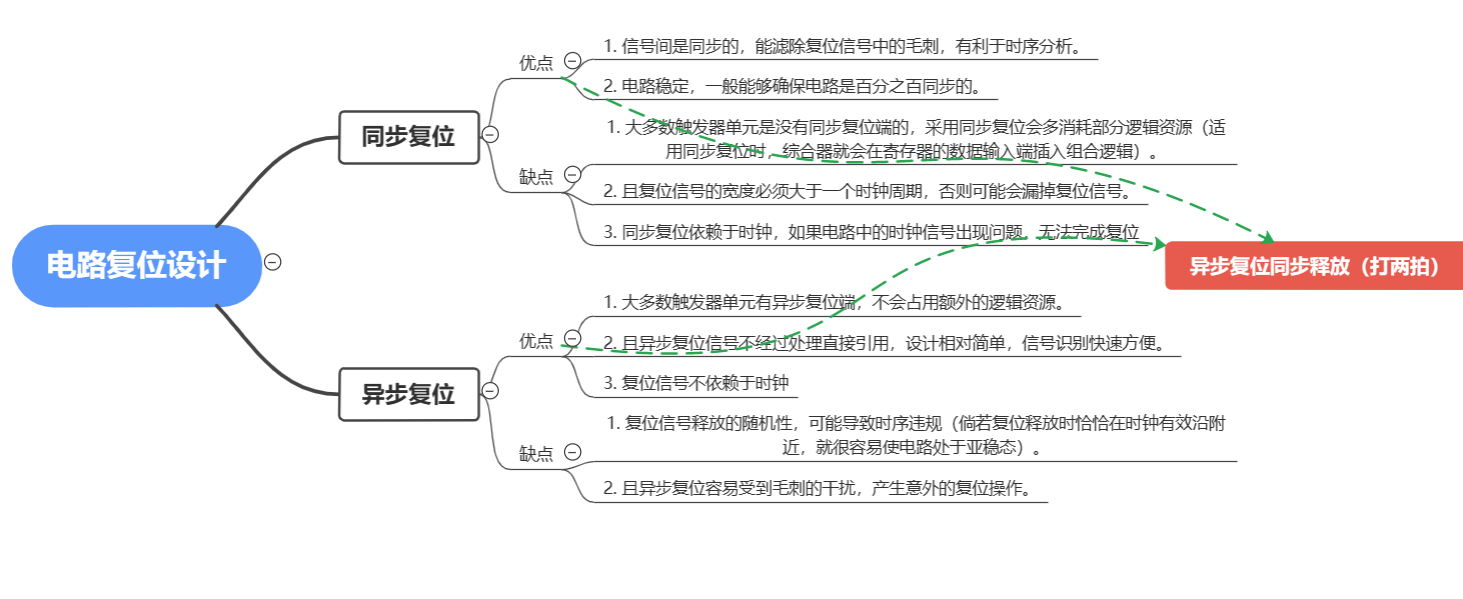

复位信号可以分为同步复位和异步复位两大类。

同步复位指的是当复位信号发生变化时,并不立即生效,而是等到有效时钟沿采集到复位信号的变化后,才会对寄存器进行复位操作;

而异步复位则不依赖于系统时钟,一旦信号发生变化,就会立即对寄存器进行复位操作。

由于在现有的大多数逻辑器件库中,触发器DFF都是只包含有异步复位端口,所以同步复位的使用会造成冗余组合逻辑的使用,浪费资源。因此,大多数数字设计中都采用的是异步复位信号。虽然异步复位信号更加方便使用,但是_因为复位信号与系统时钟异步的关系,很容易出现复位信号释放位置恰恰出现在时钟有效沿附近,导致亚稳态的出现_。

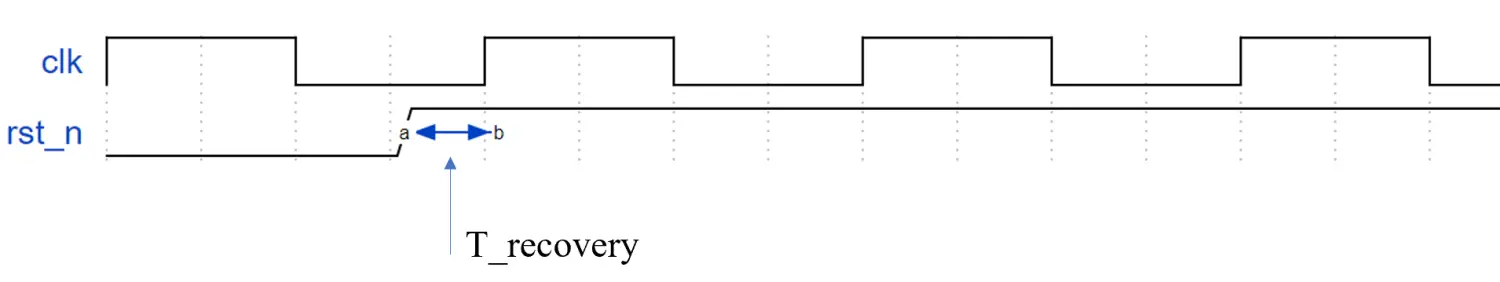

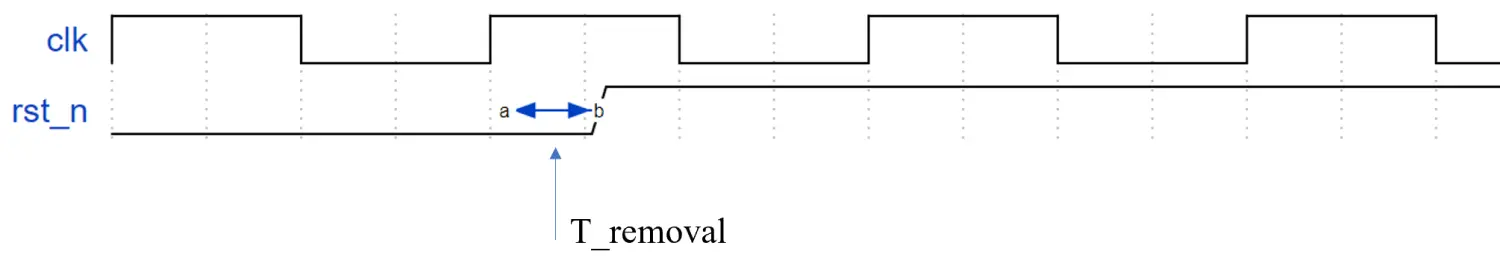

对于异步复位,有类似于寄存器建立时间和保持时间的说法,分别是recovery time 和temoval time。如下面两张图所示:

- recovery time是异步复位的恢复时间,指的是复位释放与下一个时钟有效边沿之间需要间隔的最小时间。

- removal time是异步复位的去除时间,指的是复位释放与上一个时钟有效边沿之间需要间隔的最小时间。

如果异步复位的释放时间不满足以上这两个条件,寄存器很可能进入亚稳态,导致电路运行失常。为了保证解决这个问题,可以采用异步复位同步释放的复位信号设计方法。顾名思义,异步复位同步释放就是对复位信号的释放过程做同步处理,使得释放的过程能够与系统时钟同步。

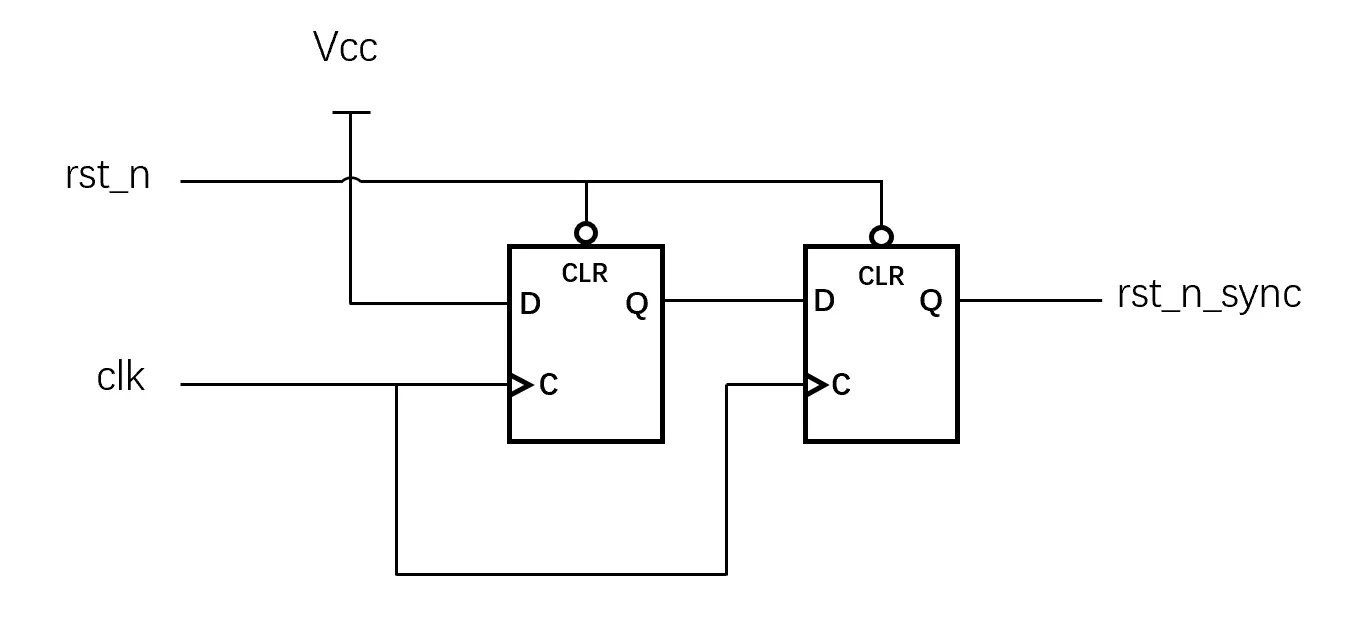

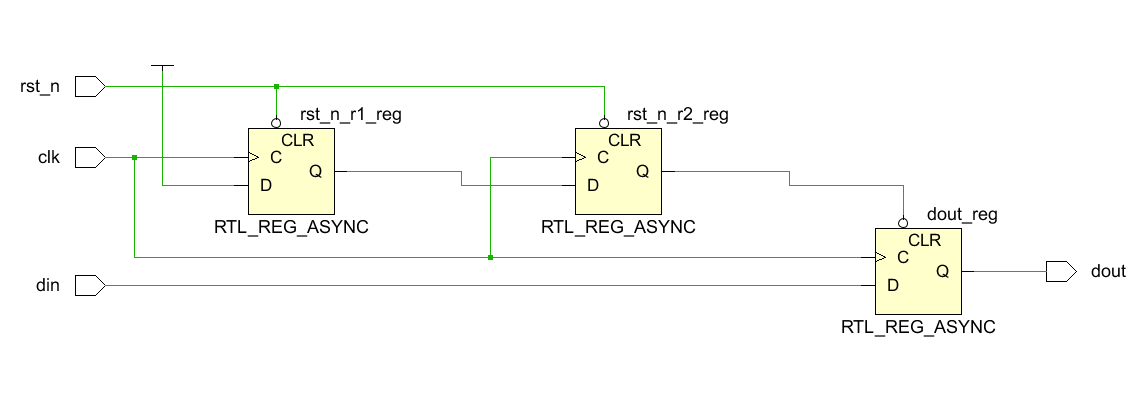

异步复位,同步释放本质就是引入两个触发器,其电路图和时序处理如下图所示:

观察上述电路图和时序图就知道,其实异步复位同步释放和两级打拍的跨时钟域信号处理很相似,本质上都是对信号进行同步处理。

以下是对同步复位、异步复位、异步复位同步释放的详细介绍:

二、同步复位

同步复位是指复位信号在时钟有效边沿到来时有效。如果没有时钟,无论复位信号怎样变化,电路也不执行复位操作。

同步复位的典型代码描述如下:

module sync_reset(

input rst_n, //同步复位信号

input clk, //时钟

input din, //输入数据

output reg dout //输出数据

);

always @(posedge clk) begin //复位信号不要加入到敏感列表中

if(!rst_n) begin

dout <= 1'b0 ;//rstn 信号与时钟 clk 同步

end

else begin

dout <= din ;

end

end

endmodule

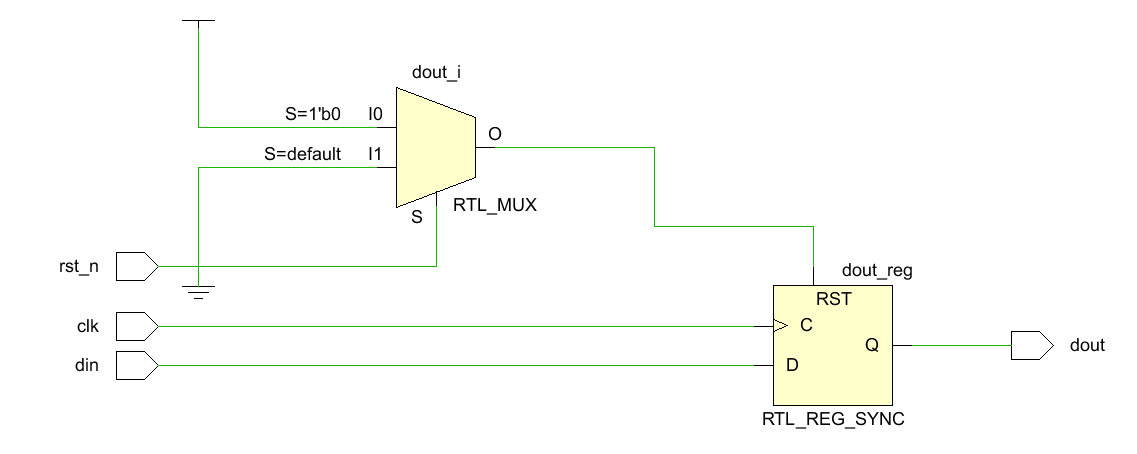

该描述代码常常会被综合成如下电路:

同步复位的优点:

- 信号间是同步的,能滤除复位信号中的毛刺,有利于时序分析。

- 电路稳定,一般能够确保电路是百分之百同步的。

同步复位的缺点:

- 大多数触发器单元是没有同步复位端的,采用同步复位会多消耗部分逻辑资源(适用同步复位时,综合器就会在寄存器的数据输入端插入组合逻辑)。

- 且复位信号的宽度必须大于一个时钟周期,否则可能会漏掉复位信号。

- 同步复位依赖于时钟,如果电路中的时钟信号出现问题,无法完成复位

三、异步复位

异步复位是指无论时钟到来与否,只要复位信号有效,电路就会执行复位操作。

异步复位的典型代码描述如下:

module async_reset(

input rst_n, //异步复位信号

input clk, //时钟

input din, //输入数据

output reg dout //输出数据

);

always @(posedge clk or negedge rst_n) begin //复位信号不要加入到敏感列表中

if(!rst_n) begin

dout <= 1'b0 ; //rstn 信号与时钟 clk 异步

end

else begin

dout <= din ;

end

end

endmodule

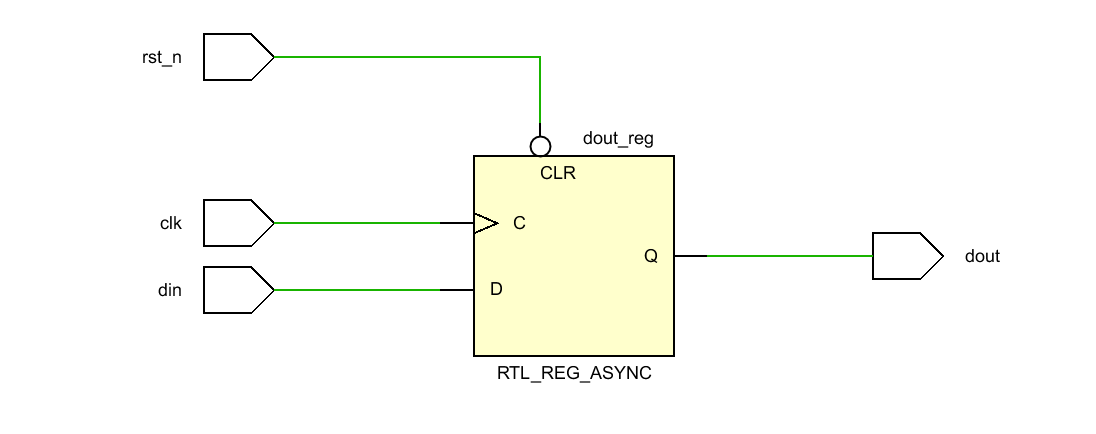

该代码常常会被综合成如下电路:

异步复位的优点:

- 大多数触发器单元有异步复位端,不会占用额外的逻辑资源。

- 且异步复位信号不经过处理直接引用,设计相对简单,信号识别快速方便。

- 复位信号不依赖于时钟。

异步复位的缺点:

- 复位信号与时钟信号无确定的时序关系,异步复位很容易引起时序上 removal 和 recovery 的不满足。复位信号释放的随机性,可能导致时序违规,倘若复位释放时恰恰在时钟有效沿附近,就很容易使电路处于亚稳态。

- 且异步复位容易受到毛刺的干扰,产生意外的复位操作。

四、异步复位同步释放

综合设计与资源等方面的考虑,一般数字系统设计时都会使用异步复位。为消除异步复位的缺陷,复位电路往往会采用“异步复位、同步释放”的设计方法。即复位信号到来时不受时钟信号的同步,复位信号释放时需要进行时钟信号的同步。

异步复位、同步释放的典型代码描述如下:

module areset_srelease(

input rst_n, //异步复位信号

input clk, //时钟

input din, //输入数据

output reg dout //输出数据

);

reg rst_n_r1;

reg rst_n_r2;

always @ (posedge clk or negedge rst_n) begin

if (!rst_n) begin

rst_n_r1 <= 1'b0; //异步复位

rst_n_r2 <= 1'b0;

end

else begin

rst_n_r1 <= 1'b1; //同步释放

rst_n_r2 <= rst_n_r1; //同步打拍,时序差可以多延迟几拍

end

end

//使用 rstn_r2 做同步复位,复位信号可以加到敏感列表中

always @ (posedge clk or negedge rst_n_r2) begin

if (!rst_n_r2) begin

dout <= 1'b0; //同步复位

end

else begin

dout <= din;

end

end

endmodule

该代码常常会被综合成如下电路:

Testbench代码描述如下:

`timescale 1ns/1ps

module areset_srelease_tb();

reg rst_n;

reg clk;

reg din;

wire dout;

areset_srelease u_areset_srelease(

.clk (clk),

.rst_n (rst_n),

.din (din),

.dout (dout)

);

always #5 clk = ~clk;

initial begin

clk = 0;

#5 rst_n = 1;

#10 rst_n = 0;

#10 rst_n = 1;

din = 1;

#300;

$finish;

end

endmodule

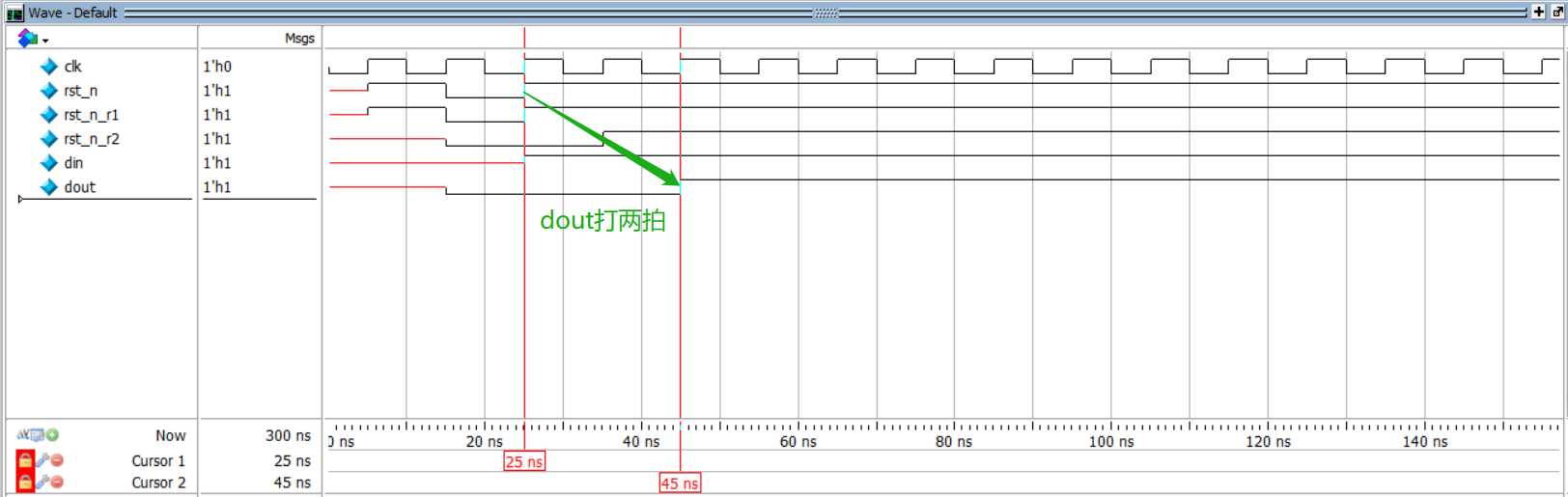

仿真结果如下:

可以看到,经过“异步复位同步释放”处理后,信号在复位信号后的第二个有效上升时钟沿进行了翻转,极大地消除异步复位信号的释放可能引起的亚稳态影响。

五、总结

同步复位的优点:

- 信号间是同步的,能滤除复位信号中的毛刺,有利于时序分析。

- 电路稳定,一般能够确保电路是百分之百同步的。

同步复位的缺点:

- 大多数触发器单元是没有同步复位端的,采用同步复位会多消耗部分逻辑资源(适用同步复位时,综合器就会在寄存器的数据输入端插入组合逻辑)。

- 且复位信号的宽度必须大于一个时钟周期,否则可能会漏掉复位信号。

- 同步复位依赖于时钟,如果电路中的时钟信号出现问题,无法完成复位

异步复位的优点:

- 大多数触发器单元有异步复位端,不会占用额外的逻辑资源。

- 且异步复位信号不经过处理直接引用,设计相对简单,信号识别快速方便。

- 复位信号不依赖于时钟。

异步复位的缺点:

- 复位信号与时钟信号无确定的时序关系,异步复位很容易引起时序上 removal 和 recovery 的不满足。复位信号释放的随机性,可能导致时序违规,倘若复位释放时恰恰在时钟有效沿附近,就很容易使电路处于亚稳态。

- 且异步复位容易受到毛刺的干扰,产生意外的复位操作。

异步复位和同步复位在设计的时候各有优缺点,那有没有综合两者的优点的复位方式呢?那就是异步复位同步释放,既保证了正常的异步复位不受时钟影响,又通过打两拍的方式消除了电路中的亚稳态(严格来讲是极大概率地消除亚稳态)。

更多可查看个人主页链接

软件版本:Modelsim 10.6c

不定期纠错补充,欢迎随时交流

最后修改日期:2023.6.2

294

294

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?