FPGA HLS 多路视频叠加融合

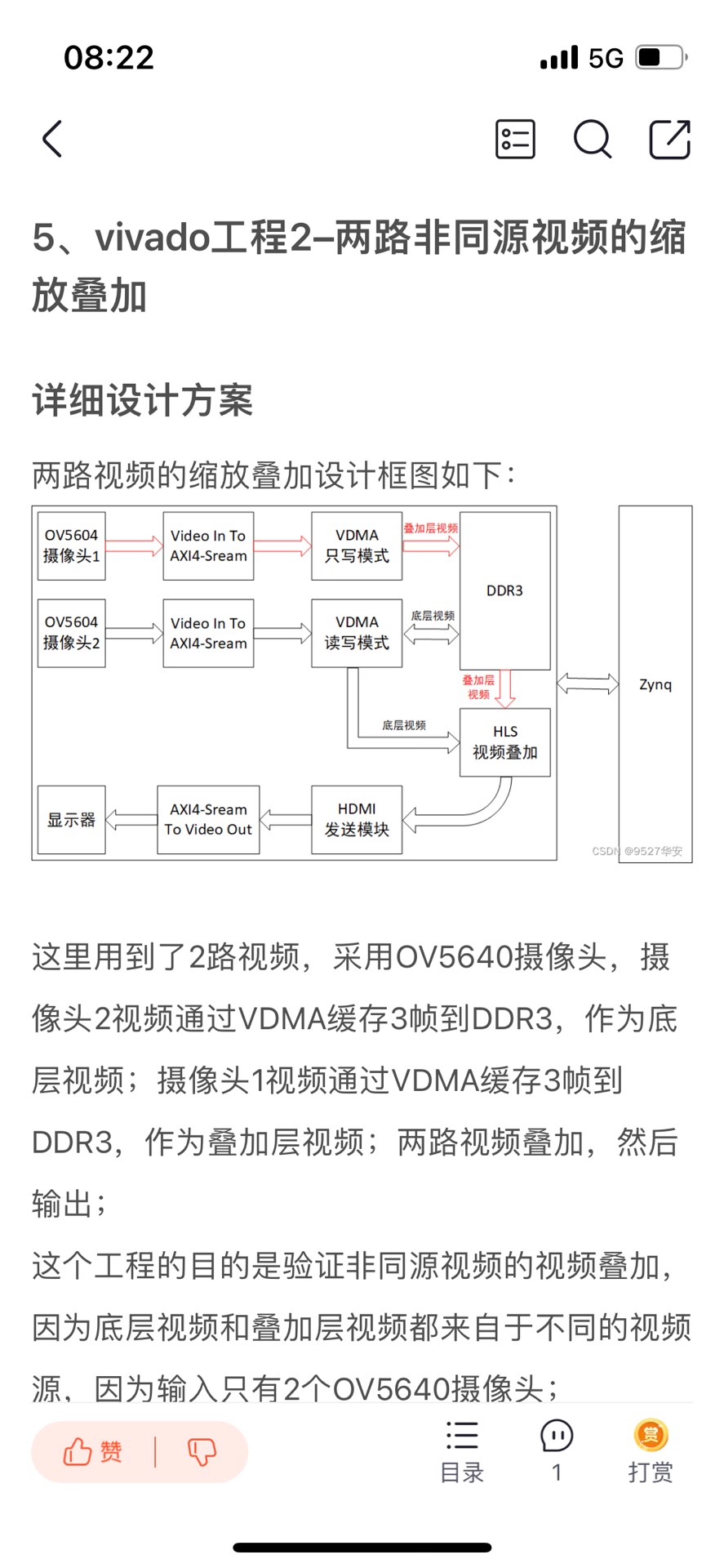

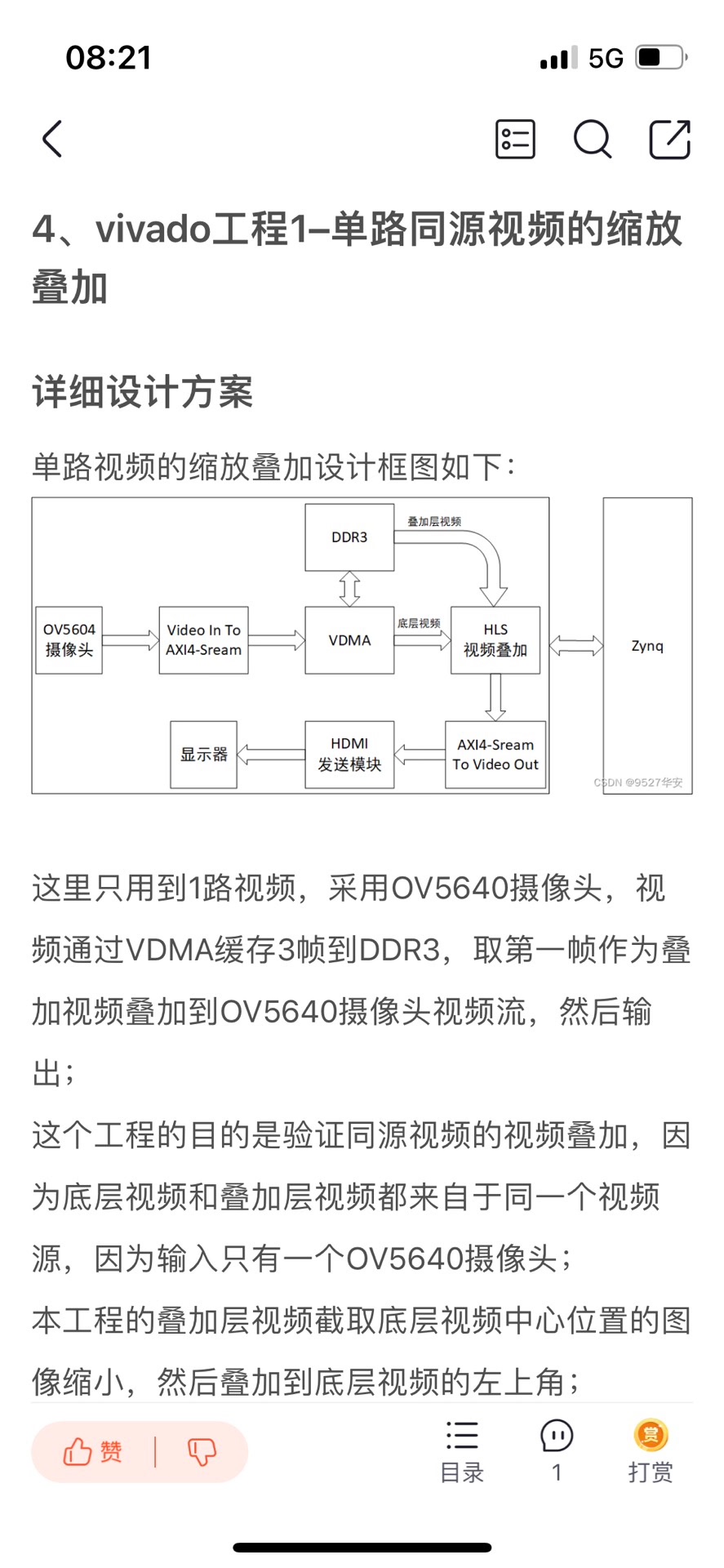

本设计提供2套vivado工程,一套是单路同源视频的缩放叠加,原视频作为底层视频,取原视频的中间部分缩小后作为叠加视频,叠加于底层视频的左上角后输出;另一套是两路非同源视频的缩放叠加,一路视频作为底层视频,取另一路视频的中间部分缩小后作为叠加视频,叠加于底层视频的左上角后输出;代码编译通过后上板调试验证,可直接项目移植

ID:16666723968837814

FPGA小白

FPGA HLS 多路视频叠加融合

在现代社会中,视频技术的广泛应用给人们的生活带来了诸多便利。为了满足用户对于视频处理的需求,不断推出新的技术方案是不可避免的。FPGA (Field-Programmable Gate Array) 是一种可编程逻辑器件,具有高度灵活性和可重构性,被广泛应用于各种领域,尤其是视频处理领域。

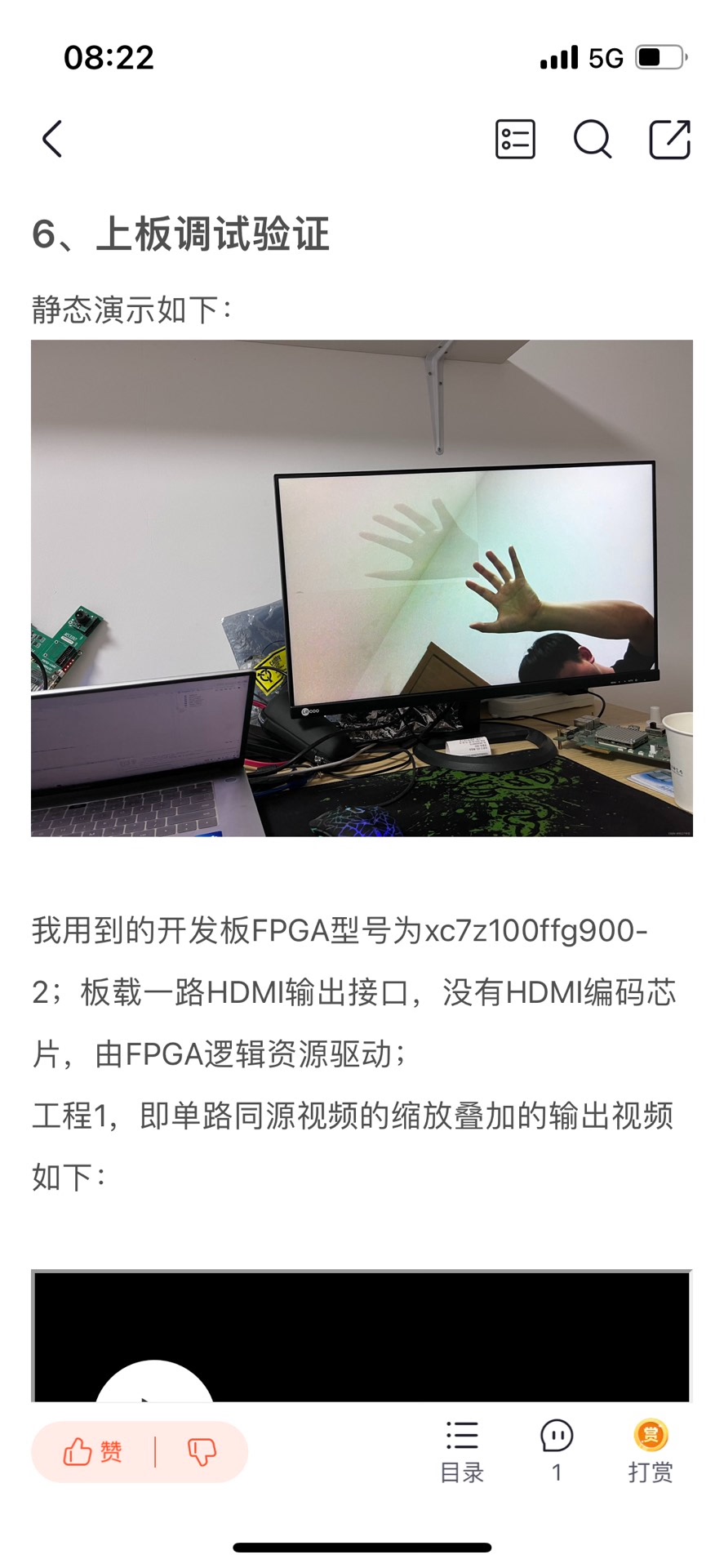

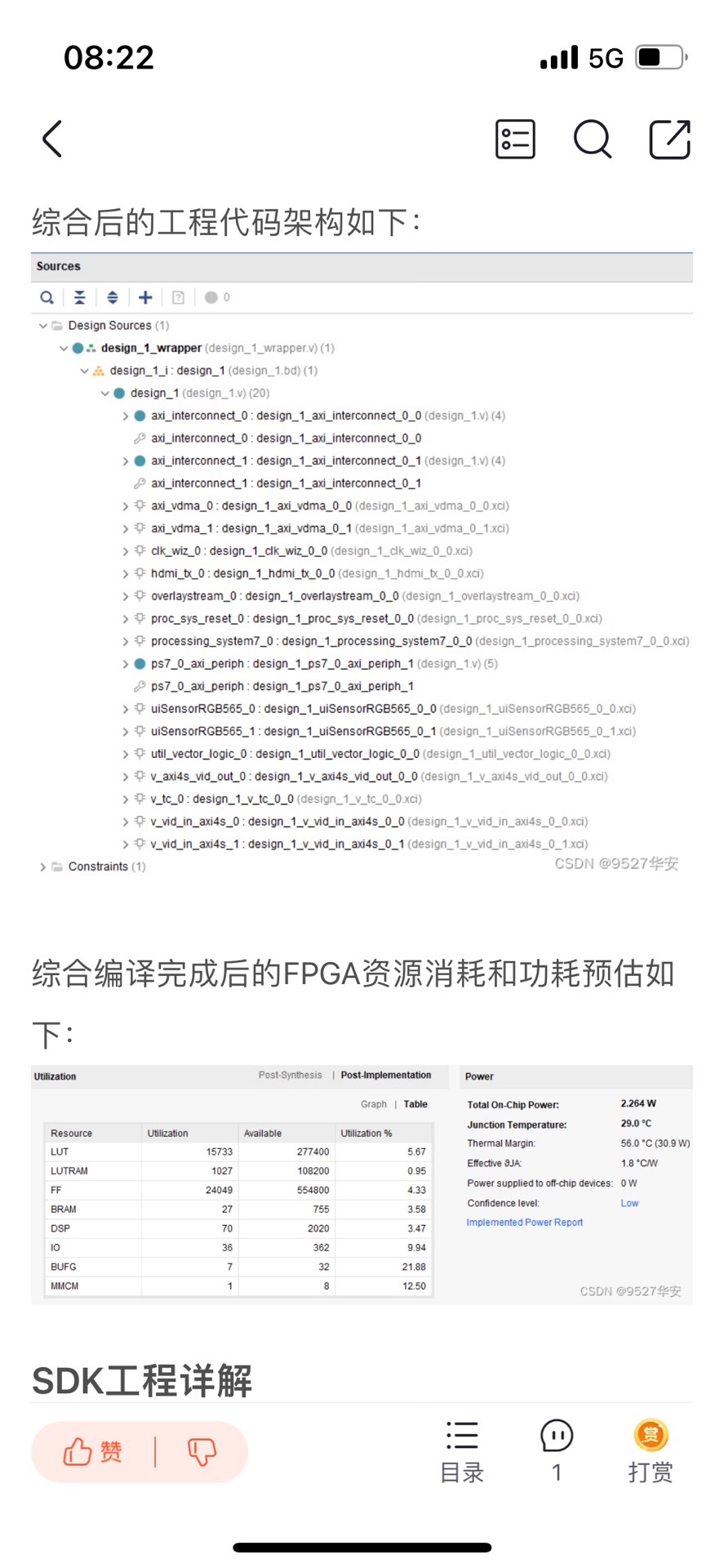

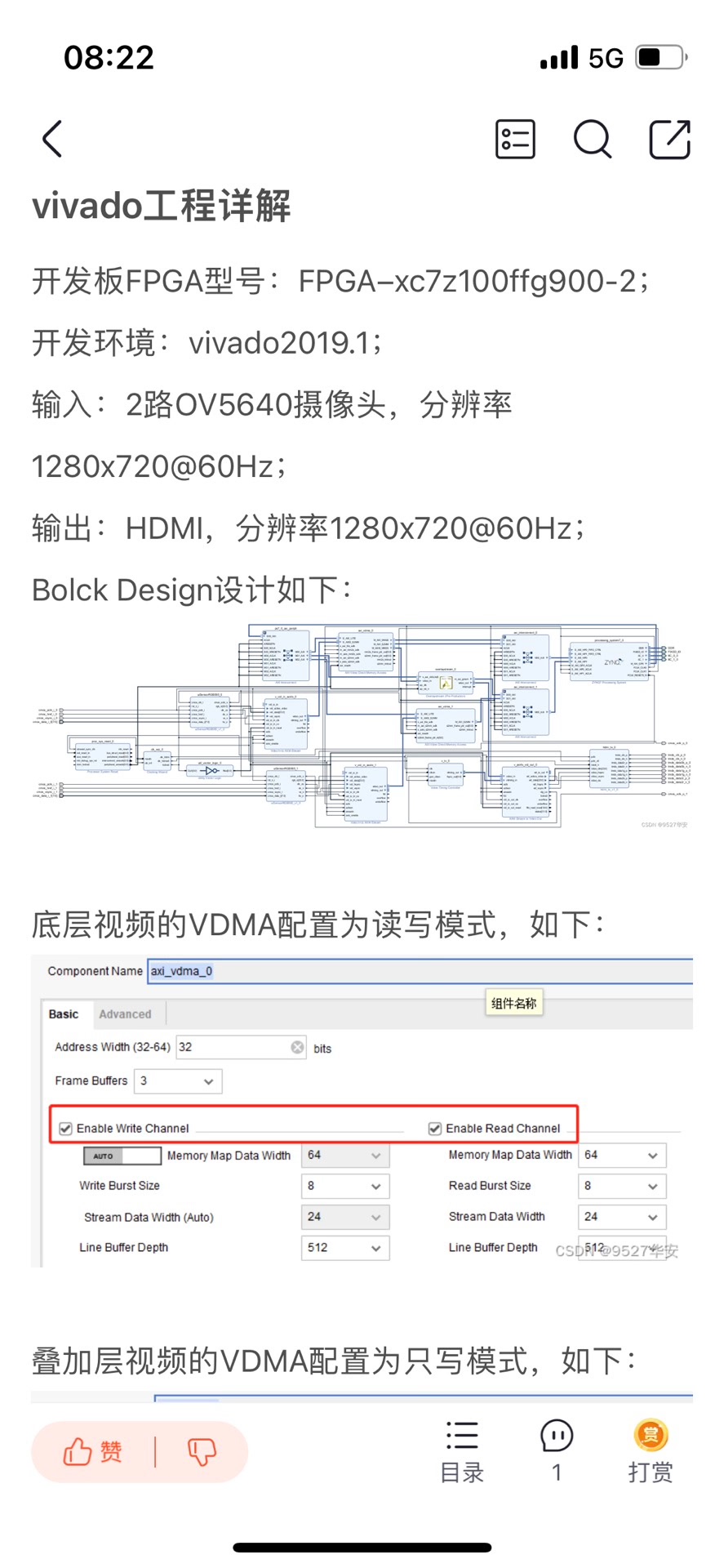

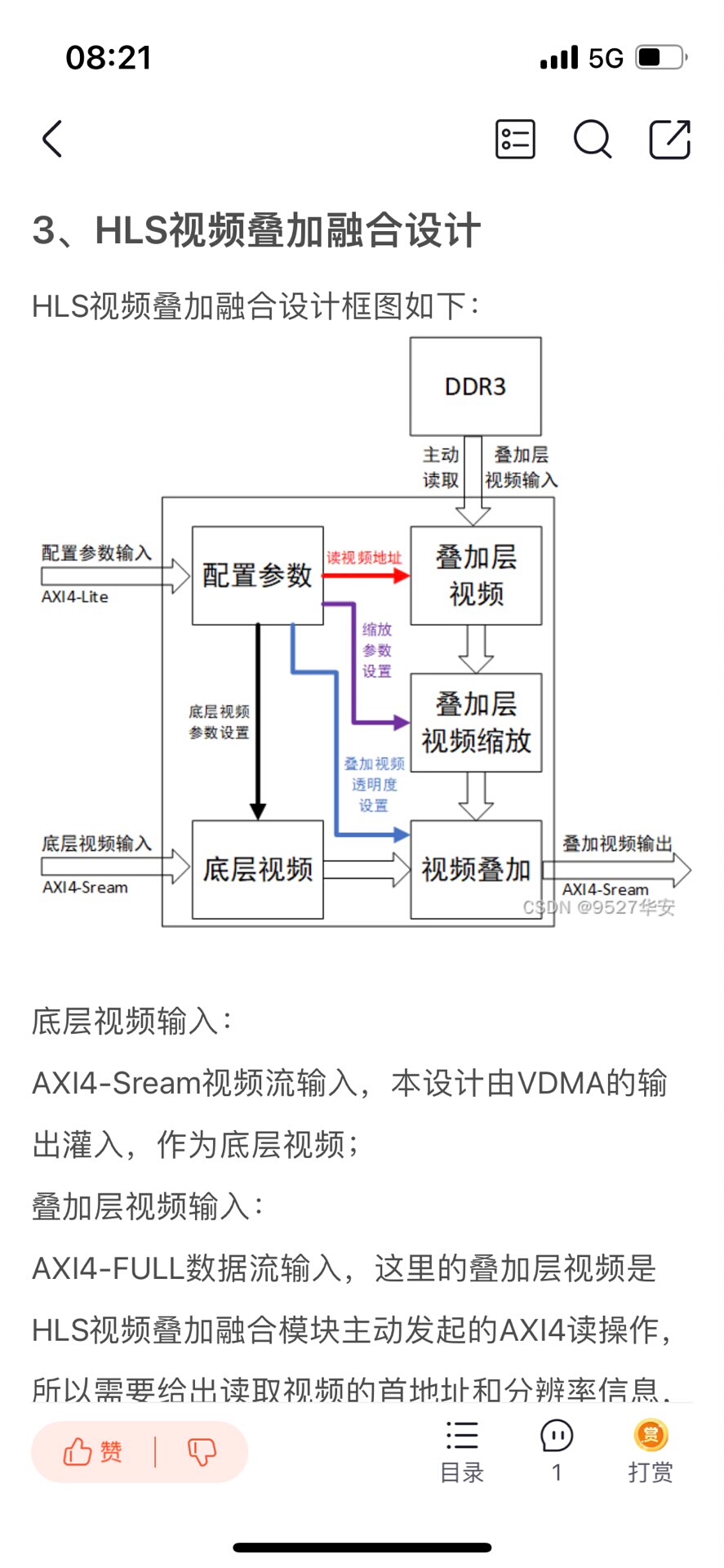

本文将介绍一个基于FPGA HLS的多路视频叠加融合设计。该设计提供了两套vivado工程,分别用于处理单路同源视频和两路非同源视频。在单路同源视频的缩放叠加方案中,原视频作为底层视频,取原视频的中间部分进行缩小处理,并将其叠加于底层视频的左上角,最后将处理结果输出。而在两路非同源视频的缩放叠加方案中,一路视频作为底层视频,取另一路视频的中间部分进行缩小处理,并将其叠加于底层视频的左上角,同样输出处理结果。

该设计的关键在于使用了FPGA HLS技术,可以将高级语言代码转换为硬件描述语言代码,从而实现高效的硬件加速。通过使用HLS工具,可以将视频处理算法以C/C++的形式描述,并通过编译优化转换为硬件描述语言代码,从而在FPGA上实现视频叠加融合功能。

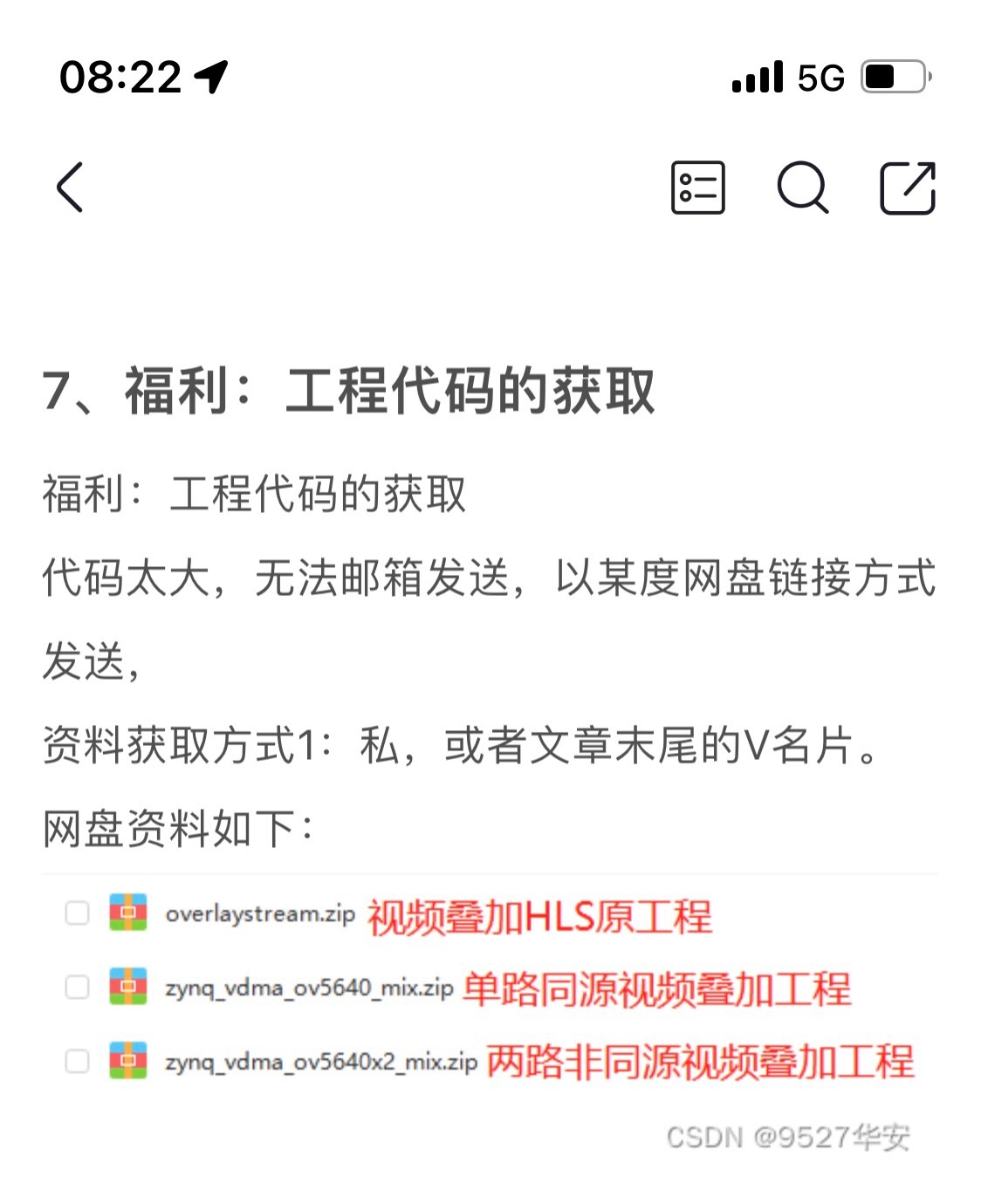

为了验证设计的正确性和可行性,在完成代码编译后,可以进行上板调试验证。通过将设计项目移植到实际的FPGA板卡上,并进行实际测试,可以检验设计的性能和功能是否符合要求。

在实际应用中,多路视频叠加融合设计可以应用于许多领域,例如视频监控系统、虚拟现实技术、医学影像处理等。在视频监控系统中,可以通过将多路视频叠加融合,将多个监控画面同时显示在一个屏幕上,方便用户查看。在虚拟现实技术中,可以通过叠加融合技术,将现实世界和虚拟场景相结合,提供更加沉浸的体验。在医学影像处理中,可以将不同的医学图像进行叠加融合,帮助医生更好地进行诊断和治疗。

总之,本文介绍了一个基于FPGA HLS的多路视频叠加融合设计。通过使用高级语言编写视频处理算法,并通过编译优化转换为硬件描述语言代码,可以在FPGA上实现高效的视频叠加融合功能。这种设计方案在实际应用中具有广泛的应用前景,可以满足用户对于视频处理的需求,提供更好的使用体验。

【相关代码,程序地址】:http://fansik.cn/723968837814.html

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?