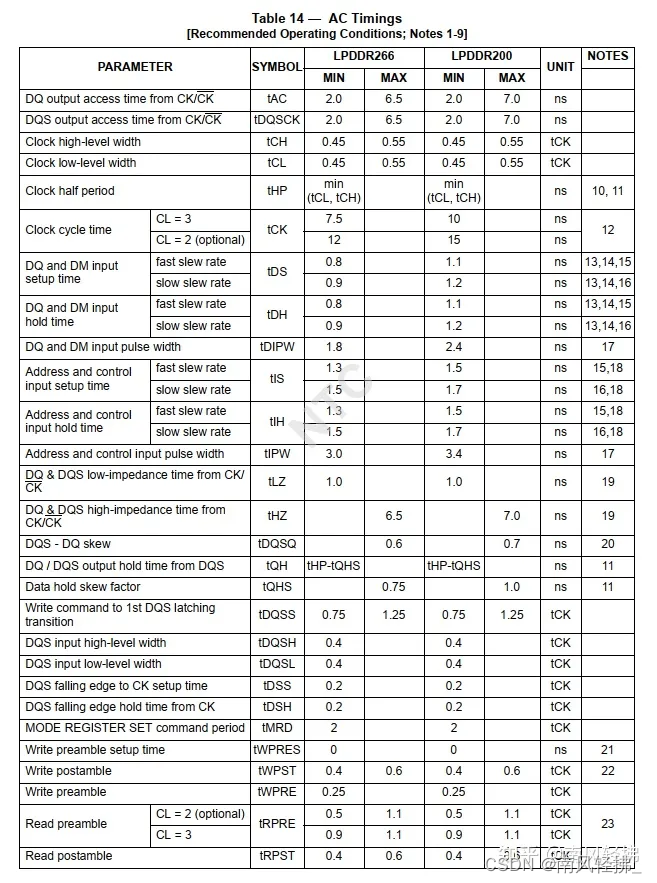

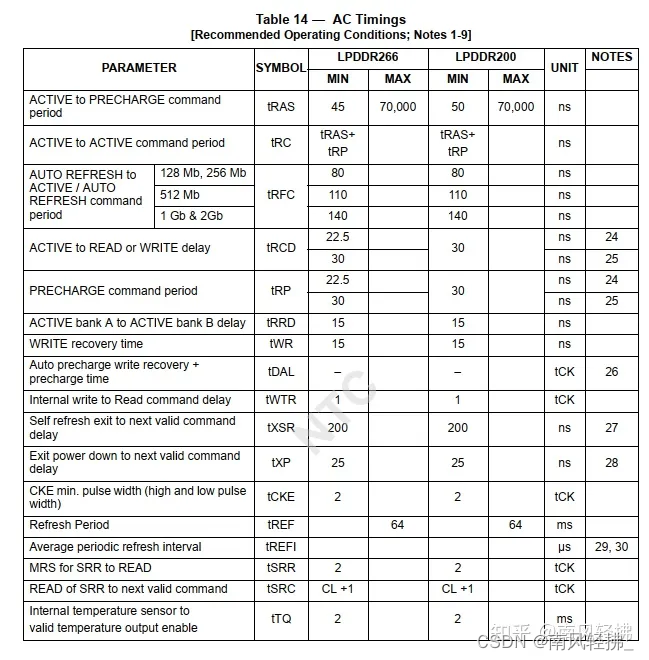

7 AC & DC Operating Conditions 模拟信号数字信号的操作参数

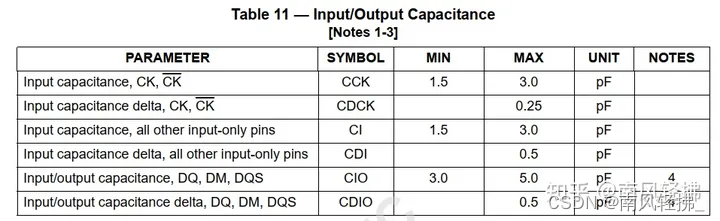

NOTES:

1.这些值需要设计人员保证,并且仅在样品基础上进行测试可得到。

2. .这些电容值仅适用于单片器件,多个die封装需要并联电容负载

3. 根据JEP147标准,通过施加VDD、VDDQ,同时将所有其它引脚(除了被测引脚之外)设置为浮动状态,通过将CKE拉至低电平将DQ设置为高阻抗状态,使用矢量网络分析仪测量电容的程序测量输入电容值。

4. 尽管DM是一个只能输入的引脚,但该引脚的输入电容必须模拟DQ和DQS引脚的输入容量。这是在匹配系统定义DQ、DQS和DM的信号传播时间需要满足的前提。

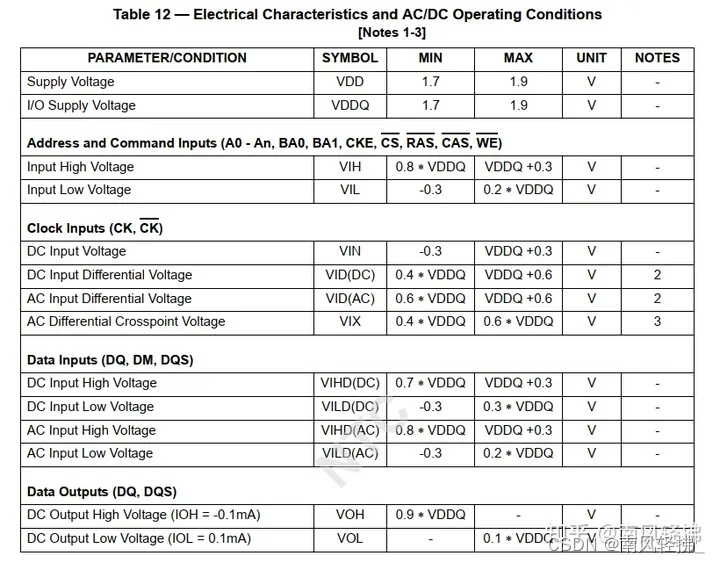

备注:

1. 参考VSS和VSSQ的所有电压必须是相同的电势。

2.VID(DC)和VID(AC)是CK上的输入电平和/CK上的输出电平之间的差值。(VID,预先设置好的电压值)

3. VIX的值大致为0.5*VDDQ,并且必须和相同的DC电平的变化保持一致

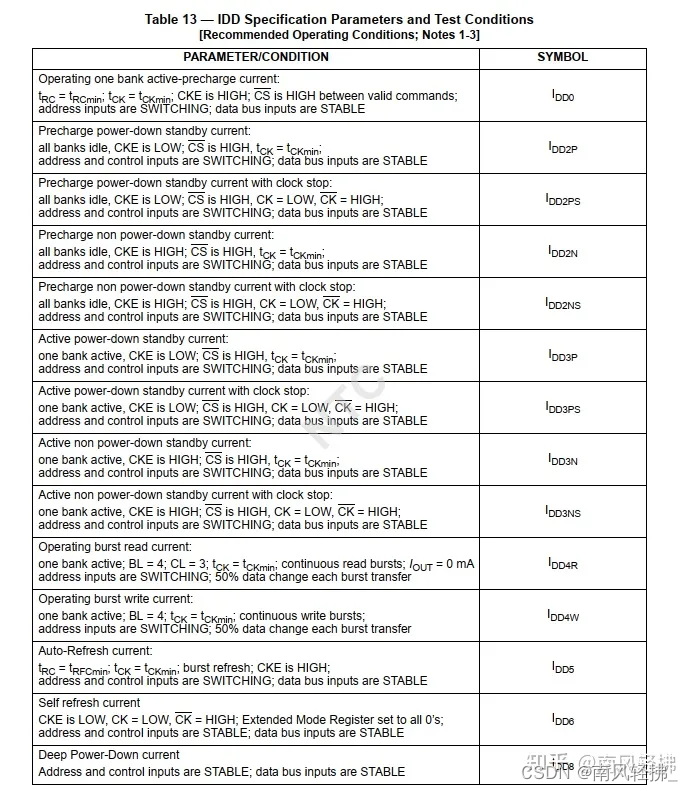

备注:

1. IDD具体的测试值需要在LPDR1正确初始化后进行测试。

2. Input slew rate is 1V/ns. 输入的压摆率是1V/1ns

3. 对IDD的定义

LOW is defined as VIN ≤ 0.1 * VDDQ; 定义VIN的值小于0.1 * VDDQ时为低电平

HIGH is defined as VIN ≥ 0.9 * VDDQ;定义VIN的值大于0.9 * VDDQ时为高电平

STABLE is defined as inputs stable at a HIGH or LOW level; 稳定指的是输入电平为低电平或者高电平状态

SWITCHING is defined as: 转换定义的是

- Address and command: inputs changing between HIGH and LOW once per two clock cycles;

地址和命令输入时每两个时钟周期在高电平和低电平之间切换一次。

- Data bus inputs: DQ changing between HIGH and LOW once per clock cycle; DM and DQS are STABLE

数据总线输入:每个时钟周期内,DQ输入时在高和低电平之间切换一次,且DM、DQ保持稳定

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2954

2954

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?