芯片原厂必学课程 - 第三篇章 - IC 理论篇

03-09 关键路径及其时序分析

新芯设计:专注,积累,探索,挑战

文章目录

引言

本文主要介绍了关键路径和流水设计,以及静态时序分析 STA

NOTES:本文来自《芯片原厂必学课程 - 第三篇章 - IC 理论篇》技术专栏

🌏 一、关键路径的相关概念

关键路径是指设计中从输入到输出经过的最大延时的组合逻辑路径。

优化关键路径是一种提高设计工作速度的有效方法,一般地,从输入到输出的延时取决于信号所经过的延时最大路径,而与其它较小的延时路径无关,在优化设计的过程中,关键路径法可以反复使用,直到不可能减少关键路径延时为止。EDA 工具中综合器及设计分析器通常都提供关键路径的信息以便设计者改进设计,从而提高速度。

关键路径是一个系统内计算时间最长的纯粹组合逻辑路径。如果系统的运行时钟周期小于关键路径长度,那么关键路径上的节点尚未计算完毕(物理上就是信号还未稳定),下个时钟触发沿就来到了,造成寄存器锁存了不稳定的错误的数据,最后造成整个系统输出错误结果。因此,关键路径决定了系统时钟的最大频率,系统时钟周期只能大于或等于关键路径长度。

🌏 二、流水设计的相关概念

流水设计是指在数据通路上引入流水线寄存器来缩短关键路径,即通过插入流水线来分割关键路径,缺点是会增加数据的输出延时。

想要详细了解的可以阅读书籍(如今已经绝版):VLSI Digital Signal Processing Systems:design and Implementation(VLSI 数字信号处理系统:设计与实现)

🌏 三、PPT 获取方式

关注 新芯设计 公众号,发送关键词 数字信号处理 即可

🌏 四、静态时序分析的相关概念

静态时序分析 STA(Static Timing Analysis)也称静态时序验证,是一种以与输入激励无关的方式进行的,其目的是通过遍历所有的传输路径,寻找所有的组合逻辑电路的最坏延迟情况(以及毛刺、时钟偏差等等),主要是通过检查建立时间和保持时间是否满足要求,而它们又是通过最大组合逻辑路径延迟和最小组合逻辑路径延迟的分析得到的。

静态时序分析是 VLSI 设计中非常重要的一个环节,它能够验证设计在时序上的正确性,并决定设计是否能够在要求的工作频率下运行(在 VLSI 设计中,动态时序验证不仅有着难以承受的工作量和时间量,而且还难以保证足够的覆盖率,促使了时序分析技术从动态向静态迁移)。

🌏 五、静态时序分析的原因和路径

两大静态时序分析原因:

- 器件内延时:逻辑门、DFF 等等;

- 互连线延时:导线、时钟等等。

四大静态时序分析路径:

- 寄存器到寄存器:Reg2Reg;

- 寄存器到输出引脚:Reg2Pin;

- 输入引脚到寄存器:Pin2Reg;

- 输入引脚到输出引脚:Pin2Pin。

其中,最关心的依旧是数据信号和时钟上升沿之间的建立时间和保持时间的关系(不同的 FPGA 厂家的器件时序参数各有不同,同时也是固定的数值)。

🌏 六、静态时序分析的优点和缺点

静态时序分析的优点:

- 执行速度快;

- 不需要测试向量;

- 测试覆盖率可以近乎达到 100%;

- 能够完成动态仿真所不能实现的复杂分析。

静态时序分析的缺点:

- 不能验证设计的功能;

- 只能验证同步时序电路的时序特性,如果设计中含有较多的异步电路,则应该通过门级动态仿真来验证;

- 不能自动识别设计中的特殊路径,如多周期路径(Multi-Cycle Path)、非正常路径(False Path)、多时钟分配(Multiple Path)等等。

🌏 七、建立时间、保持时间在静态时序分析中的要求

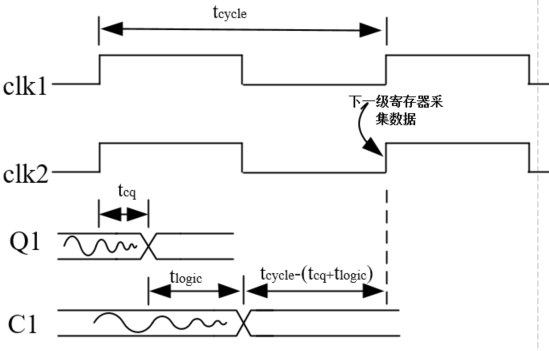

建立时间、保持时间在静态时序分析中的要求(这里不考虑时钟偏差与时钟抖动):时钟周期应该大于寄存器最大传播延时(从 D 触发器的输入数据被时钟打入到 D 触发器,到数据到达 D 触发器输出端的延迟时间)、组合逻辑最大延时与目标寄存器(D 触发器)建立时间之和:Tcycle >= Tcq + Tlogic + Tsu。目标寄存器保持时间应该小于寄存器污染延时与组合逻辑污染延时之和:Th <= Tcq,cd + Tlogic,cd。保持时间希望中间的组合逻辑延时越大越好,反之,建立时间则希望中间的组合逻辑越小越好。

寄存器最大传播延时 Tcq,是指时钟翻转之后(0→1),数据从 D 触发器的输入端 D 到输出端 Q 的最大延时;

电路的线延时和组合逻辑最大延时 Tlogic,是指本级寄存器的输出到达下一级寄存器的输入之间的最大延时;

最大延时和污染延时相互对应,污染延时表示最小延时的意思,一般添加后缀名 “cd” 加以表示;

🌏 八、建立时间裕量和保持时间裕量

-

建立时间裕量:Tsu_slack = Tcycle - Tcq - Tlogic - Tsu

-

保持时间裕量:Th_slack = Tcq,cd + Tlogic,cd - Th

-

以上二者都应该大于零

🌏 九、建立时间裕量和保持时间裕量

-

数据要求时间:Trequired = Tcycle - Tsu

-

数据到达时间:Tarrived = Tlogic + Tcq

-

裕量 = 数据要求时间 - 数据到达时间:Slack = Data Required Time - Data Arrival Time

🌏 十、FPGA 开发与 STA

FPGA 开发软件也是通过这种方法来计算系统最高运行速度 Fmax。因为 Tcq 和 Tsu 是由具体的器件工艺决定的,故设计电路时只能改变组合逻辑的延迟时间 Tlogic,所以说缩短触发器间组合逻辑的延时时间是提高同步电路速度的关键所在。

可以将较大的组合逻辑分解为较小的 N 块,通过适当的方法平均分配组合逻辑,然后在中间插入 D 触发器,并和原 D 触发器使用相同的时钟,就可以避免在两个 D 触发器之间出现过大的延时,消除速度瓶颈,这样可以提高电路的工作频率,这就是所谓的 “流水线” 技术的基本设计思想,即 “插入流水线”,从而提高 Fmax,加快系统工作速度,增大吞吐量。值得注意的是,流水线设计会在原数据通路上加入延时,另外硬件面积也会稍有增加,这也是面积换速度的基本设计思想。

4072

4072

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?