- 时序分析的本质是什么

- 建立时间要求和保持时间要求是如何产生的

- 时序路径共有几种

- 如何确立建立时间要求及slack

- 如何确立保持时间要求及slack

- 建立时间和保持时间为何可以为负

1.什么是时序分析

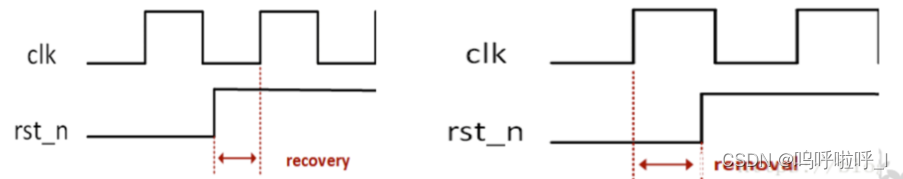

时序分析本质上就是一种时序检查,目的是检查设计中所有的D触发器是否能够正常工作,也就是检查D触发器的同步端口(数据输入端口)的变化是否满足建立时间要求(Setup)和保持时间要求(Hold);检查D触发器的异步端口(异步复位端口)的变化是否满足恢复时间要求(Recovery)和移除时间要求(Removal)。

rst_n信号的复位时刻必须在recovery之前,否则可能不是非复位状态;

rst_n信号的释放必须在removal后(这里的复位信号是低电平有效)。

2.时序分析分类

时序分析包括静态时序分析(STA)和动态时序分析。

-

动态时序分析:将布局布线生成的布线延迟信息反标注到门级网表中进行仿真,检查是否存在时序违例。此时的仿真包括门延迟和布线延迟信息,能够较好反应芯片的实际工作情况。

缺点:因为不可能产生完备的测试向量,覆盖门级网表中的每一条路径。因此在动态时序分析中,无法暴露一些路径上可能存在的时序问题。

-

静态时序分析:采用穷尽分析方法来提取出整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误。

它不需要输入向量就能穷尽所有的路径,且运行速度很快、占用内存较少,不仅可以对芯片设计进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计,因此静态时序分析已经越来越多地被用到数字集成电路设计的验证中。

静态时序分析使用的工具

①Xilinx Vivado Intergreated Design Environment Time Engine

②Altera Quartus II Timequest

③DC等

动态时序分析使用的工具

①Mentor Modelsim

②Cadence NC-Verilog

③Sysnopsys VCS

静态时序分析的准备工作

撰写基本的时序约束文件,告知时序引擎一些必要的信息(比如时钟,输入输出延时等)。

3.基础知识

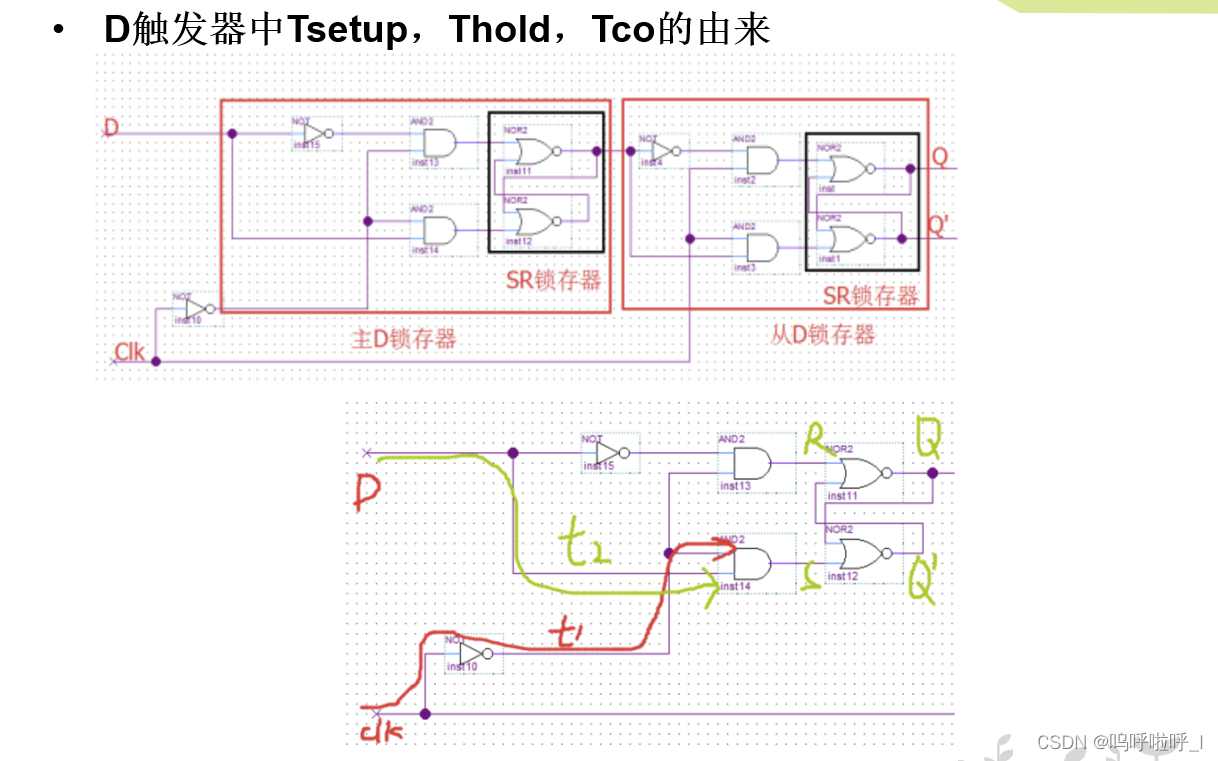

(1)D触发器中Tsetup、Thold、Tco

关于建立时间、保持时间、Tco的由来详见下面这篇文章:

FPGA建立时间、保持时间原理总结_fpga建立时间和保持时间-CSDN博客

- 观察图中主锁存器,clk为0时主锁存器开启从锁存器关闭,当clk为1时主锁存器的两个与门被关闭掉,此时必须保证数据已被打入到锁存器的输出,由于路径上存在非门、与门、或非门,因此输入信号要提早到达,这便是建立时间Tsetup的由来;

- Thodld处,当clk由0变为1时,由于路径上存在门,会有延时t1导致与门并没有立刻被关掉,而此时如果输入发生变化他会立刻反映到与门因为它的路径上只有布线延迟t2(t2<t1),这样就没有锁存到原来的数据就被替换掉了,这就是Thold的由来;

- Tco指的是时钟跳变沿采集到数据到输出数据稳定的时间,主要指的是从锁存器将数据从主锁存器的而输出传递到从锁存器输出所花费的时间;

(2)时序分析中的常用术语

时序分析中的常用术语

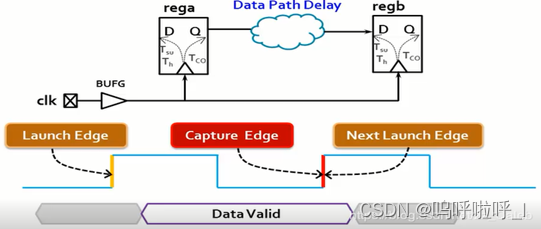

源时钟(Source Clock/Launch Clock,也称为发起时钟):rega时钟端连接的时钟;

目的时钟(Destination Clock/Capture Clock,也称为捕获时钟):目的寄存器时钟端连接的时钟;

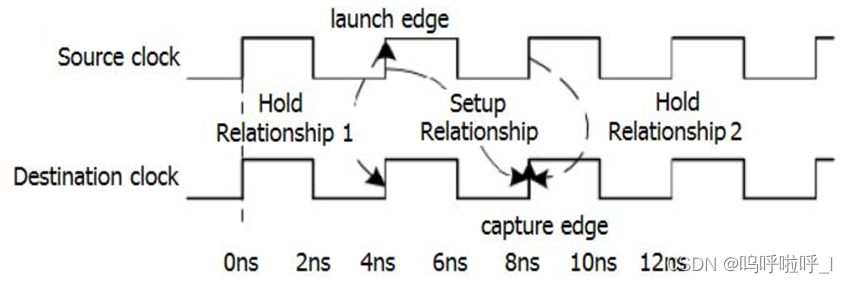

发起沿(launch edge,源时钟产生数据的有效时钟沿)产生数据指把数据从D端打到Q端;

捕获沿(capture edge,目的时钟捕获数据的有效时钟沿);

发起沿通常在0ns,捕获沿通常在下一个发起沿,发起沿和捕获沿通常相差一个时钟周期。

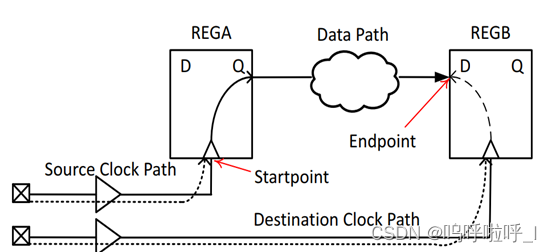

(3)一条普通时序路径的三要素

- 源时钟路径:从源时钟的源节点(通常是FPGA的时钟输入引脚)到源寄存器的时钟端口的路径。当时序路径的起点是FPGA输入端口时,该时序路径是没有源时钟路径的。

- 数据路径:从时序路径的起点到时序路径的终点之间的数据传播路径。时序路径的起点可以是源寄存器的时钟端口或FPGA的输入端口,时序路径的终点可以是目的寄存器的输入端口或FPGA的输出端口。

- 目的时钟路径:从目的时钟的源节点(通常是FPGA的时钟输入引脚)到目的寄存器的时钟端口的路径。当时序路径的终点是FPGA的输出端口时,该时序路径是没有目的时钟路径的。

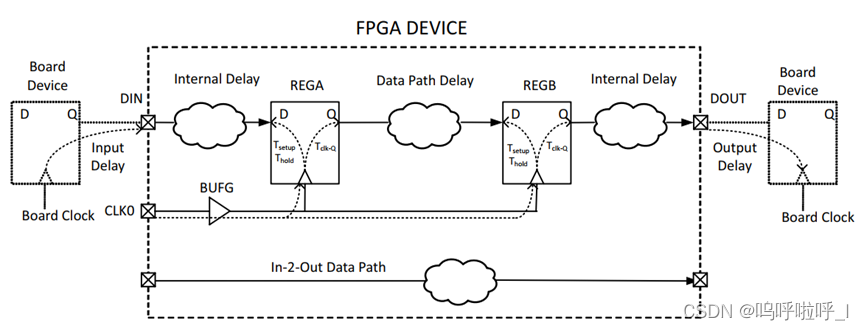

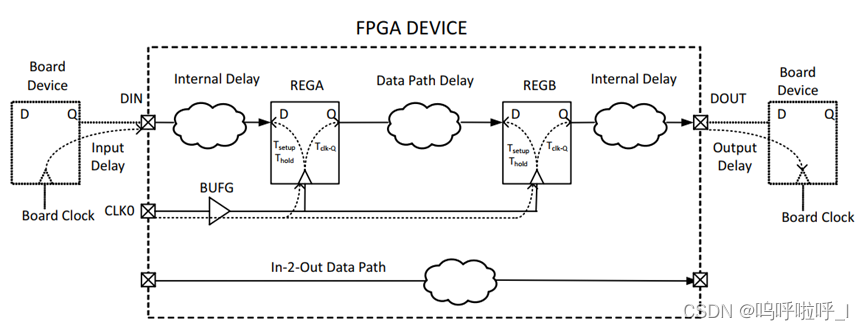

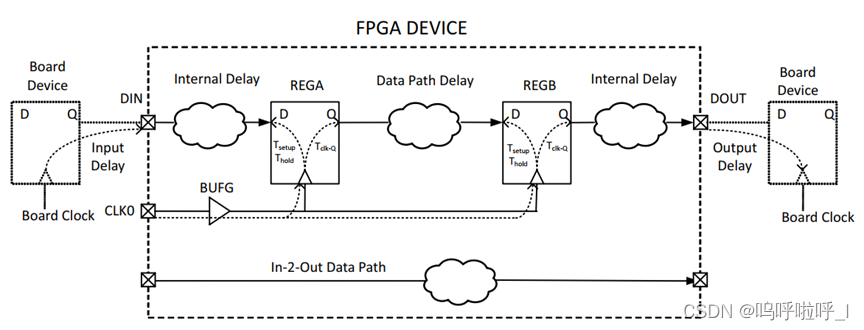

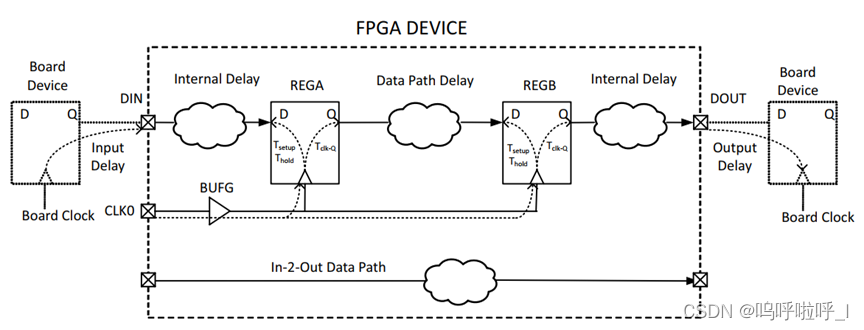

(4)FPGA中常见的四种时序路径

①从FPGA的输入端口到目的寄存器的****数据输入端口

- 数据由Board clock发起并在FPGA外部产生;

- 数据经过Input Delay的延迟后到达FPGA的输入端口;

- 这种路径是没有源时钟路径的,用户需要约束Input Delay和时钟来告知时序引擎必要信息,时序引擎才能正确的分析这种路径。

②从源寄存器的时钟端口到目的寄存器的数据输入端口

- 数据由源时钟发起并在FPGA内部产生;

- 数据经过Data Path Delay后到达由目的时钟驱动的目的寄存器;

- 这种时序路径是最常见的,用户需要约束源时钟和目的时钟告知时序引擎必要的信息,时序引擎才能正确的分析这种时序路径。

③从源寄存器的时钟端口到FPGA的输出端口

- 数据由源时钟发起并在FPGA内部产生;

- 数据经过Internal Delay后到达输出端口;经过Output Delay后被Board Clock捕获到;

- 这种路径是没有目的时钟路径的,用户需要约束Output Delay和时钟来告知时序引擎必要信息,时序引擎才能正确的分析这种路径。

④从FPGA的输入端口到FPGA的输出端口

- 数据横穿FPGA,没有经过任何触发器,这种路径也叫in-to-out path,约束输入和输出延时的参考时钟可以使用虚拟时钟。

- 这种路径中只有数据路径,用户需要约束Input Delay和Output Delay,告知时序引擎必要的信息,时序引擎才能正确的分析这种时序路径。

4.Setup检查

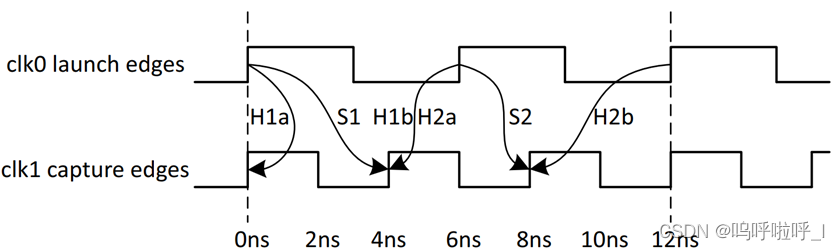

(1)确定建立时间要求

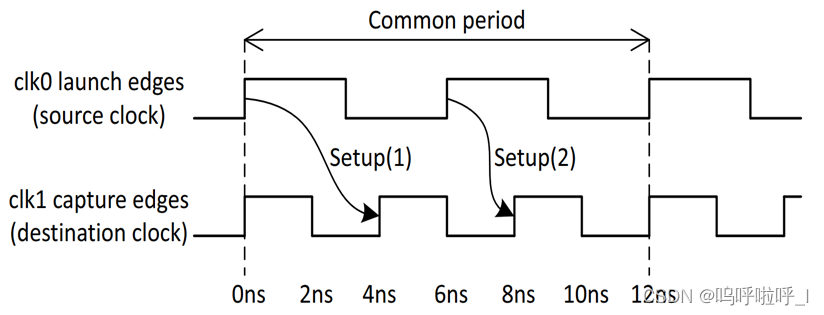

时序引擎会找出发起时钟和捕获时钟的最小公共周期,然后在最小公共周期内找到所有发起时钟沿和捕获时钟沿的所有可能的情况,并在所有可能的情况中挑选出最小的建立时间需求(大于0),从而确定了Launch edge和Capture edge。

在最小公共周期内,建立时间有多种可能,在于发起沿的选取。

注:如果最小的建立时间都能满足要求,那其余的建立时间也必定满足。

如图中setup(1)为4ns,setup(2)为2ns,因此选取setup(2)进行分析;

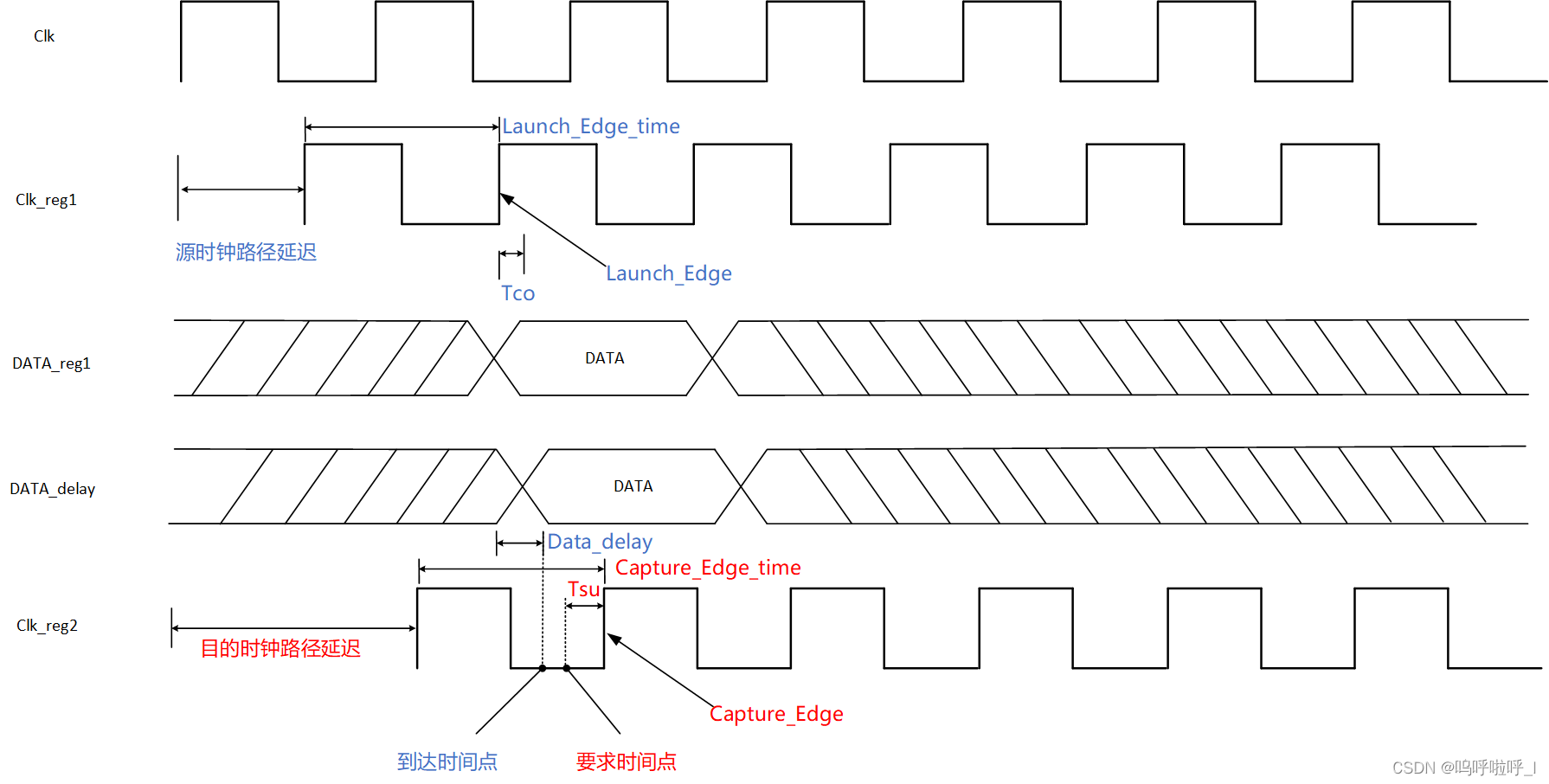

需要注意的是图中的数据路径延迟包含了Tco、布线及中间组合逻辑的延迟。

(2)计算数据的需求时间 / 到达时间 / Setup的裕量

①需求时间

在保证目的寄存器满足建立时间的标准的前提下,所能接受的数据到达的最晚时间点;

D a t a R e q u i r e d T i m e ( s e t u p ) = C a p t u r e e d g e t i m e + 目的时钟路径延迟 − c l o c k u n c e r t a i n t y − 建立时间 T s u \\Data Required Time (setup) = Captureedgetime+ 目的时钟路径延迟 - clock uncertainty\\ - 建立时间T_{su}\\ DataRequiredTime(setup)=Captureedgetime+目的时钟路径延迟−clockuncertainty−建立时间Tsu

②计算数据的到达时间

D a t a A r r i v a l T i m e ( s e t u p ) = l a u n c h e d g e t i m e + 源时钟路径延迟 + 数据路径延迟 Data Arrival Time ( setup) = launch edge time+ 源时钟路径延迟 + 数据路径延迟 DataArrivalTime(setup)=launchedgetime+源时钟路径延迟+数据路径延迟

③计算Setup的裕量(Slack)

S l a c k ( s e t u p ) = D a t a R e q u i r e d T i m e − D a t a A r r i v a l T i m e Slack ( setup )= Data Required Time - Data Arrival Time Slack(setup)=DataRequiredTime−DataArrivalTime

为负表明发生了时序违例;

(3)导致Setup slack为负的因素

① Setup Requirement 与实际情况不符

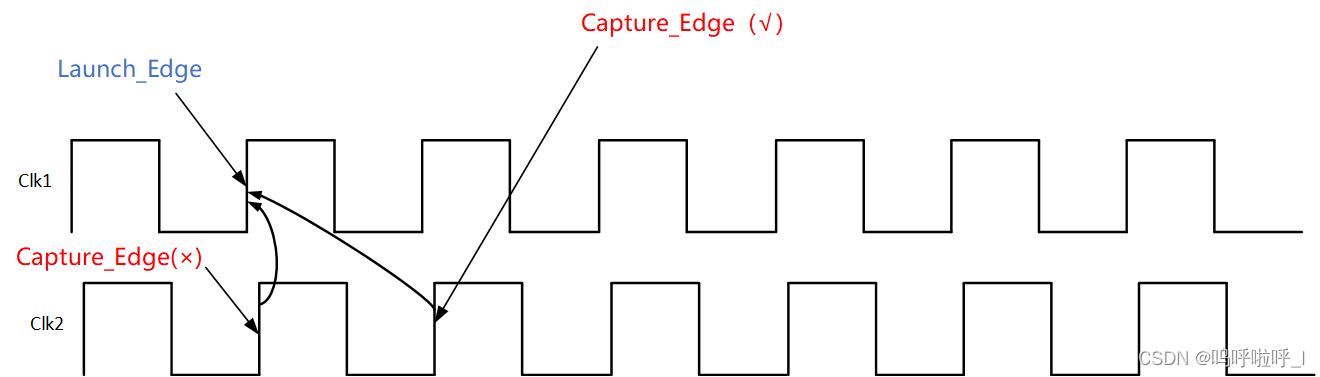

建立时间需求过小,这种情况通常会在同步跨时钟域路径中出现,在同步跨时钟域路径中的源时钟频率与目的时钟频率的相位关系虽然是已知的,但是时序引擎默认选择的捕获沿通常都是错误的,需要用户通过多周期路径约束的方式手动修正建立时间需求。比如下图中,两个同频不同相的同步时钟,时序引擎默认选择的捕获沿是目的时钟第二个上升沿,导致建立时间需求非常小,最终肯定会导致时序违例。

② clk skew为负值,且很大

通常情况下,同一个时钟下的时钟歪斜不应该超过300ps,同步跨时钟域路径的时钟歪斜不应该超过500ps,异步跨时钟域路径的时钟歪斜一般比较大,因为它们的时钟源不同。

当出现时钟歪斜大的情况时:

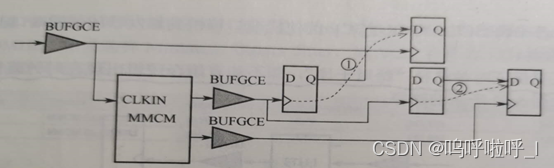

1.检查源时钟路径和目的时钟路径上是否干净,时钟路径上是否引入了组合逻辑,时钟路径是否使用了过多的BUFGCE导致时钟延时变大;

2.检查源时钟路径和目的时钟路径所经过的模块是否相同,比如源时钟路径上经过全局缓冲,MMCM,但是目的时钟路径上只经过了全局缓冲。如下图所示,第一条路径的源时钟路径上有BUFGCE/MMCM/BUFGCE,而目的时钟路径上只有BUFGCE,所以源时钟路径和目的时钟路径的延时不同,导致时钟歪斜较大,应该尽量避免此类路径。第二条路径的源时钟和目的时钟都是来源于同一个MMCM的不同的时钟,所以时钟歪斜较小。

经过MMCM会有相位补偿等,可能会导致延迟比上面的延迟还要小!

③Tsu/Tco大

当设计中使用Block(DSP/Block RAM等)时,应该要注意以下问题。对于以这些Block为时序路径的起点或终点的时序路径,这些Block的Tsu/Th/Tco都比普通的寄存器大,而且这些Block的布线延时和时钟歪斜比较大。所以当使用这些Block作为时序路径的终点时,它的起点一定要是触发器,比如说一个Block RAM的写数据信号,输入进Block前最好打一拍。当使用这些Block作为时序路径的起点时,应该使用Block 内部的输出寄存器,比如使用由Block RAM组成的FIFO时,尽量不要使用首字置出的,而使用打一拍后输出的,使用后者可以显著降低Tco。当时序路径为从一个Block到另一个Block时,中间需要进行打拍操作。当使用这些Block的控制端口时,应该保证这些控制信号的低扇出,如使用由Block RAM组成的FIFO时,应该尽量降低读/写能信/地址信号的扇出。

5.Holdup检查

(1)确定保持时间要求

保持时间要求是以建立时间要求为基础的,保持时间要求有两种:

- 当前建立时间的发起沿产生的数据不能被当前建立时间的捕获沿的前一个有效沿捕获;

- 当前建立时间发起沿的下一个有效沿产生的数据不能被当前建立时间的捕获沿捕获

根据所有的建立时间需求找到所有的保持时间需求,并从保持时间需求(可正可负)中找到最大的保持时间需求。

(2)计算数据的需求时间 / 到达时间 / 保持时间裕量

①需求时间

D a t a R e q u i r e d T i m e ( h o l d ) = 捕获时间 + 目的是中路劲延迟 + c l o c k u n c e r t a i n t y + h o l d t i m e Data Required Time (hold) = 捕获时间 + 目的是中路劲延迟 + clock uncertainty\\ + hold time DataRequiredTime(hold)=捕获时间+目的是中路劲延迟+clockuncertainty+holdtime

②计算数据的到达时间

D a t a A r r i v a l T i m e ( h o l d ) = 发起时间 + 源时钟路径延迟 + 数据延迟 Data Arrival Time (hold) = 发起时间 + 源时钟路径延迟 + 数据延迟 DataArrivalTime(hold)=发起时间+源时钟路径延迟+数据延迟

③计算Hold up的裕量(slack)

S l a c k ( h o l d u p ) = D a t a A r r i v a l T i m e − D a t a R e q u i r e d T i m e Slack ( holdup )= Data Arrival Time-Data Required Time Slack(holdup)=DataArrivalTime−DataRequiredTime

(3)导致Holdup slack为负的原因

- 保持时间需求大于0(通常由时序引擎选择错误的捕获沿导致)

- 时钟歪斜大于300ps(通常由时钟路径上的组合逻辑导致)

- Th过大(通常由时序路径终点为Block导致)

- Hold up Slack为负的情况比较少见,当SetupSlack有较大裕量时,通常工具会自动插入延时来增加Holdup Slack。

5390

5390

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?