Update: 2022 / 10 / 11

USB | 2. 最新USB 4.0规范解析及一致性测试

目录

参考这里 1

- 背景

- 概念

- 测试的实现

背景

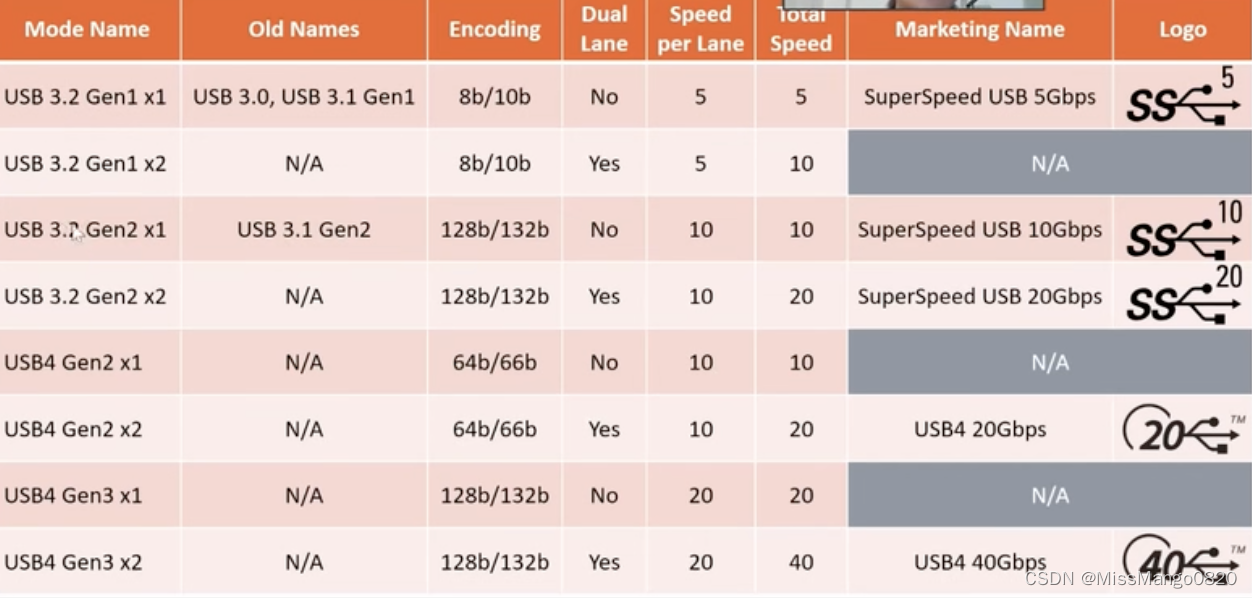

USB 1.0 ~ 4.0

USB 的 4 代发展如下,

Type-C

Type-C 一统此前的接口, 如下:

接口

接口形式如下:

拓扑结构

| Port口 | 描述. |

|---|---|

DFP | Downstream face port,面向下游,即从 host 面向 devcie |

UFP | Upstream face port,面向上游,即从 device 面向 host |

host 端上都是面向 device 的 DFP,

device 端上都是面向 host 的 UFP。

USB hub 端上有1个 UFP 和若干个 DFP。

USB 4

工作原理的阶段大致如下:

| SPEC | 作用 |

|---|---|

USB Type-C Spec | 其规定: 1. 对设备接入的检测,是正插还是反插?; 2. 通过USB总线 Bus 对自身不带电源的USB设备进行 VBus 电源初始化,即供电 |

USB PD 3.0 Spec | 其规定: 1. 在 host / device 间协商电源契约,即 Power Contract。比如一个USB 4.0 产品插入 host 上,USB 4.0 产品会告知 host 要多大的电压、电流; 2. 进行模式的选择:在USB 4.0上有很多模式的选择,故在此处进行模式的确定,比如确定作为 USB 设备进行使用。 |

USB 4 Spec | 其规定: 设备枚举 |

USB4 PHY CTS | |

USB 2.0 CTS |

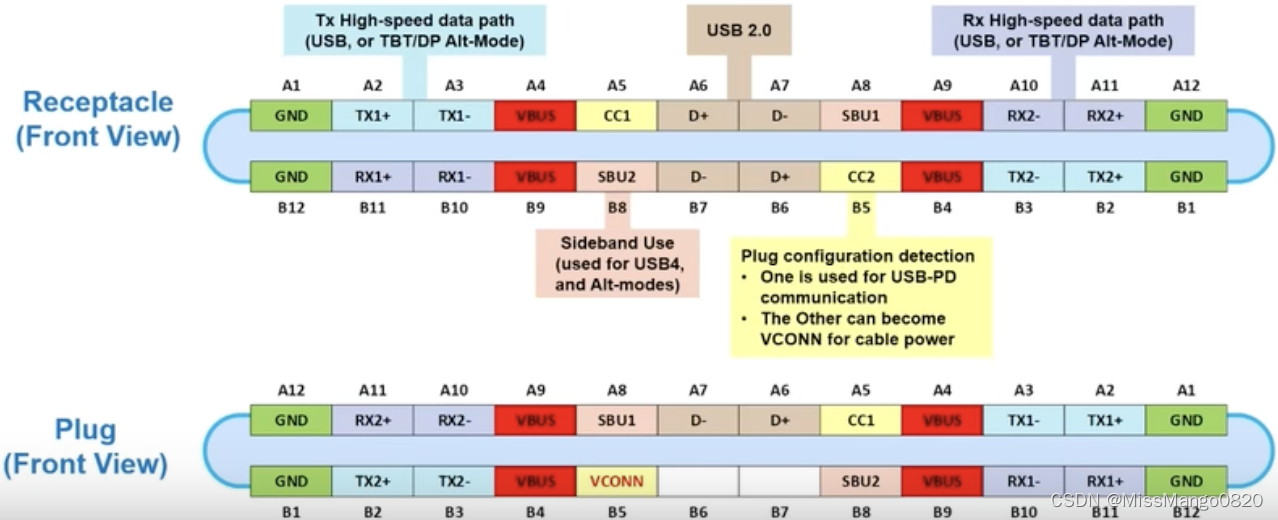

USB Type-C

引脚是中心轴对称分布的,故可以保证无论正插还是反插都可以工作。

Plug 原理

当 Plug 插入 Receptacle 中,Receptacle 端的 Rp 上拉电阻与 Rd 端的 Rd 下拉电阻通过 CC 线连接并导通,可以在 cable 的两端检测到电压差,通过检查电压差异可以判断 CC 连接线是通过哪2个 pin 脚连通的,进而判断插入方向。

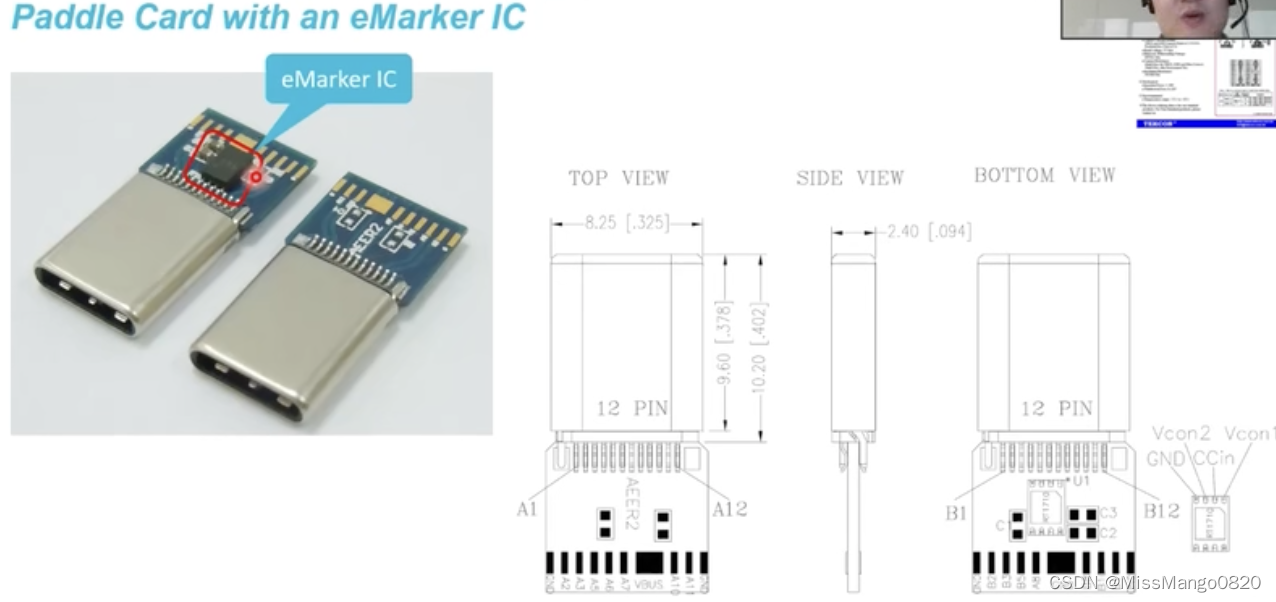

USB全特性Type-C线缆有一个 eMarker IC。Plug 的 Vconnector 即对 eMarkder IC 供电,eMarker IC 可以告诉 host 和 device 线缆的能力,比如支持到 20 GB/s。

Single Plane Configuration

当 host 检测到 CC1 被端接,从而配置 TX1 / RX1 发送数据;device 也检测到 CC1 被端接,从而 MUX 选通到 TX1 / RX1。

当 host 检测到 CC1 被端接,从而配置 TX1 / RX1 发送数据;devcie 检测到 CC2 被端接,从而 MUX 选通到 TX2 / RX2。

当 host 检测到 CC2 被端接,从而配置 TX2 / RX2 发送数据;devcie 检测到 CC2 被端接,从而 MUX 选通到 TX2 / RX2。

Dual Plane Configuration

当 host 检测到 CC1 被端接,从而配置 TX1 / RX1 为 host 侧的 Lane 0,TX2 / RX2 为 Lane 1;

devcie 检测到 CC1 被端接,从而 MUX 选通到 TX1 / RX1,TX2 / RX2 通过 MUX 选通到 Lane 1。

当 host 检测到 CC1 被端接,从而配置 TX1 / RX1 为 host 侧的 Lane 0,TX2 / RX2 为 Lane 1;

devcie 检测到 CC2 被端接,从而 TX2 / RX2 从 MUX 选通到 TX1 / RX1(Lane0),TX1 / RX1 通过 MUX 选通到 Lane 1。

当 host 检测到 CC2 被端接,从而配置 TX2 / RX2 为 host 侧的 Lane 0,TX1 / RX1 为 Lane 1;

devcie 检测到 CC2 被端接,从而 TX2 / RX2 从 MUX 选通到 TX2 / RX2(Lane0),TX1 / RX1 通过 MUX 选通到 Lane 1。

USB PD

USB4 Router

在一种协议中传输另外一种协议的内容,称为 thunder port。

怎么实现的呢?如下:

对于 USB 2.0 的传输,需要在 Host Router 中含有 USB 2.0 Host;

对于 PCIe 的传输,需要在 Host Router 中含有 PCIe Controller;

对于 DP 的传输,需要在 Host Router 中含有 DP Source。

经过集成化后,原理如下:

一个 Router 的本质是一个功能非常复杂的开关,分时切换不同的协议,从而完成不同协议的传输。

Lane Adaptor 物理通路适配器,理解为一个 USB 4.0 的 PHY。

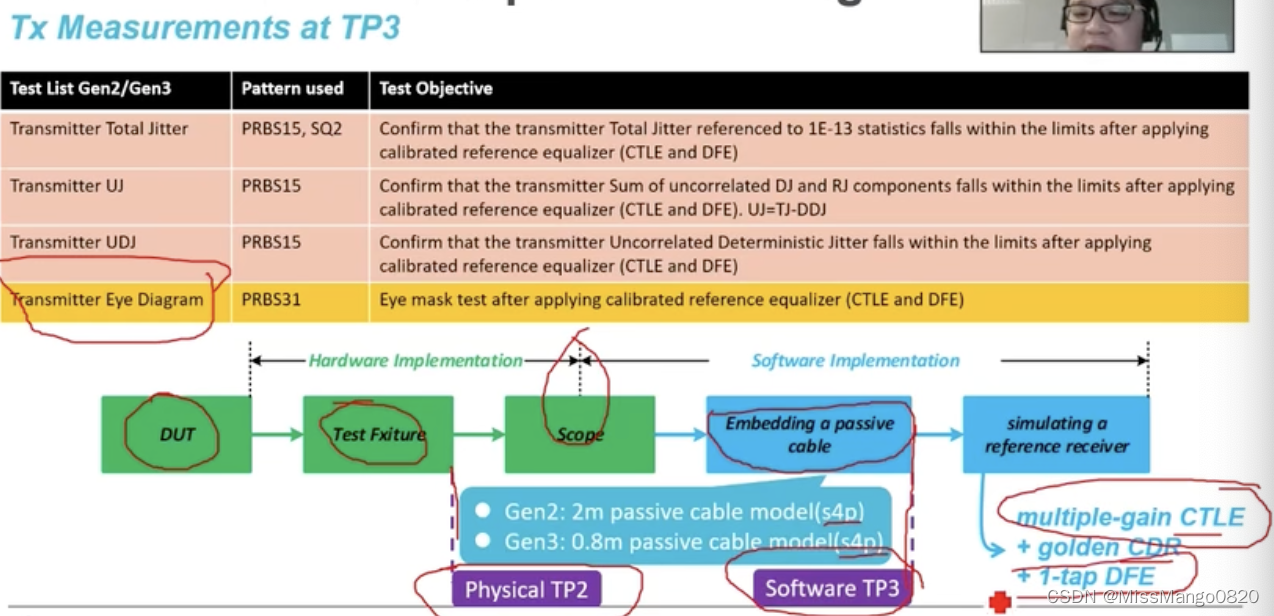

USB4 PHY

典型 SerDes 架构:

- 逻辑层

PCS; - 电气层

PMA;

可以在 Single Plane Configuration 或者 Dual Plane Configuration 模式下工作。

Side band channel 边带信道可以实现物理通路的初始化,保证锁定和位对齐等的实现,如下:

逻辑层

逻辑层主要用来信令的编码,以及,比如会传一些 skip码 skip码用来保证数据不丢失;也会传一些扰码。

电气层

电气层的一大问题是 channel loss,使得信号边缘变缓,电压幅度接近,在 Rx 端分不清 0 和 1。

至此,引入均衡技术 Equalization。均衡技术主要分为3部分,在 Tx 端有 FFE,在 Rx 端有 CTLE 和 DFE。

FFE

主要是在电压要变时让电压高一些,来使电压衰减。

Insertion Loss

主机和设备的损耗预算是一样的。

USB4 认证需求

2689

2689

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?