什么是PCIE

PCIe,全称Peripheral Component Interconnect Express,是一种高速串行计算机扩展总线标准,用于连接计算机内部的硬件组件,如显卡、存储设备、网络适配器等。PCIe是一种点对点的双向通信标准,这意味着它在发送和接收方向上都提供专用的信道,与传统的PCI总线相比,PCIe提供了更高的带宽和更低的延迟。

PCIE设备长什么样

比如这是一张虚假的显卡

虽然上图内容是假的, 但还是很形象的.

带宽

PCI Express (PCIe) 是一种高速串行计算机扩展总线标准,用于连接主板上的各种硬件组件,如显卡、存储设备和网络适配器等。PCIe带宽主要由以下几个因素决定:

- 版本:

-

PCIe 1.0:最初版本,每个通道的原始数据传输速率为

2.5 GT/s(Giga Transfers per second),考虑到8b/10b编码的效率,实际数据传输速率为250 MB/s。 -

PCIe 2.0:将每个通道的原始数据传输速率翻倍至

5.0 GT/s,实际数据传输速率为500 MB/s。 -

PCIe 3.0:再次将每个通道的原始数据传输速率翻倍至

8.0 GT/s,实际数据传输速率为1 GB/s。 -

PCIe 4.0:继续将每个通道的原始数据传输速率翻倍至

16.0 GT/s,实际数据传输速率为2 GB/s。 -

PCIe 5.0:每个通道的原始数据传输速率提升至

32.0 GT/s,实际数据传输速率为4 GB/s。 -

通道数(

lane count): -

PCIe插槽有不同的通道数,表示为x1、x2、x4、x8、x16等。通道数越多,带宽越高。 -

例如,一个

PCIe 3.0 x16插槽的总带宽为16 × 1 GB/s = 16 GB/s(双向,即上行和下行总和),单向带宽为8 GB/s。 -

方向性:

-

PCIe带宽通常是双向的,这意味着数据可以同时在两个方向上传输,增加了一倍的有效带宽。

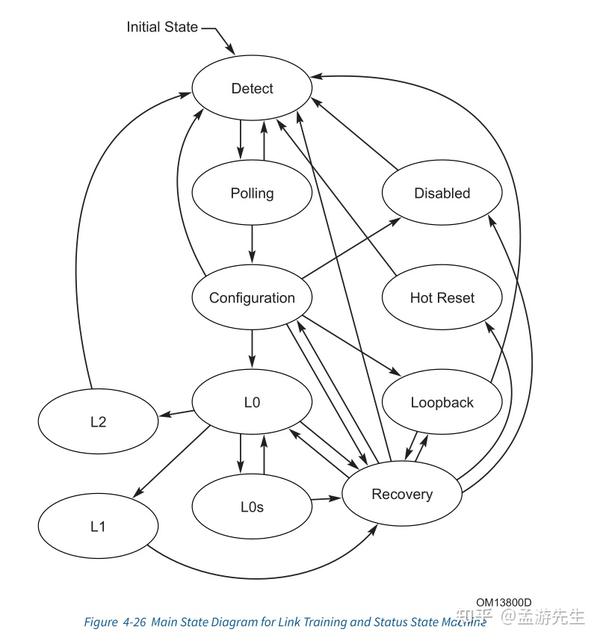

PCIE链路状态

包括detect, polling, configuration等, 大致了解下先. 在固件下需要做PCIE设备的链接, 就是从detect状态切换至L0状态.

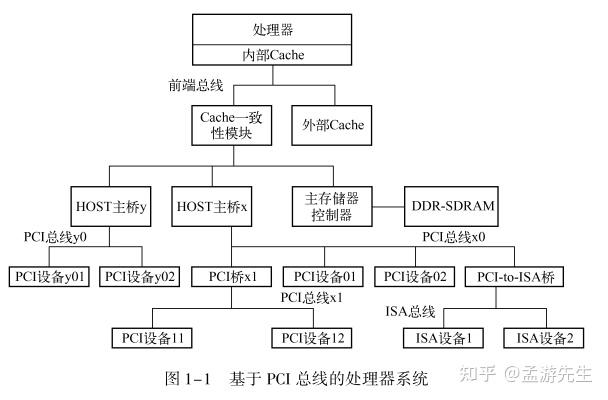

PCIE总线的组织结构

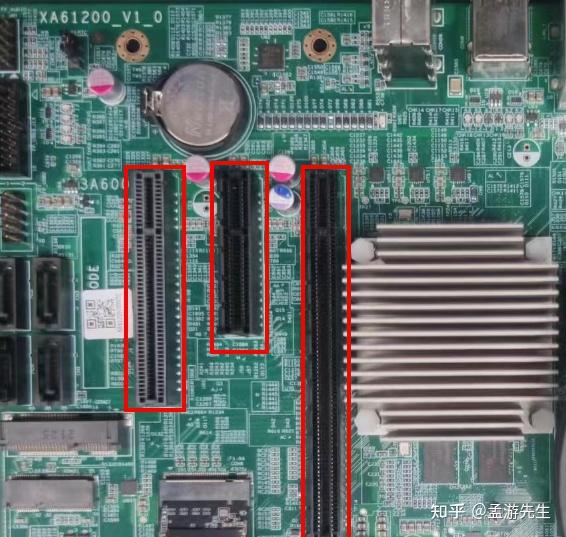

图中与 PCI 总线相关的模块包括: HOST 主桥、 PCI 总线、 PCI 桥和 PCI 设备。在 PCI 总线中有三类设备: PCI Agent 设备和桥设备。如PCIE的网卡, 显卡, RAID卡等, 均属于PCIE的Agent 设备. 而其插槽, 就可以认为是一个PCIE桥设备. 插槽通常如下图:

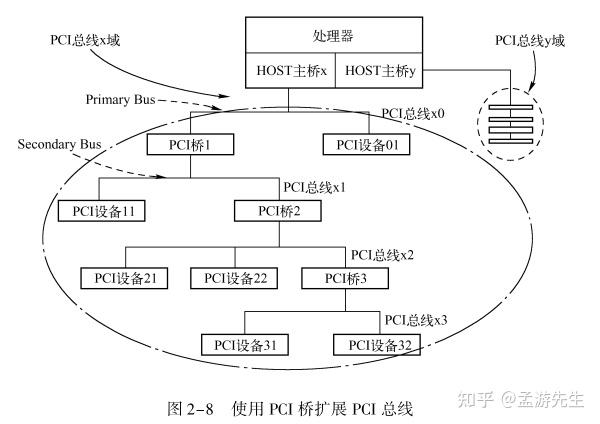

Type0和Type1

PCI 总线定义了两类配置请求, 一类是 Type 00h 配置请求, 另一类是 Type 01h 配置请求。 PCI 总线使用这些配置请求访问 PCI 总线树上的设备配置空间, 包括 PCI 桥和 PCI Agent设备的配置空间。

其中 HOST 主桥或者 PCI 桥使用 Type 00h 配置请求, 访问与 HOST 主桥或者 PCI 桥直接相连的 PCI Agent 设备或者 PCI 桥; 而 HOST 主桥或者 PCI 桥使用 Type 01h 配置请求, 需要至少穿越一个 PCI 桥, 访问没有与其直接相连的 PCI Agent 设备或者 PCI 桥。如下图所示, HOST 主桥可以使用 Type 00h 配置请求访问 PCI 设备 01, 而使用 Type 01h 配置请求通过 PCI 桥 1、 2 或者 3 转换为 Type 00h 配置请求之后, 访问 PCI 总线树上的 PCI 设备 11、 21、22、 31 和 32 。

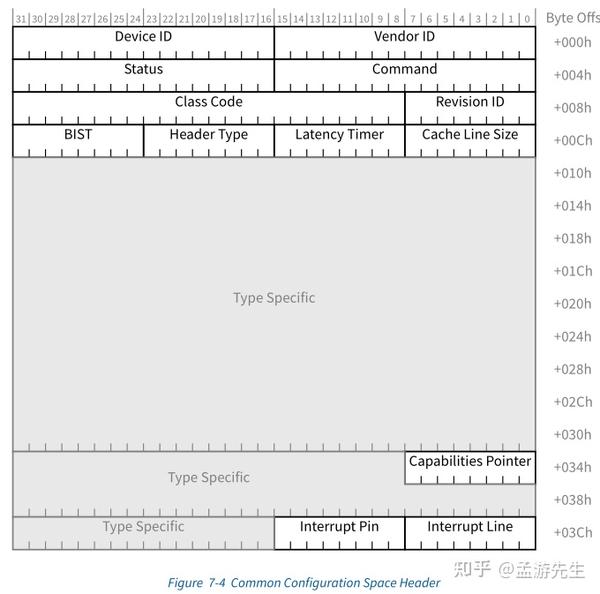

配置空间

共同点

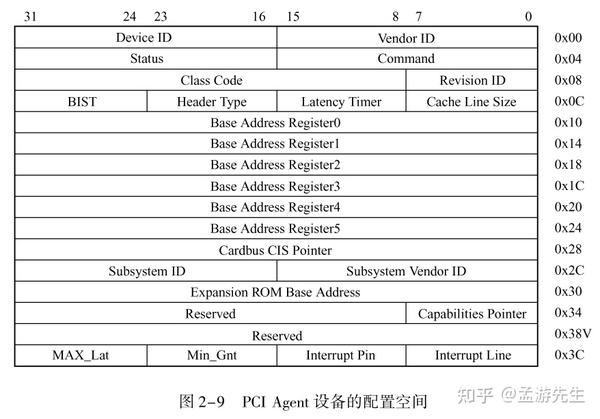

Pci Agent 设备配置空间

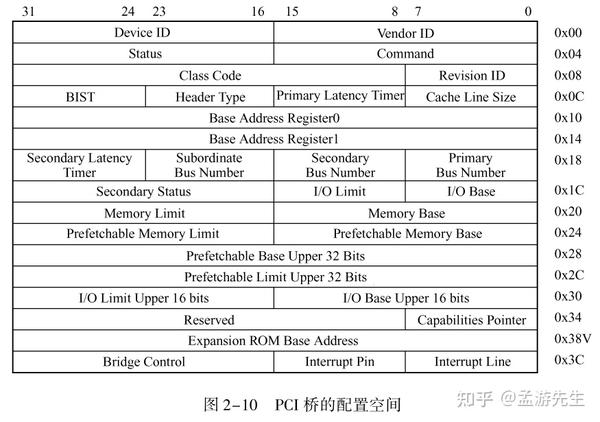

Pci 桥设备配置空间

其中相应寄存器含义可结合PCIE手册查看其详细含义.

上面说的配置空间通常只描述地址范围为 0x00 ~ 0x3F的寄存器, 这 64 个字节是所有 PCI 设备必须支持的。 事实上,许多 PCI 设备也仅支持这 64 个配置寄存器。

此外 PCI / PCI⁃X 和 PCIe 设备还扩展了 0x40~0xFF 这段配置空间, 也属于标准配置空间, 叫做能力寄存器, 即PCI Express Capability. 在这段空间主要存放一些与 MSI 或者 MSI⁃X 中断机制和电源管理相关的 Capability 结构。

身为软件开发人员, 要了解基本的配置空间中的寄存器含义, 比如

Vendor ID指厂商,Class Code指设备类型等. 软件开发时一定会根据相应的设备类型或厂商信息做适配.

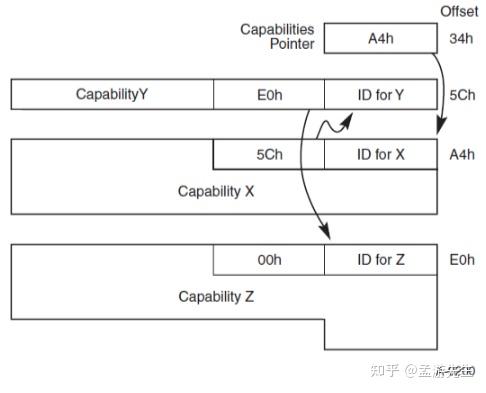

Capabilities

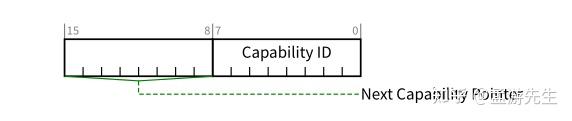

Capabilities其实就是一个单向链表. 0x34寄存器中的值是第一个capability在配置空间中的偏移, 如下图, 先0xA4处是第一个capability, 0x5C是第二个capability. 以此类推, 直至找到0x10(PCIE能力标识)或一个都没找到后结束.

每个Capability的结构如下图:

其中Capability ID表明此Capability的类型. 相关类型可参考如下代码:

/* Capability lists */

#define PCI_CAP_LIST_ID 0 /* Capability ID */

#define PCI_CAP_ID_PM 0x01 /* Power Management */

#define PCI_CAP_ID_AGP 0x02 /* Accelerated Graphics Port */

#define PCI_CAP_ID_VPD 0x03 /* Vital Product Data */

#define PCI_CAP_ID_SLOTID 0x04 /* Slot Identification */

#define PCI_CAP_ID_MSI 0x05 /* Message Signalled Interrupts */

#define PCI_CAP_ID_CHSWP 0x06 /* CompactPCI HotSwap */

#define PCI_CAP_ID_PCIX 0x07 /* PCI-X */

#define PCI_CAP_ID_HT 0x08 /* HyperTransport */

#define PCI_CAP_ID_VNDR 0x09 /* Vendor-Specific */

#define PCI_CAP_ID_DBG 0x0A /* Debug port */

#define PCI_CAP_ID_CCRC 0x0B /* CompactPCI Central Resource Control */

#define PCI_CAP_ID_SHPC 0x0C /* PCI Standard Hot-Plug Controller */

#define PCI_CAP_ID_SSVID 0x0D /* Bridge subsystem vendor/device ID */

#define PCI_CAP_ID_AGP3 0x0E /* AGP Target PCI-PCI bridge */

#define PCI_CAP_ID_SECDEV 0x0F /* Secure Device */

#define PCI_CAP_ID_EXP 0x10 /* PCI Express */

#define PCI_CAP_ID_MSIX 0x11 /* MSI-X */

#define PCI_CAP_ID_SATA 0x12 /* SATA Data/Index Conf. */

#define PCI_CAP_ID_AF 0x13 /* PCI Advanced Features */

#define PCI_CAP_ID_EA 0x14 /* PCI Enhanced Allocation */

#define PCI_CAP_ID_MAX PCI_CAP_ID_EA

#define PCI_CAP_LIST_NEXT 1 /* Next capability in the list */

#define PCI_CAP_FLAGS 2 /* Capability defined flags (16 bits) */

#define PCI_CAP_SIZEOF 4

比较常用的是PCI_CAP_ID_EXP, 表明其为PCIE的Capability, 还有MSI等中断相关的Capability.

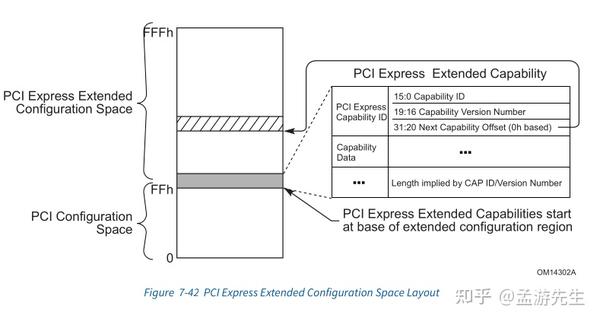

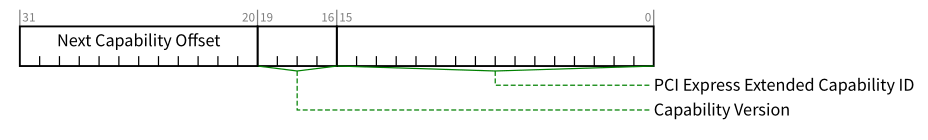

扩展配置空间

Extended Capabilities

从0x100开始到0x1000的范围则是PCIE的扩展配置空间. 如下图

和标准的Capability类似, 其也是一个单向链表, 不过是从0x100处开始是第一个. 直到Next Capability Offset为0时结束.

其具体结构如下:

其中PCI Express Extended Capability ID表明此扩展Capability的类型. 相关类型可参考如下代码:

#define PCI_EXT_CAP_ID_ERR 0x01 /* Advanced Error Reporting */

#define PCI_EXT_CAP_ID_VC 0x02 /* Virtual Channel Capability */

#define PCI_EXT_CAP_ID_DSN 0x03 /* Device Serial Number */

#define PCI_EXT_CAP_ID_PWR 0x04 /* Power Budgeting */

#define PCI_EXT_CAP_ID_RCLD 0x05 /* Root Complex Link Declaration */

#define PCI_EXT_CAP_ID_RCILC 0x06 /* Root Complex Internal Link Control */

#define PCI_EXT_CAP_ID_RCEC 0x07 /* Root Complex Event Collector */

#define PCI_EXT_CAP_ID_MFVC 0x08 /* Multi-Function VC Capability */

#define PCI_EXT_CAP_ID_VC9 0x09 /* same as _VC */

#define PCI_EXT_CAP_ID_RCRB 0x0A /* Root Complex RB? */

#define PCI_EXT_CAP_ID_VNDR 0x0B /* Vendor-Specific */

#define PCI_EXT_CAP_ID_CAC 0x0C /* Config Access - obsolete */

#define PCI_EXT_CAP_ID_ACS 0x0D /* Access Control Services */

#define PCI_EXT_CAP_ID_ARI 0x0E /* Alternate Routing ID */

#define PCI_EXT_CAP_ID_ATS 0x0F /* Address Translation Services */

#define PCI_EXT_CAP_ID_SRIOV 0x10 /* Single Root I/O Virtualization */

#define PCI_EXT_CAP_ID_MRIOV 0x11 /* Multi Root I/O Virtualization */

#define PCI_EXT_CAP_ID_MCAST 0x12 /* Multicast */

#define PCI_EXT_CAP_ID_PRI 0x13 /* Page Request Interface */

#define PCI_EXT_CAP_ID_AMD_XXX 0x14 /* Reserved for AMD */

#define PCI_EXT_CAP_ID_REBAR 0x15 /* Resizable BAR */

#define PCI_EXT_CAP_ID_DPA 0x16 /* Dynamic Power Allocation */

#define PCI_EXT_CAP_ID_TPH 0x17 /* TPH Requester */

#define PCI_EXT_CAP_ID_LTR 0x18 /* Latency Tolerance Reporting */

#define PCI_EXT_CAP_ID_SECPCI 0x19 /* Secondary PCIe Capability */

#define PCI_EXT_CAP_ID_PMUX 0x1A /* Protocol Multiplexing */

#define PCI_EXT_CAP_ID_PASID 0x1B /* Process Address Space ID */

#define PCI_EXT_CAP_ID_DPC 0x1D /* Downstream Port Containment */

#define PCI_EXT_CAP_ID_L1SS 0x1E /* L1 PM Substates */

#define PCI_EXT_CAP_ID_PTM 0x1F /* Precision Time Measurement */

#define PCI_EXT_CAP_ID_MAX PCI_EXT_CAP_ID_PTM

设备自己的特性配置

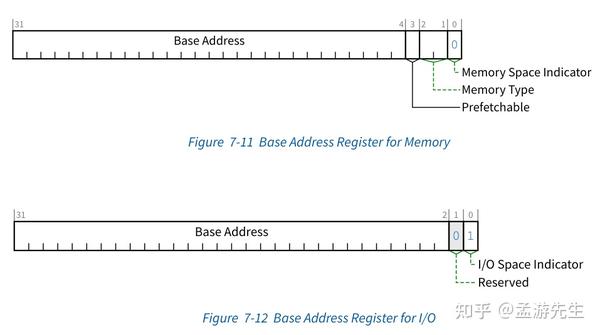

在PCI的配置空间中, 有若干个寄存器叫做Base Address Registers, 简称BAR, 这里通常是设备本身的相关配置所在的位置.

BAR

其结构如下:

向里面写全

1后再读可以获得其空间大小哦

Option Rom

也就是Pci Agent 设备配置空间中有的Expansion ROM Base Address, 是设备自身的boot code, 用作自身初始化, 善于使用有奇效.(倒也没必要特别关注)

参考文献

- PCI Express® Base Specification Revision 5.0 Version 1.0

- [内核源码](GitHub - loongson-community/linux-loongnix: Source from pkg.loongnix.cn)

- 《PCI Express 体系结构导读》

- 通义千问

- [豆包AI](豆包 - 你的 AI 朋友)

253

253

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?