1.PCIe概述

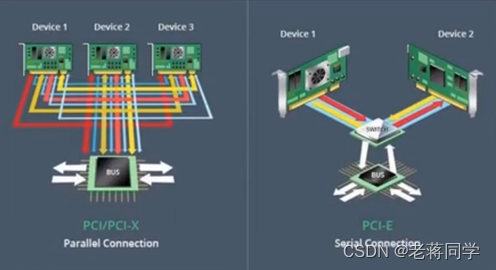

了解PCIe之前,绕不开PCI,因此,我们先介绍一下PCI。PCI(Peripheral Component Interconnect)是1991年英特尔公司推出的局部总线标准。采用并行总线结构,即在同一条总线上所有外设设备共享总线带宽,因此会出现抢占总线的情况,带宽有限。通讯速率较慢,其中地址线和数据线复用。下图中的白色框中的就是传统的PCI接口,上边是时间更长的ISA总线。

而PCIe采用的是点对点传输,串行通信,通信速率快,每个设备都独自拥有一条总线。如下图所示:

PCIe(peripheral component interconnect express)高速串行计算机扩展总线标准,是由英特尔公司2001年提出的。

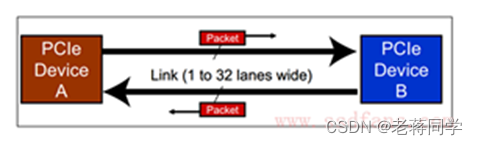

两个PCIe设备之间通信是串行通信的,如下图所示,即RX+ RX- TX+ TX-,即同一时刻既可以实现收数据,也可以发数据,以差分信号传输,具有一定的抗干扰能力。这四条线称为一个lane,其中PCIe最多支持32个Lane。

2.PCIe传输速度

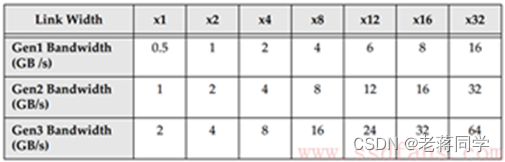

如上图所示,分别是PCIe1.0/2.0/3.0 X1 X2....X32的传输速度。

其中X1代表1条Lane,X2代表2条Lane...X16代表16条Lane。

PCIE 1.0 线上比特传输速率 2.5Gb/s,物理层使用的8/10编码,也就是8比特得到数据实际传输10比特;PCIE 2.0 线上比特传输速率 5Gb/s,物理层使用的也是8/10编码;PCIE 2.0 线上比特传输速率 8Gb/s,物理层使用的也是128/130编码。

所以

PCIE1.0 X1带宽 = (2.5Gb/s * 2(双向通道))/ 10 bit = 0.5GB/s。

本文详细介绍了PCIe(PCIExpress)的起源、传输速度提升、拓扑结构、分层架构、配置空间管理、功能模式以及TLP类型的多样性,展示了PCIe作为高性能计算机扩展总线的特性及其在现代IT系统中的重要性。

本文详细介绍了PCIe(PCIExpress)的起源、传输速度提升、拓扑结构、分层架构、配置空间管理、功能模式以及TLP类型的多样性,展示了PCIe作为高性能计算机扩展总线的特性及其在现代IT系统中的重要性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?