分频器是指使输出频率为输入频率的M分之一的数字电路,其中M为整数。下面介绍的是常用的50%占空比的分频器及Verilog代码:

偶分频

偶分频是指分频系数M为偶数的分频器。

现以4分频为例,即M=4.

module divider_even

#(parameter M = 4)(

input clk,

input rstn,

output reg clk_out

);

reg [2:0] count;

parameter N = M/2;

always@(posedge clk or negedge rstn)begin

if(!rstn)begin

clk_out <= 0;

count <= 3'b00;

end

else if(count == N-1)begin

clk_out <= ~clk_out;

count <= count + 1;

end

else if(count == M-1)begin

clk_out <= ~clk_out;

count <= 3'b000;

end

else begin

clk_out <= clk_out;

count <= count + 1;

end

end

endmodule

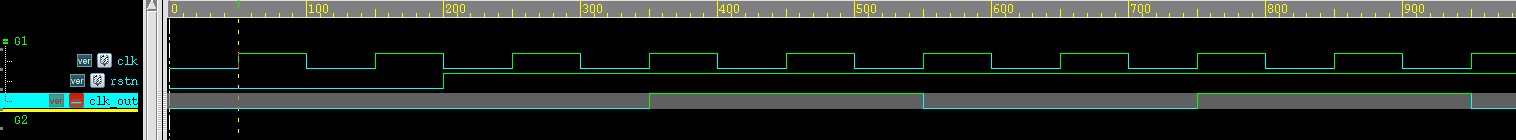

仿真波形:

奇分频

奇分频是指分频系数M为奇数,代码如下:

- 单个计数器

module divider_odd

#(parameter M = 5)(

input clk,

input rstn,

input clk_out

);

reg [2:0] count;

reg clk_1;

reg clk_2;

parameter N = (M-1)/2;

always@(posedge clk or negedge rstn)begin

if(!rstn)

count <= 0;

else if(count == (M-1))

count <= 0;

else

count <= count +1;

end

always@(posedge clk or negedge rstn)begin

if(!rstn)

clk_1 <= 0;

else if(count == N-1)

clk_1 <= ~clk_1;

else if(count == M-1)

clk_1 <= ~clk_1;

end

always@(negedge clk or negedge rstn)begin

if(!rstn)

clk_2 <= 0;

else if(count == N-1)

clk_2 <= ~clk_2;

else if(count == M-1)

clk_2 <= ~clk_2;

end

assign clk_out = clk_1 & clk_2;

endmodule

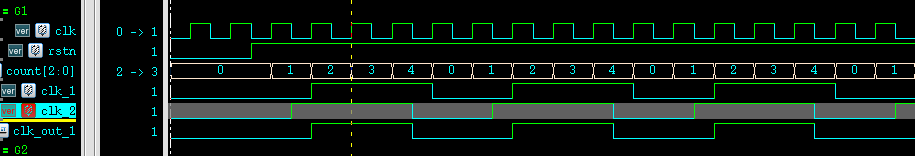

仿真波形

- 两个计数器

module divider_odd2

#(parameter M =5)(

input clk,

input rstnn,

output clk_out

);

reg [2:0] cont_1;

reg [2:0] cont_2;

reg clk_1;

reg clk_2;

parameter N = (M-1)/2;

always @ (posedge clk or negedge rstn)begin

if(!rstn)

cont_1 <= 0;

else if(cont_1==M-1)

cont_1 <=0;

else

cont_1 <= cont_1 + 1;

end

always @ (posedge clk or negedge rstn)begin

if(!rstn)

clk_1 <= 0;

else if(cont_1==N)

clk_1 <= ~clk_1;

else if(cont_1==M-1)

clk_1 <= ~clk_1;

end

always @ (negedge clk or negedge rstn)begin

if(!rstn)

cont_2 <= 0;

else if(cont_2==M-1)

cont_2 <=0;

else

cont_2 <= cont_2 + 1;

end

always@(negedge clk or negedge rstn)begin

if(!rstn)

clk_2 <= 0;

else if(cont_2==N)

clk_2 <= ~clk_2;

else if(cont_2==M-1)

clk_2 <= ~clk_2;

end

assign clk_out = clk_1 | clk_2;

endmodule

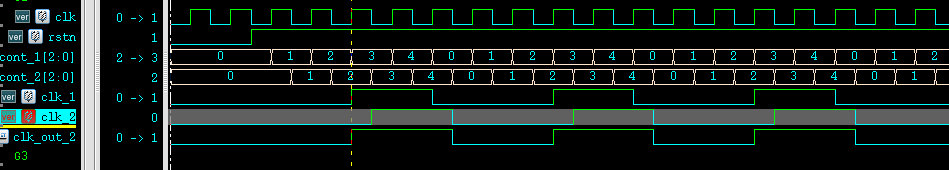

仿真波形

5236

5236

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?