FPGA开发全流程详解:从设计到烧录的终极指南

一、FPGA技术概述

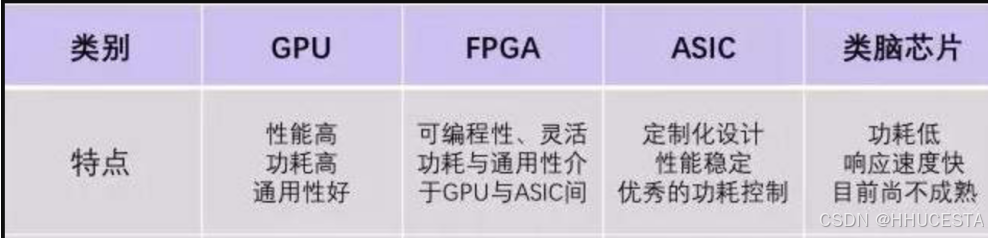

FPGA(Field-Programmable Gate Array)凭借其硬件可重构特性,在5G通信、人工智能加速和工业控制等领域广泛应用。与ASIC和CPU相比,FPGA兼具灵活性和高性能优势。

- 灵活性优势(相比ASIC)

硬件可重构性:FPGA的底层逻辑单元和互连资源可通过硬件描述语言(如Verilog/VHDL)实时编程,允许直接修改硬件电路结构,适应不同算法需求。这种“软硬件协同”能力使其能快速响应功能迭代(如通信协议更新、算法优化),而ASIC一旦流片则功能固定。

开发周期短:无需定制芯片,通过配置即可实现功能,适合原型验证和小批量场景。 - 高性能优势(相比CPU)

并行计算能力:FPGA通过硬件电路直接实现算法逻辑,可并行处理大量任务(如同时处理多个数据流),而CPU依赖顺序执行的指令集,性能受限于时钟频率和核心数量。

低延迟与高能效:FPGA的数据路径由硬件直接控制,无需经过操作系统和软件堆栈,减少了指令译码、内存访问等开销,在实时处理(如5G信号处理)和低功耗场景(如边缘计算)中表现突出。 - 平衡性应用场景

定制化加速:FPGA可针对特定算法(如AI推理、加密解密)设计专用数据通路,实现接近ASIC的效率,同时保留可重构性。

异构计算补充:常与CPU/GPU协同工作,承担高吞吐、低延迟任务,提升系统整体效能。

二、FPGA开发核心流程

1. 整体流程图

1. 功能定义/器件选型

核心任务:明确设计需求(如功能、性能、接口等),选择合适的FPGA芯片(如Xilinx、Intel、Lattice等厂商的型号)。

关键考量:

资源需求(逻辑单元、DSP、存储器、IO数量)。

功耗、成本、封装形式。

开发工具链支持(如Xilinx Vivado、Intel Quartus)。

2.设计输入

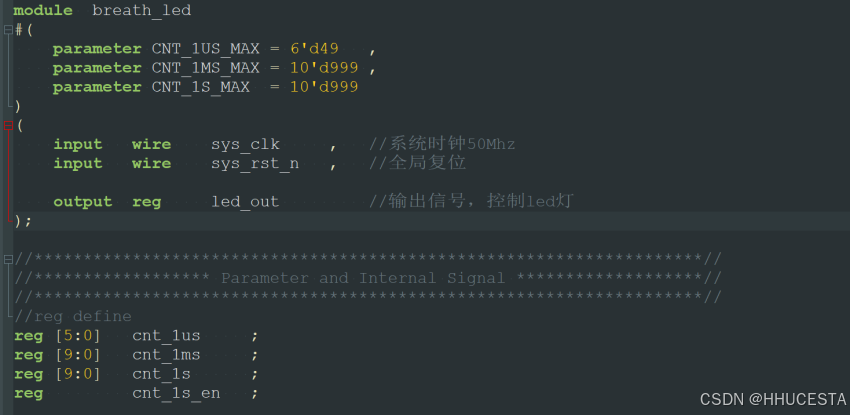

核心任务:将功能需求转化为硬件描述语言(HDL)代码(如Verilog、VHDL)或原理图设计。

常用工具:文本编辑器(如VS Code)或图形化输入工具(如Vivado IP Integrator)。

输出产物:RTL级代码(寄存器传输级)。

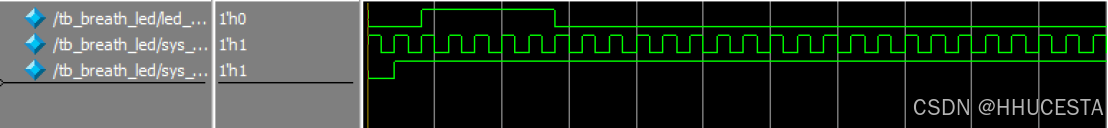

3. 功能仿真

核心任务:验证RTL代码的逻辑功能是否符合预期。

仿真工具:逻辑仿真器(如ModelSim、VCS、Xilinx ISim)。

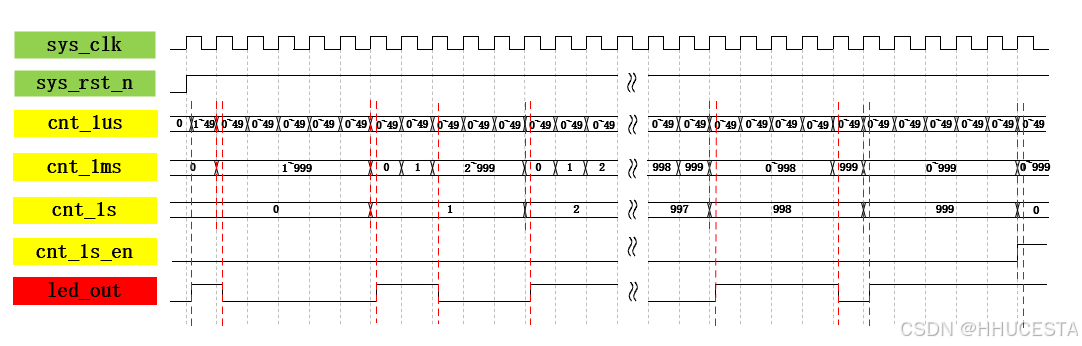

测试方法:编写测试激励(Testbench),通过波形图观察信号行为。

典型问题:逻辑错误、状态机跳转异常。

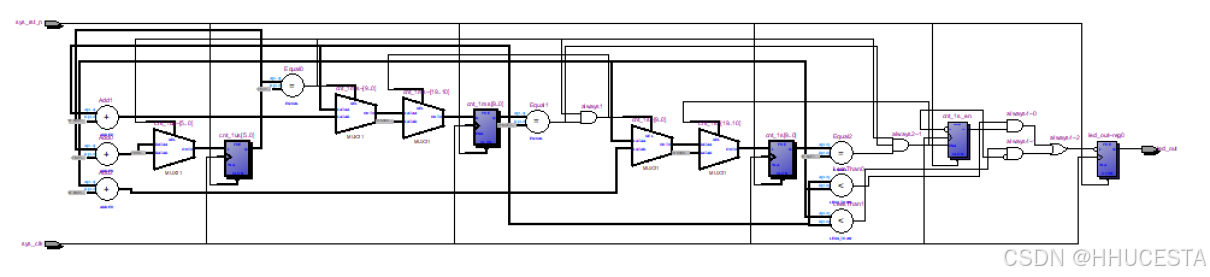

4. 综合优化

核心任务:将RTL代码转换为门级网表(逻辑门、触发器等),并进行逻辑优化。

关键工具:逻辑综合器(如Synopsys Synplify、Xilinx XST)。

优化目标:减少资源占用、提高时序性能。

输出产物:网表文件(如EDIF格式)。

5. 综合后仿真

核心任务:验证综合后的网表是否保留原始设计功能。

工具与方法:仍使用逻辑仿真器,但需加载综合后的网表与标准单元库模型。

注意点:仿真速度较慢,需关注综合工具引入的优化是否导致功能偏差。

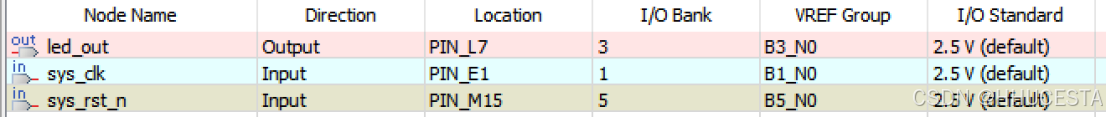

6. 布局布线(Place & Route)

核心任务:将门级网表映射到FPGA的物理资源(如CLB、DSP、Block RAM),并完成信号走线。

关键工具:FPGA厂家开发工具(如Vivado、Quartus)。

核心挑战:平衡时序收敛与资源利用率,解决布线拥塞问题。

输出产物:比特流文件(.bit/.sof)。

7. 静态时序分析(STA)

核心任务:在不依赖仿真的情况下,分析设计是否满足时序约束(如时钟频率、建立/保持时间)。

工具支持:集成在FPGA开发工具中(如Vivado Timing Analyzer)。

关键输入:时序约束文件(SDC格式)。

典型问题:关键路径时序违例、时钟域交叉(CDC)风险。

8. 时序仿真

核心任务:结合布局布线后的实际延迟信息(SDF文件),验证设计在真实时序下的行为。

工具与方法:逻辑仿真器加载带延迟的网表,验证时序敏感场景(如高速接口)。

注意点:仿真耗时长,通常仅针对关键模块。

9. 板级仿真与验证

核心任务:将比特流文件下载至FPGA开发板,进行硬件实测。

验证内容:

功能正确性(如外设驱动、通信协议)。

时序稳定性(如高频时钟下的信号完整性)。

常用工具:逻辑分析仪(如Saleae)、示波器、FPGA片内调试工具(如ChipScope)。

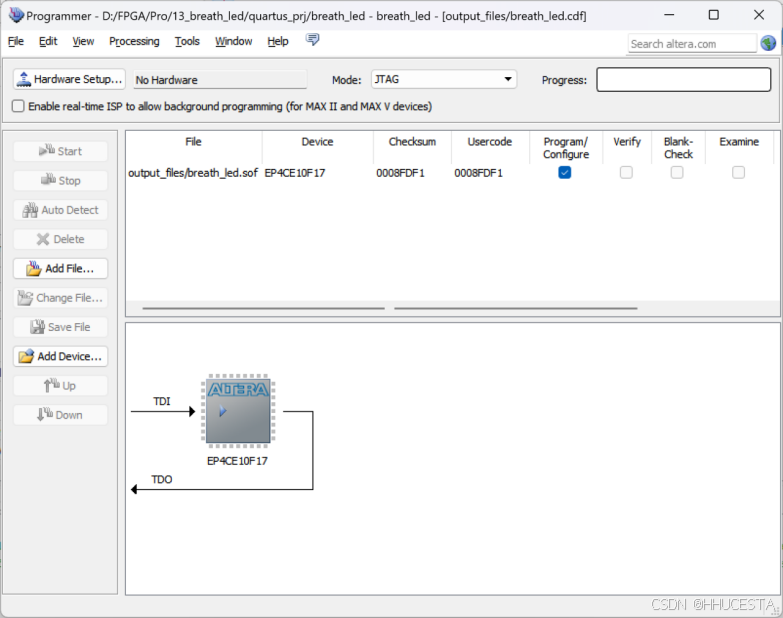

10. 芯片烧录与调试

核心任务:将最终设计固化到FPGA(或Flash芯片),并进行长期稳定性测试。

烧录方式:通过JTAG、SPI接口或专用配置芯片。

调试手段:

在线调试(如Vivado Hardware Manager)。

日志输出与断点调试。

典型问题:电源噪声、温度漂移导致的时序波动。

9297

9297

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?