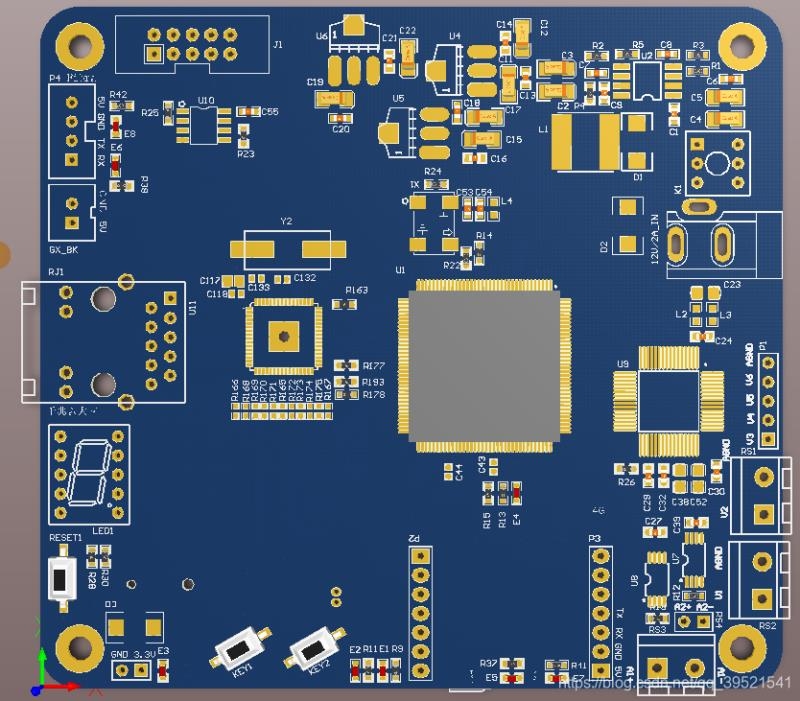

AD源文件及Verilog程序源码,包含AD的PCB源码和quartus程序源码,板子为四层板,程序为verilog,主控芯片为fpga。

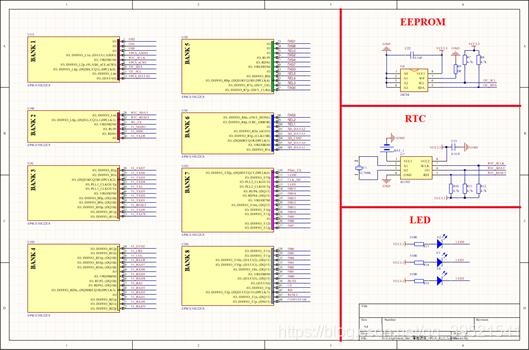

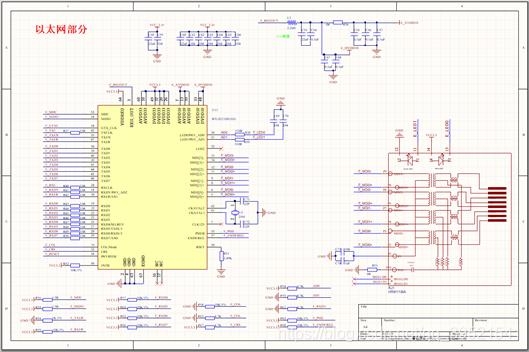

功能包括千兆以太网通讯(RTL8211EG芯片),micro sd卡存储,ad7606数据采集,串口通讯,电流和电压采集,实时时钟等。

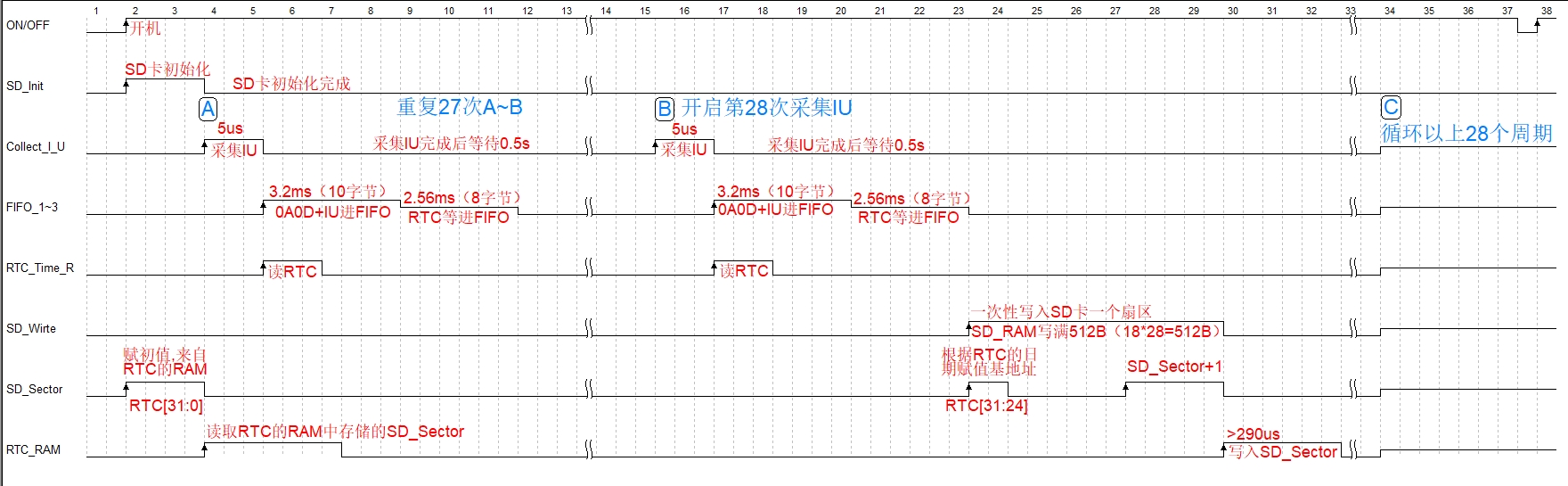

程序硬件在硬件上实际验证可行,fpga获取ad采集的数据和rtc实时时钟数据,并行的进行数据存储、串口和千兆以太网通讯。

最后在电脑上查看三者的数据是否相同。

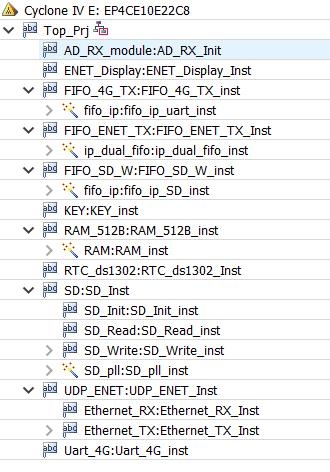

附上主要功能框图,部分原理图,实物图,源码结构图,主要时序图等图片。

源码4000+行,AD硬件源文件4层板,考虑了千兆网的阻抗和叠层。

进行了时序约束,无时序错误。

YID:28139641547733273

Advent!

AD源文件及Verilog程序源码的发布和共享在程序员社区中是非常常见的。这些源文件和程序通常包含了硬件原理图、源代码,以及其他必要的设计资料。在这篇文章中,我们将详细介绍一个功能强大的AD源文件及Verilog程序源码,并对其中的关键部分进行分析。

首先,我们来了解一下这个AD源文件及Verilog程序的功能和特点。这个程序是基于FPGA芯片的,包括了许多功能模块,如千兆以太网通信模块、Micro SD卡存储模块、AD7606数据采集模块、串口通信模块、电流和电压采集模块,以及实时时钟模块。它的硬件部分经过了实际验证,并且在设计中考虑了千兆网的阻抗和叠层问题,以确保数据传输的质量和稳定性。

在程序的实现上,FPGA芯片获取AD数据采集和实时时钟数据,并行进行数据存储、串口通信和千兆以太网通信。最后,我们可以在电脑上查看这三者的数据是否相同,以验证程序的正确性和可靠性。

接下来,我们将详细介绍这个AD源文件及Verilog程序的各个模块。首先是千兆以太网通信模块,它使用了RTL8211EG芯片,这个芯片提供了高速的以太网通信功能。我们将详细分析这个模块的原理和实现方法,并介绍其在整个系统中的作用。

接下来是Micro SD卡存储模块,它提供了数据的存储功能。我们将介绍SD卡的工作原理和接口协议,以及如何在Verilog程序中实现这个模块。

然后是AD7606数据采集模块,它是一个多通道的高精度数据采集模块。我们将详细介绍AD7606的工作原理和接口协议,并展示如何在Verilog程序中实现数据的采集和存储。

接下来是串口通信模块,它提供了和外部设备的串口通信功能。我们将介绍串口通信的原理和常用的协议,以及在Verilog程序中如何实现串口通信。

最后是电流和电压采集模块,它可以实时采集电流和电压数据。我们将详细介绍如何在Verilog程序中实现这个模块,并介绍一些常用的电流和电压采集方法。

除了功能模块的介绍,我们还会提供这个AD源文件及Verilog程序的一些设计资料,如主要功能框图、部分原理图、实物图、源码结构图和主要时序图等。这些设计资料能够更好地帮助读者理解和分析这个程序的实现细节。

总结来说,本文详细介绍了一个功能强大的AD源文件及Verilog程序,并对其中的各个功能模块进行了分析和解释。通过这篇文章,读者可以了解到该程序的设计思路和实现方法,进一步提高自己在FPGA芯片设计和Verilog程序编写方面的技术水平。

以上相关代码,程序地址:http://matup.cn/641547733273.html

762

762

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?