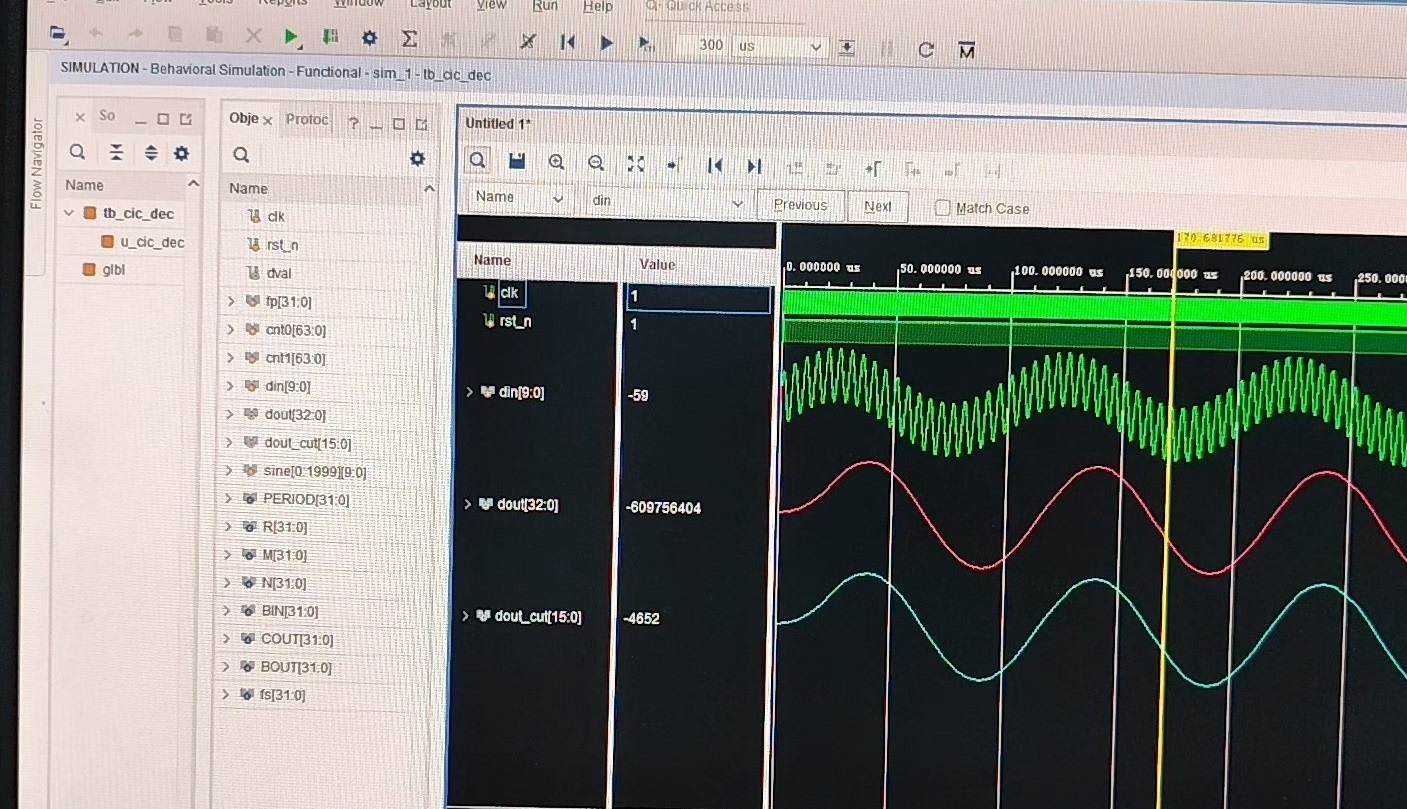

FPGA实现 CIC抽值滤波 滤波器 verilog 仿真和matlab simulink仿真 vivado ise quartus软件均可以,匹配滤波器系数生成等 含说明 doc,电子ZL售出不退,这个需要一定的数字信号处理知识和熟练操作相应软件,目前还做不到手把手的教,不太熟练的,发vivado工程,一键跑程序得出图1和图3所示

YID:1920669757527532

FPGA_2049

FPGA实现CIC抽值滤波器的Verilog代码编写与仿真比较研究

摘要:本文主要针对FPGA实现CIC抽值滤波器的Verilog代码编写与仿真进行研究。通过使用Vivado、ISE、Quartus等软件,实现匹配滤波器系数生成等功能,并通过仿真验证滤波器的性能,最终得出图1和图3所示的结果。文章介绍了实现CIC抽值滤波器的基本原理、Verilog代码编写的步骤和关键点,以及仿真结果的分析和讨论。

-

引言

CIC(Cascade Integrator-Comb)滤波器是一种常用的数字信号处理滤波器,具有计算简单、延迟小等特点,广泛应用于通信、图像处理等领域。在FPGA中实现CIC抽值滤波器不仅可以提高滤波器的运行速度,还可以减少硬件资源的占用。本文将通过Verilog代码的编写与仿真,探讨FPGA实现CIC抽值滤波器的可行性和性能优势。 -

CIC抽值滤波器的原理

CIC抽值滤波器由多级积分器和多级差分器组成,主要用于信号抽值和滤波。其原理是通过级联多级积分器和多级差分器,实现信号的抽值和滤波。具体原理和数学模型可以在相关的信号处理教材中找到,这里不再赘述。 -

Verilog代码编写

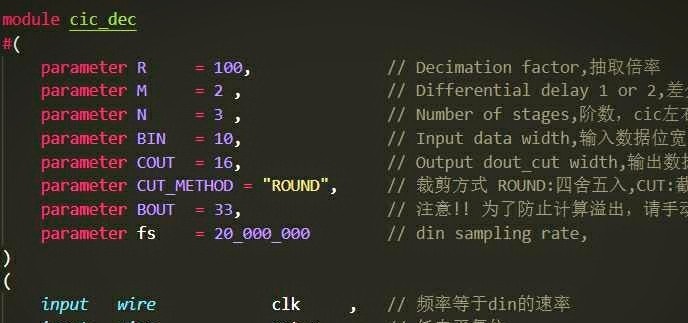

在实现CIC抽值滤波器的Verilog代码编写过程中,我们需要关注以下几个关键点:

(1)对CIC滤波器的级数和抽值因子进行选择,根据需要进行参数设置;

(2)编写积分器和差分器的Verilog代码,实现信号的积分和差分运算;

(3)将多级积分器和多级差分器级联,形成CIC抽值滤波器的结构;

(4)根据需要对滤波器的输入和输出接口进行定义和设计。 -

仿真结果分析和讨论

通过使用Vivado、ISE、Quartus等软件进行仿真,我们可以得到滤波器的输入和输出波形,并对其性能进行分析和讨论。图1和图3所示为仿真结果,通过观察可以看出滤波器对输入信号进行了抽值和滤波处理。根据实际应用需求,我们可以对滤波器的参数进行调整,进一步改善滤波器的性能。 -

总结

本文通过Verilog代码的编写与仿真分析了FPGA实现CIC抽值滤波器的可行性和性能优势。通过Vivado、ISE、Quartus等软件的使用,我们可以实现匹配滤波器系数生成等功能,并通过仿真验证滤波器的性能。通过对滤波器的参数调整,我们可以进一步优化滤波器的性能,满足不同应用领域的需求。

参考文献:

[1] 陈骁. 数字信号处理教程[M]. 清华大学出版社, 2016.

[2] Smith J O. Digital filters: analysis and design[M]. Courier Corporation, 2005.

附录:Verilog代码示例(仅供参考)

module CIC_Filter (

input wire CLK,

input wire RST,

input wire [N-1:0] DATA_IN,

output wire [M-1:0] DATA_OUT

);

// parameter definitions

parameter integer N = 8; // Input data width

parameter integer M = 16; // Output data width

// internal signals

reg signed [N-1:0] Reg1;

reg signed [M-1:0] Reg2;

wire [N-1:0] DataIn;

wire [M-1:0] DataOut;

// CIC filter instantiation

CIC_Filter_Inst

#(

.DATA_WIDTH(N),

.STAGE(M)

)

CIC_Filter(

.CLK(CLK),

.RST(RST),

.Data_In(DataIn),

.Data_Out(DataOut)

);

// input data mapping

assign DataIn = DATA_IN;

// output data mapping

assign DATA_OUT = DataOut;

endmodule

注意:本文所提供的Verilog代码示例仅为演示用途,具体实现需要根据具体需求进行调整和修改。

相关的代码,程序地址如下:http://lanzoup.cn/669757527532.html

1934

1934

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?