课题:ALU设计与验证

一、实验目的

1.熟悉 74LS181 ALU 的功能和使用方法。

2.了解运算部件的基本结构和数据传输过程,并掌握其设计和调试方法。

二、实验设备

1.装有ISE Design Suite 14.7的计算机一台

2.EDK-3 SA ISE实验平台

三、实验任务

1.对ALU模块进行仿真,验证功能的正确性

2.分析ALU功能,实现功能测试

四、实验原理

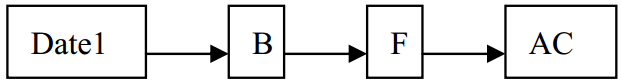

在图中,ALU 的数据输入,输出及对数据的处理都采用并行方式,ALU 的 B 输入端数据来自开关输入寄存器 B、A 输入端数据来自累加器 AC 的输出,ALU 的运算结果 F 存放在 AC 中,状态寄存器放两种特征:C 和 Z。

具体要求:

(1)数据为 4 位无符号二进制整数;

(2)完成 5 种运算功能:

1、 F=B

2、F=A+ B

3、F=AB

4、 F=A 加 B

5、 F=A 减 B

AC 的初始状态可以通过对它直接清零或者执行 F=B 操作给予置数; ALU 的控制端由开关设置;显示运算结果 AC 和状态 C、Z。

结构构思

时序

时序

T1: AC←0,Rz←0,Rc←0

T2: D1→B→F→AC

T3: D2→B→F→AC , AC→F→AC, C→Rc,Z→Rz

T4即:

T1(P0): CLRac CLRc/z =H PRc=L

T2 : ~Gb CKac F

T3 : ~Gb CKac F CKrc CKrz

T4 :

综合: CLR=PRc=PRz= P0 ~Gb=~(T2+T3) =(~T2)*(~T2)

CKac=T2M1+T3M1 CKrc=T3M1 CKrz=T3M1

74ls181 模块

MSI(中规模集成电路) 74LS181 ALU 可以对输人的两个 4 位数据 A 和B 执行 32 种算术及逻辑运算功能,其中算术、逻辑运算各 16 种,该器件有A0~A3, B0~B3 两个 4 位数据输入端, F0~F3 为结果输出端,高位进位输出端CN+4,组成进位辅助函数 P 和 G 输出端。 S3、 S2、 S1、 S0、 Cn、 M 为控制端,其中 M 为模式控制,当 M=1 时, ALU 执行对 A, B 的逻辑运算;

功能表

Ls74 模块

这是一个正沿触发双 D 型触发器

///ACTIVE HIGHT DATA

always@(posedge clk_s)

begin

case(S_in)

4'b0000 : begin

if (M_in==1) F_out_tmp<=~A_in;else begin if (Cn==1) F_out_tmp<=A_in;else F_out_tmp<=A_in+1; end

end

4'b0001 : begin

if (M_in==1) F_out_tmp<=~(A_in|B_in);else begin if (Cn==1) F_out_tmp<=A_in|B_in;else F_out_tmp<=(A_in|B_in)+1;end

end

4'b0010 : begin

if (M_in==1) F_out_tmp<=(~A_in)&B_in;else begin if (Cn==1) F_out_tmp<=A_in|(~B_in);else F_out_tmp<=A_in|(~B_in)+1;end

end

4'b0011 : begin

if (M_in==1) F_out_tmp<=0;else begin if (Cn==1) F_out_tmp<=-1;else F_out_tmp<=0;end

end

always@(F_out_tmp)

begin

if (F_out_tmp[3:0]==4'b0000)

Zero<=1'b1;

else

Zero<=1'b0;

end

endmodule

Ls74代码:

module ls74(clk_s,pre,clock,clear,din,dout

);

input clk_s;

input pre;

input clock;

input clear;

input din;

output dout;

reg dout;

always@(posedge clk_s )

begin

if (pre==1) begin

if (clear==1) begin

if (clock==1)

dout<=din;

else

dout<=1'b0;

end

end

end

endmodule

六、实验结果

-

仿真结果

-

操作现象

根据sin、carry、kin的不同输入,可以使用不用的运算规则;Din用于输入运算的数据,可以进行算术运算与逻辑运算。

3.实验结果分析

在图中,ALU 的数据输入,输出及对数据的处理都采用并行方式,ALU 的 B 输入端数据来自开关输入寄存器 B、A 输入端数据来自累加器 AC 的输出,ALU 的运算结果 F 存放在 AC 中,状态寄存器放两种特征:C 和 Z。

本实验重要的两个模块:

1.74ls181 模块 (实现逻辑运算与算数运算)

MSI(中规模集成电路) 74LS181 ALU 可以对输人的两个 4 位数据 A 和B 执行 32 种算术及逻辑运算功能,其中算术、逻辑运算各 16 种,该器件有A0~A3, B0~B3 两个 4 位数据输入端, F0~F3 为结果输出端,高位进位输出端CN+4,组成进位辅助函数 P 和 G 输出端。 S3、 S2、 S1、 S0、 Cn、 M 为控制端,其中 M 为模式控制,当 M=1 时, ALU 执行对 A, B 的逻辑运算:

2.Ls74 模块:一个正沿触发双 D 型触发器

3.数据传递:

Sw3数值为0时:Din拨成0011,sin拨成1010,kin拨成1,carry拨成1或0均可(逻辑运算仅与kin高低电位有关);

Sw3数值为1时:数据传入Din、sin、kin、carry;

Sw3数值为2时:数据传入bin、acin、F(上一次运算结果存在F中);

Sw3数值为3时:运算结果显示在acin。

七、问题思考

1.该简化版ALU与全功能ALU还有那些区别?

简化版ALU只适用于数值小于16的逻辑运算与算术运算。

全功能ALU可以对处理器控制器、内存及输入输出设备的直接读入读出。

2.节拍在ALU运行过程中起到什么作用?

一个节拍对应一个数据传递状态,即指令,节拍状态的表明了一条指令执行的步骤的次序关系。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?