步进电机控制器设计

利用Quartus ii9.0设计一个具有四相单四拍,四相双四拍和四相八拍的脉冲分配器。

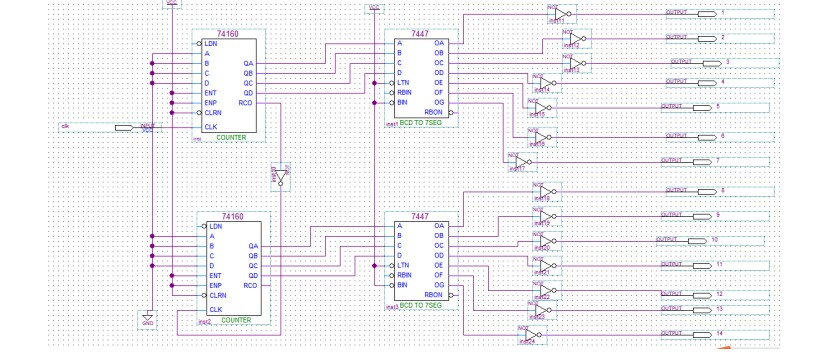

设计一个三选一数据选择器来控制pause信号选择工作方式,以及用两个74160与两个7447设计成计数器来对步进电机进行计数。

并用该软件对其进行了仿真。

报告设计说明书原理图程序

ID:68120649164702970

柠檬味的橘子

步进电机控制器设计

摘要:

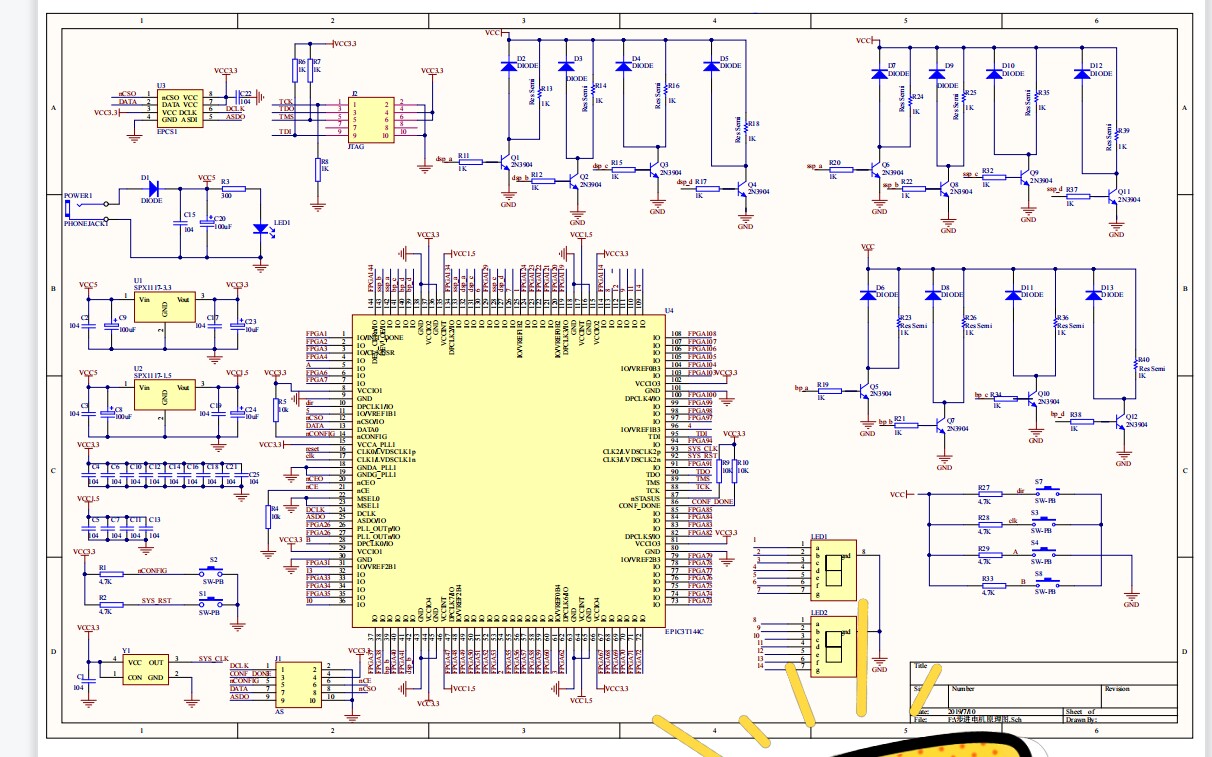

本文围绕步进电机控制器的设计展开讨论。首先介绍了使用Quartus ii9.0设计步进电机控制器的基本原理和方法。其次,讨论了具有四相单四拍、四相双四拍和四相八拍脉冲分配器的设计。然后,介绍了使用三选一数据选择器来控制pause信号选择工作方式的方法,并使用两个74160与两个7447设计成计数器来对步进电机进行计数。最后,通过该软件对步进电机控制器进行了仿真,并提供了设计说明书原理图程序。

关键词:步进电机控制器;Quartus ii9.0;四相单四拍;四相双四拍;四相八拍;脉冲分配器;三选一数据选择器;74160;7447;仿真

-

引言

步进电机是一种常用的控制设备,广泛应用于各种场景中。为了实现对步进电机的精确控制,需要设计一个有效的步进电机控制器。本文将介绍使用Quartus ii9.0进行步进电机控制器设计的方法,并结合具体示例进行详细讨论。 -

Quartus ii9.0设计步进电机控制器的原理和方法

Quartus ii9.0是一种常用的FPGA设计工具,可以用于设计和实现各种数字逻辑电路。在步进电机控制器的设计中,可以利用Quartus ii9.0来实现脉冲分配器、数据选择器和计数器等功能模块的设计。通过这些功能模块的组合,可以实现对步进电机的精确控制。 -

四相单四拍、四相双四拍和四相八拍脉冲分配器的设计

在步进电机控制中,脉冲分配器负责将输入的脉冲信号按照一定的规律进行分配,从而驱动步进电机转动。本文介绍了三种常见的脉冲分配器设计:四相单四拍、四相双四拍和四相八拍。通过设计不同的脉冲分配器,可以实现不同运动模式下步进电机的控制。 -

三选一数据选择器的设计

为了实现对步进电机的工作方式的选择,可以设计一个三选一数据选择器来控制pause信号的选择。通过该数据选择器,可以动态地切换步进电机的工作模式,使其适应不同的应用场景。 -

用两个74160与两个7447设计成计数器来对步进电机进行计数

在步进电机控制中,计数器是一种常见的辅助模块,用于记录步进电机转动的步数。本文介绍了使用两个74160与两个7447设计成计数器的方法。通过这种计数器的设计,可以实时监控步进电机的运动状态。 -

步进电机控制器的仿真

为了验证步进电机控制器的设计效果,本文使用Quartus ii9.0对步进电机控制器进行了仿真。通过仿真结果的分析,可以评估设计的正确性和性能。 -

设计说明书原理图程序

最后,本文提供了步进电机控制器的设计说明书原理图程序,方便读者参考和使用。

总结:

本文围绕步进电机控制器的设计展开了论述,介绍了使用Quartus ii9.0进行步进电机控制器设计的原理和方法,并通过具体示例详细阐述了四相单四拍、四相双四拍和四相八拍脉冲分配器的设计、三选一数据选择器的设计和使用两个74160与两个7447设计成计数器的方法。最后,进行了步进电机控制器的仿真,并提供了设计说明书原理图程序。本文旨在为读者提供一个实际可行的步进电机控制器设计方案,并为相关领域的研究和应用提供参考。

以上相关代码,程序地址:http://matup.cn/649164702970.html

1672

1672

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?