存储器制作(含非对齐读写)

1. 创建ROM 和 RAM IP核

参考马德老师lab0PPT

1.新建一个项目ROM,选择芯片,创建。

2.搜索memory generator.

3.双击

4.设置好后点击OK

width写32 另一个写1024

5.编写ROM.coe

memory_initialization_radix=16;

memory_initialization_vector=

0000000, 11111111, 22222222, 33333333, 44444444, 55555555, 66666666, 77777777, 88888888, 99999999, aaaaaaaa, bbbbbbbb, cccccccc, dddddddd, eeeeeeee, ffffffff, 557EF7E0, D7BDFBD9, D7DBFDB9, DFCFFCFB, DFCFBFFF, F7F3DFFFF, FFFFDF3D, FFFF9DB9, FFFFBCFB, DFCFFCFB, DFCFBFFF, D7DB9FFF, D7DBFDB9, D7BDFBD9, FFFF07E0, 007E0FFF, 03bdf020, 03def820, 08002300;

用记事本编写然后保存设置后缀(全部文件)。

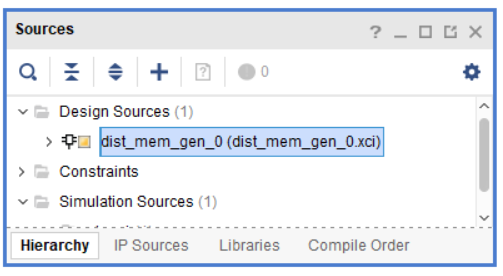

6.双击xci

7.点击RST & initialization,导入ROM.coe

8.点击IP Sources,查看调用模式

RAM基本相同,在memory generator处选择上一个有时钟输入的即可。

2. TOP文件编写

要求是在指定的地址写入32’h12345678

assign wired=32'h12345678;

always @(posedge clk)begin

//读数的低16

//给寄存器赋值

if(flag==3'b000)begin

adr<=add[0]?add+2'b10:add;

flag<=3'b001;

end

//第一次赋值成功后 赋值第二次

else if(flag==3'b001)begin

adr<=add;

flag<=3'b010;

end

//RAM读出第一次adr的值 给低16位输出

else if(flag==3'b010)begin

//result[31:16]<=add[0]?result1[15:0]:result1[31:16];

store_result[63:32]<=result1;

result[15:0]<=add[0]?result1[31:16]:result1[15:0];

flag<=3'b011;

end

else if(flag==3'b011)begin

store_result[31:0]<=result1;

result[31:16]<=add[0]?result1[15:0]:result1[31:16];

flag<={LES,2'b00};

end

else if(flag==3'b100)begin

//wr<=add[0]?{store_result[31:16],wired[15:0]}:wired;

wr<=add[0]?{result1[31:16],wired[31:16]}:wired;

myLES<=1;

flag<=3'b101;

end

else if(flag<=3'b101)begin

wr<=add[0]?{wired[15:0],store_result[47:32]}:wired;

myLES<=add[0]?1'b1:1'b0;

adr<=add+2'b10;

flag<=3'b110;

end

else if(flag<=3'b110)begin

myLES<=1'b0;

flag<=3'b000;

end

end

简单实现一个状态机。

- 寄存器每次要在下一个时钟周期才能更新值。

- RAM在寄存器更新之后需要一个时钟周期才能读出地址的值(write first RAM)

- 通过myLES信号实现只给特定时钟周期的写使能。

进行引脚约束下板即可。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?