IP核配置

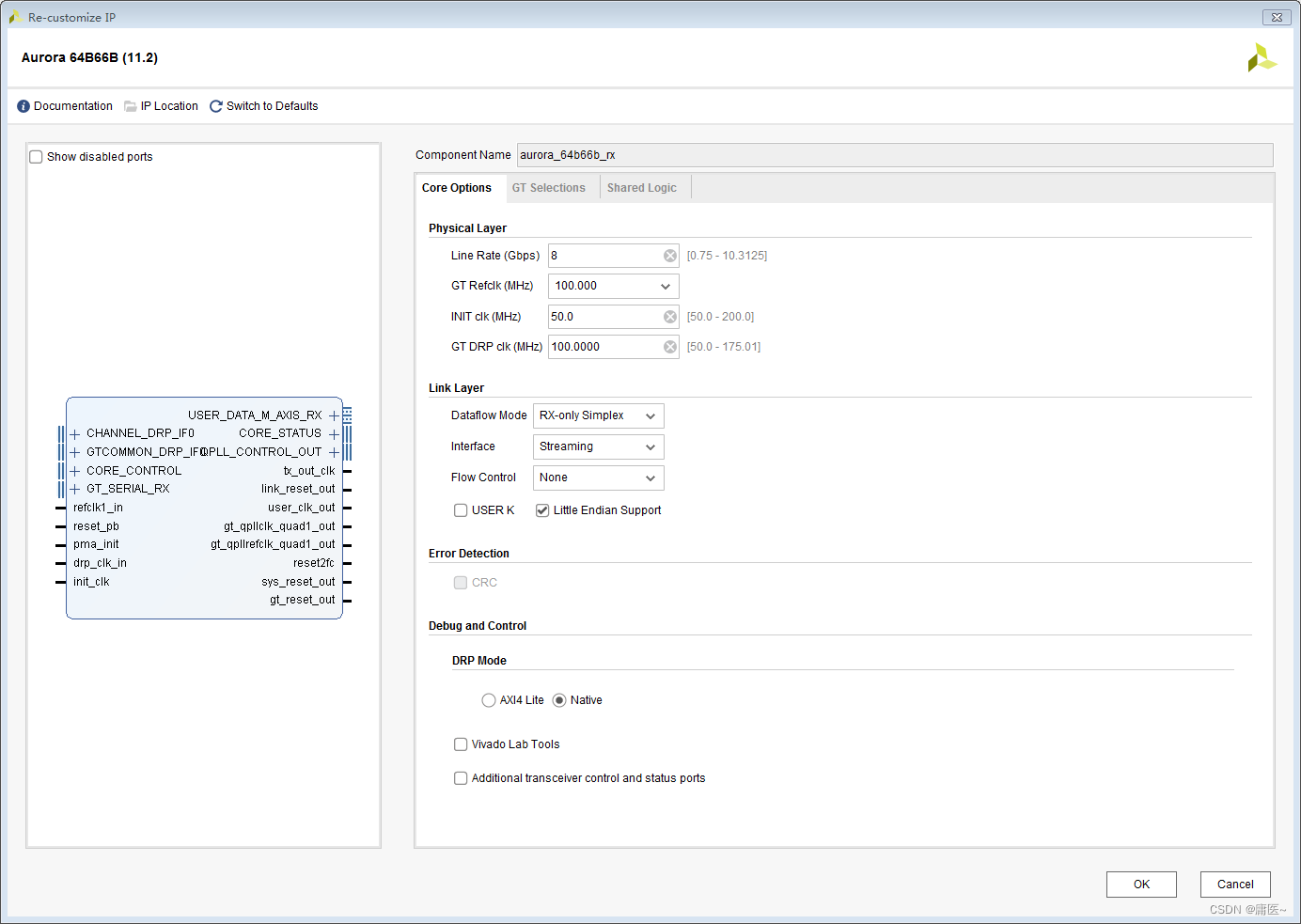

Aurora 64B/66B IP核的配置也比较简单,只需要对线速率和时钟进行配置,INIT clk和DRP clk是IP核内部逻辑使用,与线速率和uesr_clk无关,这两个时钟可以选择用户提供方便的时钟频率,

Link Layer进行接口的配置,datafolw模式可以选择全双工传输,半双工传输,以及单工传输。接口类型可以选择帧式接口和流式接口,可以选择是否使用流量控制功能,数据默认大端类型。也就是[0:63]的格式,可以勾选litter endian support改成常见的小端格式[63:0]。

对于Debug and control,这里的几乎用不到,不用管,为了减少IP核的接口,模式可以选用native模式,

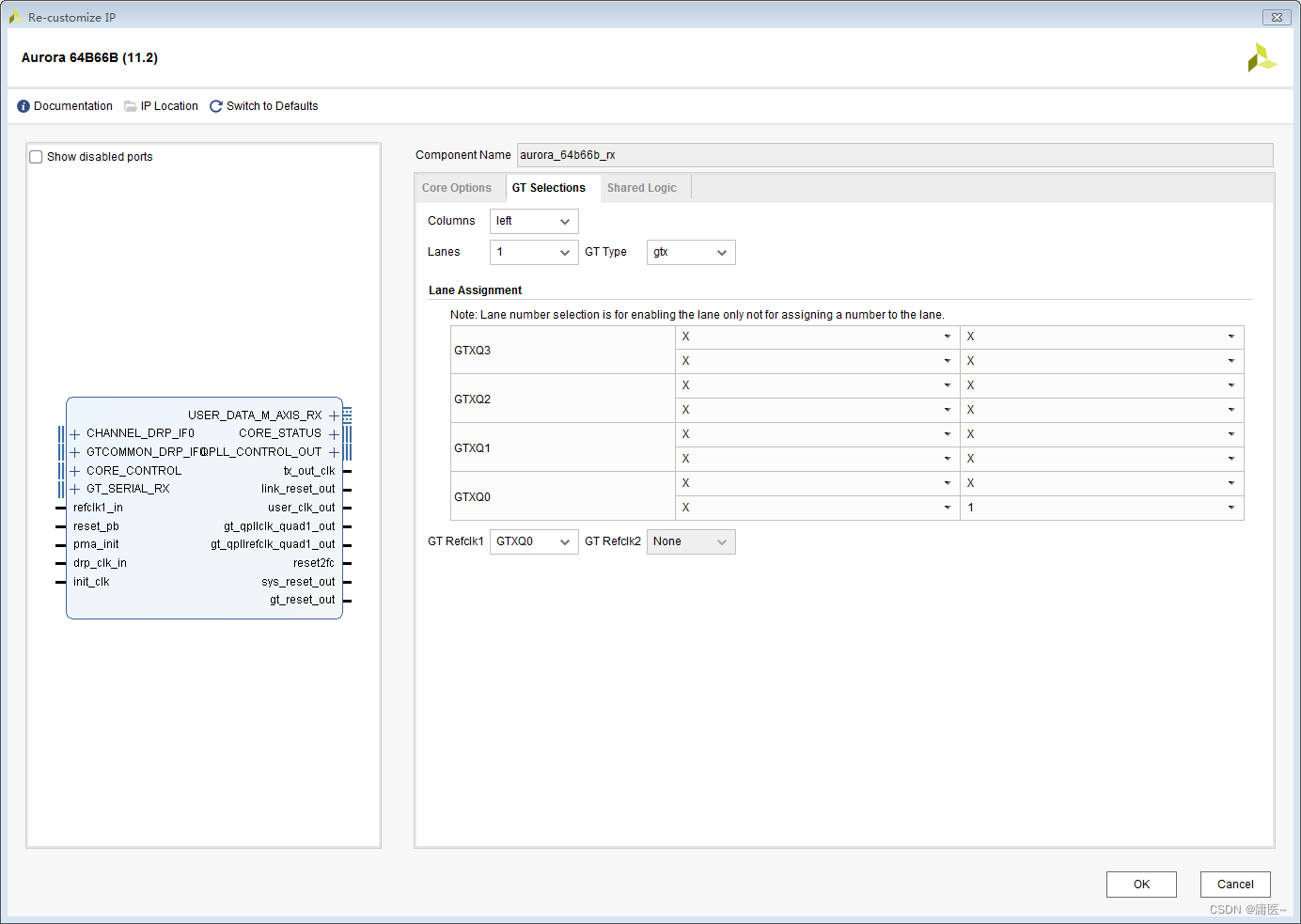

GT_selections 这里可以不用管,这里规定了用的哪一组收发器,只要在引脚约束的时候把管脚约束对就行。对于GT refclk,对于单链路传输,这里的选项只能选同一quad的时钟,但实际上可以选用临近quad的时钟,也就是临近bank上的时钟,只需要在进行引脚约束的时候把约束对就行。

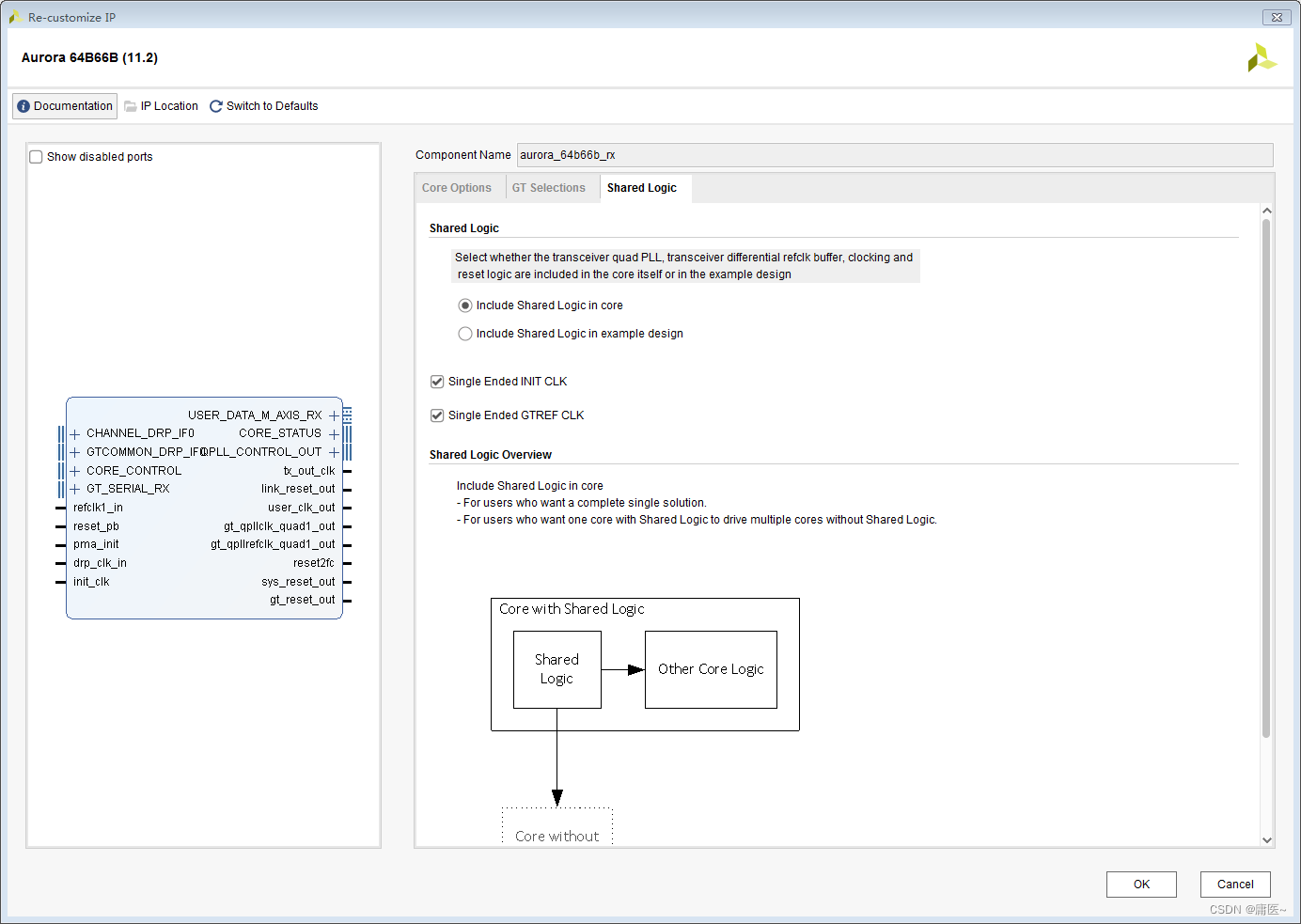

对于shared logic 这里选择的共享逻辑在核心中还是共享逻辑在示例程序中,当选择共享逻辑在核心中时,可以选择init clk和ref clk是单端时钟输入还是差分时钟输入。选择共享逻辑在核中,就不需要例化GTXE2_COMMON,GTXE2_COMMON在IP内部进行例化使用。选择共享逻辑在示例中这种通常是为了同时使用两组quad,一个IP核选用共享逻辑在核中,一个选择共享逻辑在示例中,选用IP在core的输出时钟提供给共享逻辑在示例程序中。

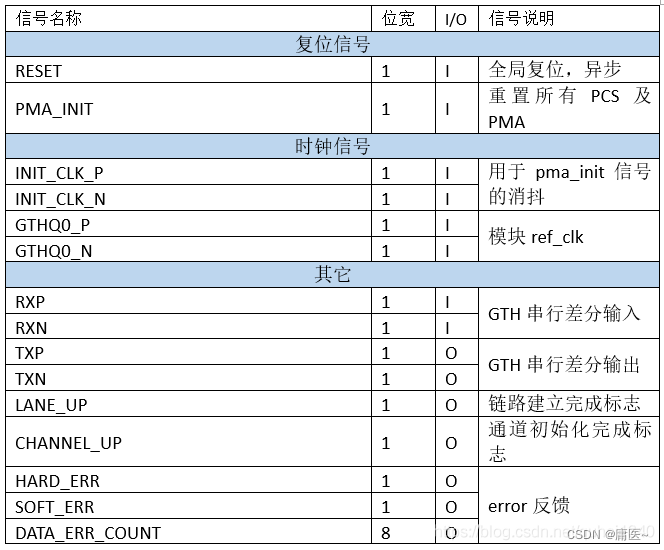

接口

用户接口

| Name |

Direction |

Clock Domain |

Description |

| s_axi_tx_tdata |

Input |

user_clk |

传出数据(大小端由用户设定) |

| s_axi_tx_tready |

Output |

user_clk |

当接受来自源的信号时断言。当忽略来自源的信号时取消断言。 |

| s_axi_tx_tvalid |

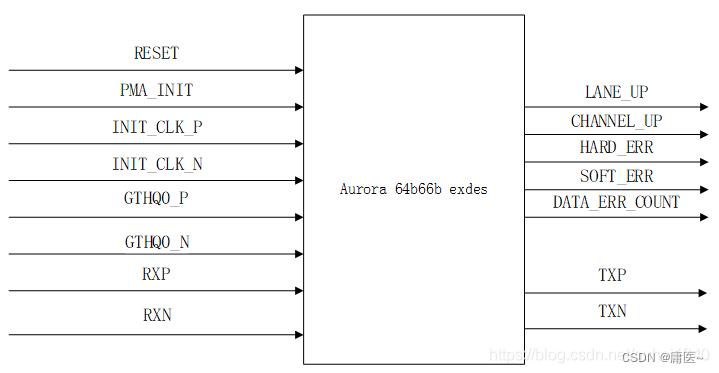

Aurora64B/66BIP核配置涉及线速率、时钟配置,如INITclk和DRPclk,以及LinkLayer的数据流模式选择。接口包括全双工、半双工和单工传输,可以选择帧式或流式接口,支持流量控制。时钟接口有init_clk、user_clk等,GT_refclk需与收发器匹配。IP核还提供了调试和控制接口,以及GT_selections和shared_logic的配置选项。

Aurora64B/66BIP核配置涉及线速率、时钟配置,如INITclk和DRPclk,以及LinkLayer的数据流模式选择。接口包括全双工、半双工和单工传输,可以选择帧式或流式接口,支持流量控制。时钟接口有init_clk、user_clk等,GT_refclk需与收发器匹配。IP核还提供了调试和控制接口,以及GT_selections和shared_logic的配置选项。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

310

310

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?