38译码器 verilog FPGA 基础练习0

发现问题,用技术解决问题。兴趣是自己的源动力 !

目录

- 38译码器 verilog FPGA 基础练习0

- 前言

- 一、端口的扩展

- 二、解决方案

- 三、实现方案

- 3.1 if else版本

- 3.2 case 版本

- 3.3.仿真代码

- 3.4 小知识点

- 3.4 仿真结果

- 总结

前言

译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

一、端口的扩展

假如我们有8个led灯需要单独控制,理论上我们需要用8个I/O口,普通的单片机也够用,但是如果我们控制的不是8个led灯,而是一个点阵屏,那就可想而知我们要使用的I/O口数量不是一般控制器就能满足的了,即便是I/O资源丰 富的FPGA在面对巨大的点阵屏时也可能面临管脚资源不够用的尴尬境地。

二、解决方案

此种情况下使用3-8译码器就可以很好的解决这个问题,我们可以通过控制器控制3个I/O输出的8种情况来分别控制8个输出状态,相当于用3个I/O口就可以独立控制8个led灯,即一个3-8译码器就能够节约出来5个I/O口,算起来是相当合算 的

三、实现方案

3.1 if else版本

if-else版本译码器代码如下:

module decoder3_8(

input wire in1,

input wire in2,

input wire in3,

output reg [7:0] out // 8bit,每一个bit表示一个LED灯

);

always@(*)

if({in3,in2,in1} == 3'b000)

out = 8'b0000_0001; // 表示亮第一盏灯

else if({in3,in2,in1} == 3'b001)

out = 8'b0000_0010; // 表示亮第二个灯,后续递推...

else if({in3,in2,in1} == 3'b010)

out = 8'b0000_0100;

else if({in3,in2,in1} == 3'b011)

out = 8'b0000_1000;

else if({in3,in2,in1} == 3'b100)

out = 8'b0001_0000;

else if({in3,in2,in1} == 3'b101)

out = 8'b0010_0000;

else if({in3,in2,in1} == 3'b110)

out = 8'b0100_0000;

else if({in3,in2,in1} == 3'b111)

out = 8'b1000_0000;

else

out = 8'b0000_0000; // 最后一个else避免latch的产生

endmodule

3.2 case 版本

case版本代码如下:

module decoder3_8(

input wire in1,

input wire in2,

input wire in3,

output reg [7:0] out

);

always@(*)

case({in3,in2,in1})

3'b000 : out = 8'b0000_0001;

3'b001 : out = 8'b0000_0010;

3'b010 : out = 8'b0000_0100;

3'b011 : out = 8'b0000_1000;

3'b100 : out = 8'b0001_0000;

3'b101 : out = 8'b0010_0000;

3'b110 : out = 8'b0100_0000;

3'b111 : out = 8'b1000_0000;

endcase

endmodule

3.3.仿真代码

`timescale 1ns/1ns

module tb_top();

// 模块的接口参数定义

reg in1;

reg in2;

reg in3;

wire [7:0] out;

initial

begin

in1 <= 1'b0;

in2 <= 1'b0;

in3 <= 1'b0;

end

always #10 in1 <= {$random} % 2;

always #10 in2 <= {$random} % 2;

always #10 in3 <= {$random} % 2;

// 实现译码的功能,使得可以通过3bit能控制8个LED灯

decoder3_8 u0_decoder3_8

(

.in1 (in1),

.in2 (in2),

.in3 (in3),

.out (out)

);

endmodule

3.4 小知识点

if-else的这种写法是存在优先级的,即第一个if中的条件的优先级最高,后面的if中的条件的优先级依次递减,好在该if中的条件只有一个,也只会产生一种情况,并不会产生优先级的冲突,所以这里优先级的高低关系并不会对最后的功能产生任何影响。而case在 任何时候都不存在优先级的问题,而是通过判断case中的条件来选择对应的输出。

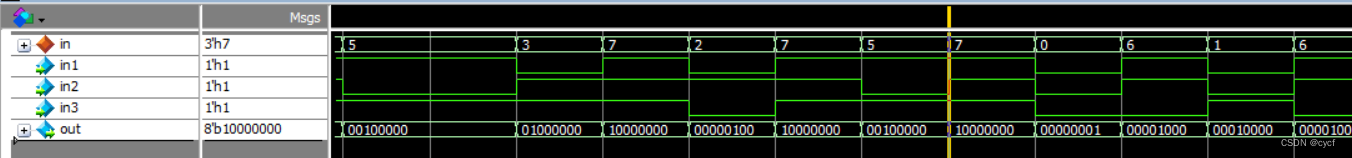

3.4 仿真结果

总结

核心思想:如果能够明白在不同场景下,能够用尽可能少的bit位来控制多bit位的数据,那么就完成思想上的升华。其处理手段和流程:输入数据、预处理(通过拼接符“{}”)、数据映射(通过条件选择语句进行3-8译码映射)、输出。

文章介绍了如何使用Verilog在FPGA中实现3-8译码器,以解决控制大量LED灯时I/O资源不足的问题,通过if-else和case结构实现,并讨论了两种方法的优劣及优先级问题。

文章介绍了如何使用Verilog在FPGA中实现3-8译码器,以解决控制大量LED灯时I/O资源不足的问题,通过if-else和case结构实现,并讨论了两种方法的优劣及优先级问题。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?