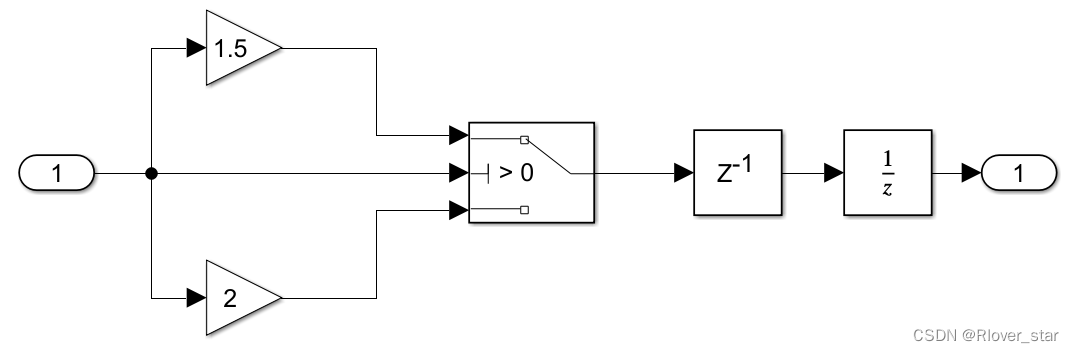

Simulink代码生成(六)——ert.tlc下默认配置生成代码的解读

一、代码生成的结构:

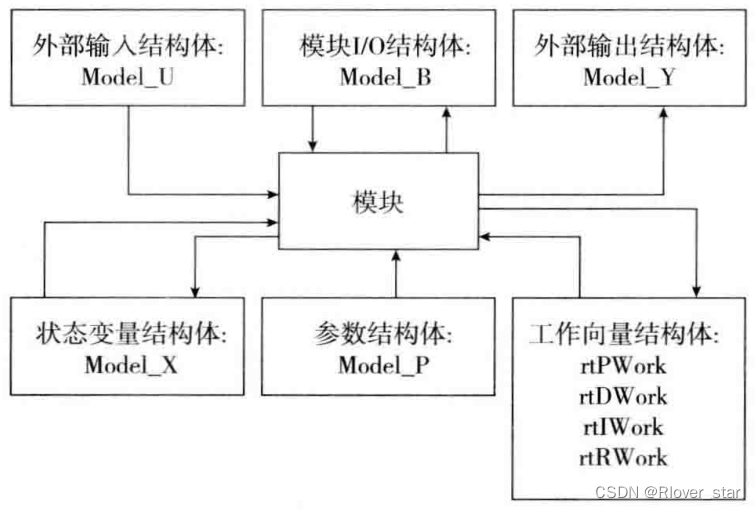

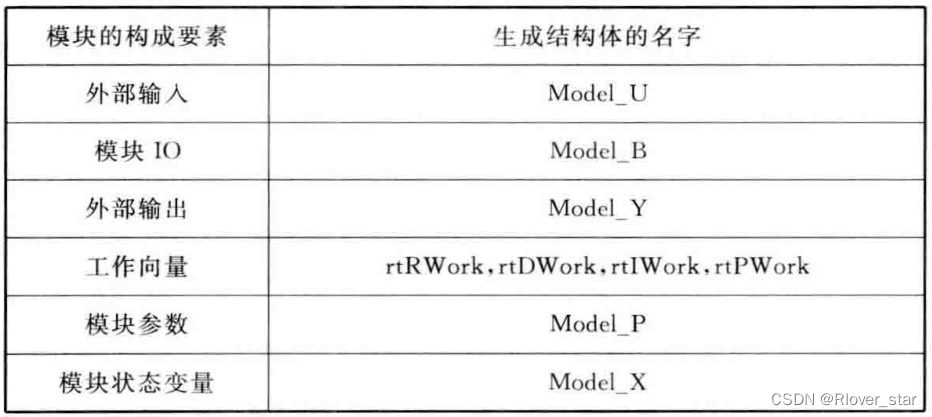

模块是构成Simulink模型的最小单元,因此可明确将一个模块分为7个部分,出去接地的rtGround之外,其余6个部分都明确了生成代码时所使用的变量生成格式,都对构成模块的各个对象的生成变量进行了结构体的约束,并且对结构体的变量名前缀进行了规定。

Model表示当前模型名,生成的代码遵循以下规则。

二、model.rtw文件解读

模块是构成Simulink模型的最小单元,因此可明确将一个模块分为7个部分,出去接地的rtGround之外,其余6个部分都明确了生成代码时所使用的变量生成格式,都对构成模块的各个对象的生成变量进行了结构体的约束,并且对结构体的变量名前缀进行了规定。

生成代码如下,rtwtypes.h是ert.tlc生成代码所要用到的数据类型的定义,不需要修改和考虑。

从untitled.h中可以看到,输入和输出的定义分别放到了不同的结构体中,两个delay模块放到了DW的结构体(也就是工作向量中),模块用到的数据都放到了P相关的结构体中。

注意两个delay参数,delayonestep模块还生成了一个变量DelayOneStep_DelayLength,其数据类型为uint32_T,通过untitled.c可以看到这个值为1,表示的是Z^-1的1.

/*

* File: untitled.h

*

* Code generated for Simulink model 'untitled'.

*

* Model version : 1.9

* Simulink Coder version : 9.0 (R2018b) 24-May-2018

* C/C++ source code generated on : Tue Oct 18 22:11:38 2022

*

* Target selection: ert.tlc

* Embedded hardware selection: Intel->x86-64 (Windows64)

* Code generation objectives: Unspecified

* Validation result: Not run

*/

#ifndef RTW_HEADER_untitled_h_

#define RTW_HEADER_untitled_h_

#include "rtwtypes.h"

#include <stddef.h>

#include <string.h>

#ifndef untitled_COMMON_INCLUDES_

# define untitled_COMMON_INCLUDES_

#include "rtwtypes.h"

#endif /* untitled_COMMON_INCLUDES_ */

/* Macros for accessing real-time model data structure */

#ifndef rtmGetErrorStatus

# define rtmGetErrorStatus(rtm) ((rtm)->errorStatus)

#endif

#ifndef rtmSetErrorStatus

# define rtmSetErrorStatus(rtm, val) ((rtm)->errorStatus = (val))

#endif

/* Forward declaration for rtModel */

typedef struct tag_RTM_untitled_T RT_MODEL_untitled_T;

/* Block states (default storage) for system '<Root>' */

typedef struct {

real_T UnitDelay_DSTATE; /* '<Root>/Unit Delay' */

real_T DelayOneStep_DSTATE; /* '<Root>/Delay One Step' */

} DW_untitled_T;

/* External inputs (root inport signals with default storage) */

typedef struct {

real_T In1; /* '<Root>/In1' */

} ExtU_untitled_T;

/* External outputs (root outports fed by signals with default storage) */

typedef struct {

real_T Out1; /* '<Root>/Out1' */

} ExtY_untitled_T;

/* Parameters (default storage) */

struct P_untitled_T_ {

real_T Gain1_Gain; /* Expression: 2

* Referenced by: '<Root>/Gain1'

*/

real_T Gain_Gain; /* Expression: 1.5

* Referenced by: '<Root>/Gain'

*/

real_T UnitDelay_InitialCondition; /* Expression: 0

* Referenced by: '<Root>/Unit Delay'

*/

real_T DelayOneStep_InitialCondition;/* Expression: 0.0

* Referenced by: '<Root>/Delay One Step'

*/

real_T Switch_Threshold; /* Expression: 0

* Referenced by: '<Root>/Switch'

*/

uint32_T DelayOneStep_DelayLength; /* Computed Parameter: DelayOneStep_DelayLength

* Referenced by: '<Root>/Delay One Step'

*/

};

/* Parameters (default storage) */

typedef struct P_untitled_T_ P_untitled_T;

/* Real-time Model Data Structure */

struct tag_RTM_untitled_T {

const char_T * volatile errorStatus;

};

/* Block parameters (default storage) */

extern P_untitled_T untitled_P;

/* Block states (default storage) */

extern DW_untitled_T untitled_DW;

/* External inputs (root inport signals with default storage) */

extern ExtU_untitled_T untitled_U;

/* External outputs (root outports fed by signals with default storage) */

extern ExtY_untitled_T untitled_Y;

/* Model entry point functions */

extern void untitled_initialize(void);

extern void untitled_step(void);

extern void untitled_terminate(void);

/* Real-time Model object */

extern RT_MODEL_untitled_T *const untitled_M;

/*-

* The generated code includes comments that allow you to trace directly

* back to the appropriate location in the model. The basic format

* is <system>/block_name, where system is the system number (uniquely

* assigned by Simulink) and block_name is the name of the block.

*

* Use the MATLAB hilite_system command to trace the generated code back

* to the model. For example,

*

* hilite_system('<S3>') - opens system 3

* hilite_system('<S3>/Kp') - opens and selects block Kp which resides in S3

*

* Here is the system hierarchy for this model

*

* '<Root>' : 'untitled'

*/

#endif /* RTW_HEADER_untitled_h_ */

/*

* File trailer for generated code.

*

* [EOF]

*/

untitled.c先对untitled.h中声明的结构体进行定义,以及进行初始化。参数的初始化是在结构体定义的时候直接赋值进行初始化的,而其他的结构体类型都是在untitled_initialize函数中进行初始化的。初始化函数只执行一次。

untitled_step函数是模型转化成的算法代码,一般会放到while中执行。

/*

* File: untitled.c

*

* Code generated for Simulink model 'untitled'.

*

* Model version : 1.9

* Simulink Coder version : 9.0 (R2018b) 24-May-2018

* C/C++ source code generated on : Tue Oct 18 22:11:38 2022

*

* Target selection: ert.tlc

* Embedded hardware selection: Intel->x86-64 (Windows64)

* Code generation objectives: Unspecified

* Validation result: Not run

*/

#include "untitled.h"

/* Block parameters (default storage) */

P_untitled_T untitled_P = {

/* Expression: 2

* Referenced by: '<Root>/Gain1'

*/

2.0,

/* Expression: 1.5

* Referenced by: '<Root>/Gain'

*/

1.5,

/* Expression: 0

* Referenced by: '<Root>/Unit Delay'

*/

0.0,

/* Expression: 0.0

* Referenced by: '<Root>/Delay One Step'

*/

0.0,

/* Expression: 0

* Referenced by: '<Root>/Switch'

*/

0.0,

/* Computed Parameter: DelayOneStep_DelayLength

* Referenced by: '<Root>/Delay One Step'

*/

1U

};

/* Block states (default storage) */

DW_untitled_T untitled_DW;

/* External inputs (root inport signals with default storage) */

ExtU_untitled_T untitled_U;

/* External outputs (root outports fed by signals with default storage) */

ExtY_untitled_T untitled_Y;

/* Real-time model */

RT_MODEL_untitled_T untitled_M_;

RT_MODEL_untitled_T *const untitled_M = &untitled_M_;

/* Model step function */

void untitled_step(void)

{

/* Outport: '<Root>/Out1' incorporates:

* UnitDelay: '<Root>/Unit Delay'

*/

untitled_Y.Out1 = untitled_DW.UnitDelay_DSTATE;

/* Delay: '<Root>/Delay One Step' incorporates:

* UnitDelay: '<Root>/Unit Delay'

*/

untitled_DW.UnitDelay_DSTATE = untitled_DW.DelayOneStep_DSTATE;

/* Switch: '<Root>/Switch' incorporates:

* Delay: '<Root>/Delay One Step'

* Gain: '<Root>/Gain'

* Gain: '<Root>/Gain1'

* Inport: '<Root>/In1'

*/

if (untitled_U.In1 > untitled_P.Switch_Threshold) {

untitled_DW.DelayOneStep_DSTATE = untitled_P.Gain_Gain * untitled_U.In1;

} else {

untitled_DW.DelayOneStep_DSTATE = untitled_P.Gain1_Gain * untitled_U.In1;

}

/* End of Switch: '<Root>/Switch' */

}

/* Model initialize function */

void untitled_initialize(void)

{

/* Registration code */

/* initialize error status */

rtmSetErrorStatus(untitled_M, (NULL));

/* states (dwork) */

(void) memset((void *)&untitled_DW, 0,

sizeof(DW_untitled_T));

/* external inputs */

untitled_U.In1 = 0.0;

/* external outputs */

untitled_Y.Out1 = 0.0;

/* InitializeConditions for UnitDelay: '<Root>/Unit Delay' */

untitled_DW.UnitDelay_DSTATE = untitled_P.UnitDelay_InitialCondition;

/* InitializeConditions for Delay: '<Root>/Delay One Step' */

untitled_DW.DelayOneStep_DSTATE = untitled_P.DelayOneStep_InitialCondition;

}

/* Model terminate function */

void untitled_terminate(void)

{

/* (no terminate code required) */

}

/*

* File trailer for generated code.

*

* [EOF]

*/

3799

3799

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?