一、主流ADC芯片架构及特性

-

SAR型(逐次逼近型)ADC

工作原理:

Tconv=N×TclkT_{\text{conv}} = N \times T_{\text{clk}}Tconv=N×Tclk(NNN为位数,TclkT_{\text{clk}}Tclk为时钟周期)

特点: -

中高精度(12-18位)

-

中等速度(100kSPS-10MSPS)

-

低功耗(Pd<10mWP_d < 10\text{mW}Pd<10mW)

代表型号:AD7980(18位/2MSPS),ADS8881(16位/1MSPS)

应用场景:工业控制、便携式仪器

- Σ-Δ型(Sigma-Delta)ADC

噪声整形原理:

Y(z)=X(z)+(1−z−1)kE(z)Y(z) = X(z) + (1 - z^{-1})^k E(z)Y(z)=X(z)+(1−z−1)kE(z)(kkk为调制器阶数)

特点:

-

超高精度(16-32位)

-

低速(<100kSPS)

-

强抗干扰能力

代表型号:AD7177(32位/125kSPS),ADS1262(32位/40kSPS)

应用场景:称重传感器、医疗仪器

- Pipeline型(流水线型)ADC

转换时序:

Latency=M×TstageLatency = M \times T_{\text{stage}}Latency=M×Tstage(MMM为流水线级数)

特点:

-

高速(100MSPS-5GSPS)

-

中等精度(10-14位)

-

固定延迟

代表型号:AD9208(14位/3GSPS),ADC12DJ5200(12位/5.2GSPS)

应用场景:5G通信、雷达系统

- Flash型(全并行)ADC

比较器数量:

Ncomp=2N−1N_{\text{comp}} = 2^N - 1Ncomp=2N−1

特点:

-

超高速(>1GSPS)

-

低精度(6-8位)

-

高功耗(Pd>1WP_d > 1\text{W}Pd>1W)

代表型号:ADC12D1000(12位/1GSPS)

应用场景:示波器、软件定义无线电

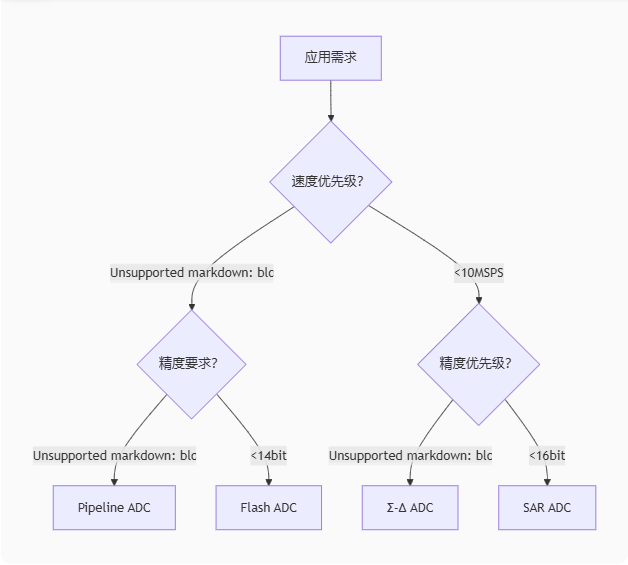

二、关键参数选型指南

-

精度指标

参数 公式 设计意 ENOB ENOB=SNDR−1.766.02\text{ENOB} = \frac{\text{SNDR}-1.76}{6.02}ENOB=6.02SNDR−1.76 实际有效位 -

动态性能

-

采样率选择:fs≥2.2×fmaxf_s \geq 2.2 \times f_{\text{max}}fs≥2.2×fmax(考虑抗混叠)

-

时钟抖动要求:σt<12N+1πfin\sigma_t < \frac{1}{2^{N+1} \pi f_{\text{in}}}σt<2N+1πfin1

-

SFDR约束:通信系统需SFDR>80dB\text{SFDR} > 80\text{dB}SFDR>80dB

- 接口与功耗

三、选型决策树 # 四、设计注意事项

# 四、设计注意事项

- 前端驱动设计

-

建立时间要求:

tsettle<12N+1fst_{\text{settle}} < \frac{1}{2^{N+1} f_s}tsettle<2N+1fs1 -

运放选型准则:

GBW>10×ffullscale\text{GBW} > 10 \times f_{\text{fullscale}}GBW>10×ffullscale

SR>2πfVpp\text{SR} > 2\pi f V_{\text{pp}}SR>2πfVpp

- 时钟系统设计

-

抖动控制公式:

SNRjitter=−20log10(2πfinσt)\text{SNR}{\text{jitter}} = -20\log{10}(2\pi f_{\text{in}} \sigma_t)SNRjitter=−20log10(2πfinσt) -

实现方案:

-

超低相噪OCXO(<−150dBc/Hz@1kHz< -150\text{dBc}/ \text{Hz}@1\text{kHz}<−150dBc/Hz@1kHz)

-

差分时钟走线(ΔL<5mil\Delta L < 5\text{mil}ΔL<5mil)

- 电源设计规范

| 噪声源 | 允许纹波 | 滤波方案 |

|---|---|---|

| AVDD | <100μVpp<100\mu\text{V}_{\text{pp}}<100μVpp | π型LC滤波 + LDO |

| DVDD | <5mVpp<5\text{mV}_{\text{pp}}<5mVpp | 磁珠 + 陶瓷电容阵列 |

| VREF | <50μVpp<50\mu\text{V}_{\text{pp}}<50μVpp | RC滤波 + 缓冲器 |

- PCB布局黄金法则

8层板叠层设计:

Layer1: 信号输入

Layer2: 完整地平面

Layer3: 模拟电源

Layer4: 时钟信号

Layer5: 隔离地

Layer6: 数字电源

Layer7: 数字输出

Layer8: 混合地

关键规则:

-

模拟/数字分割间距 >3mm> 3\text{mm}>3mm

-

去耦电容距引脚 <2mm< 2\text{mm}<2mm

-

参考走线阻抗 50Ω±550\Omega \pm 5%50Ω±5

五、典型应用方案

- 高精度测量系统

-

芯片选型:ADS1262(Σ-Δ型,32位)

-

前端设计:

Rin>10MΩR_{\text{in}} > 10\text{M}\OmegaRin>10MΩ

CMRR>120dB\text{CMRR} > 120\text{dB}CMRR>120dB -

滤波方案:8阶抗混叠滤波器

- 5G通信接收机

-

芯片选型:AD9208(Pipeline型,14位/3GSPS)

-

时钟方案:

fclk=3GHzf_{\text{clk}} = 3\text{GHz}fclk=3GHz

σt<30fs\sigma_t < 30\text{fs}σt<30fs -

接口设计:JESD204B(12.5Gbps/lane)

六、失效预防措施

- 混叠失真防护

-

抗混叠滤波器截止频率:

fc=0.8×fs2f_c = 0.8 \times \frac{f_s}{2}fc=0.8×2fs -

阻带衰减:>80dB> 80\text{dB}>80dB(8阶椭圆滤波器)

- 热管理设计

-

温漂补偿:

Vos=αTΔT(αT≈1μV/∘C)V_{\text{os}} = \alpha_T \Delta T \quad (\alpha_T \approx 1\mu\text{V}/^\circ\text{C})Vos=αTΔT(αT≈1μV/∘C) -

散热方案:

θJA<30∘C/W\theta_{JA} < 30^\circ\text{C}/ \text{W}θJA<30∘C/W(加散热垫)

- ESD防护设计

- 寄生电容:CTVS<1pFC_{\text{TVS}} < 1\text{pF}CTVS<1pF

七、选型对比总结表

| 类型 | 精度范围 | 速度范围 | 功耗 | 适用场景 |

|---|---|---|---|---|

| SAR | 12-18位 | 100k-10MSPS | <50mW | 工业控制/电池设备 |

| Σ-Δ | 16-32位 | 1-100kSPS | 10-100mW | 高精度测量 |

| Pipeline | 10-14位 | 100M-5GSPS | 200-800mW | 通信/雷达 |

| Flash | 6-10位 | >1GSPS | >1W | 超高速采集 |

高速选Pipeline,高精选Σ-Δ,均衡选SAR,极速选Flash。通过精准选型+严谨设计,可释放ADC芯片95%的标称性能。在5G基站、医疗影像等高端应用中,Pipeline和Σ-Δ的组合方案已成为行业标配。

1008

1008

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?