记录Quartus中遇到的报错

一、Failed to launch MegaWizard Plug-In Manager

报错:Failed to launch MegaWizard Plug-In Manager. PLL IntelFPGA IP v18.1 could not be found in the specified librarypaths.

原因:编译后无法再打开IP核查看了,因为为Inter收购Altera后一些名称的改动没改好

解决方法一:找到Quartus安装路径D:\intelFPGA\18.1\ip\altera\altera_pll\pll_wizard.plt,用文本编辑器打开

[Basic Functions|Clocks; PLLs and Resets|PLL]

Altera PLL v18.1= "%t" "%w/../common/lib/megawizard.pl" --wizard:altera_pll --early_gen:on --wizard_file:"%w/source/top/pll_hw.tcl" --familyparameter:device_family %f %o %h

<INFO>

<QIP_FILE_ENABLED/>

<ACCEPT_OTHER_CNX VALUE="ON"/>

<DEVICE_FAMILY SUPPORTED="NONE | Stratix V | Arria V | Cyclone V | Arria V GZ" SUPPORT_CHECK="ON" />

<LANGUAGES AHDL="OFF"/>

<PINPLAN SUPPORTED="ON"/>

<ALIAS>Altera PLL</ALIAS>

<ALIAS>Altera PLL v10.0</ALIAS>

<ALIAS>Altera PLL v10.1</ALIAS>

<ALIAS>Altera PLL v11.0</ALIAS>

<ALIAS>Altera PLL v11.1</ALIAS>

<ALIAS>Altera PLL v12.0</ALIAS>

<ALIAS>Altera PLL v12.1</ALIAS>

<ALIAS>Altera PLL v13.0</ALIAS>

<ALIAS>Altera PLL v13.1</ALIAS>

<ALIAS>Altera PLL v14.0</ALIAS>

<ALIAS>Altera PLL v14.1</ALIAS>

<ALIAS>Altera PLL v15.0</ALIAS>

<ALIAS>Altera PLL v15.1</ALIAS>

<ALIAS>Altera PLL v16.0</ALIAS>

<ALIAS>Altera PLL v16.1</ALIAS>

<ALIAS>Altera PLL v17.0</ALIAS>

<ALIAS>Altera PLL v17.1</ALIAS>

<ALIAS>Altera PLL v18.0</ALIAS>

<ALIAS>Altera PLL v18.1</ALIAS>

<ALIAS>Altera PLL v19.0</ALIAS>

<ALIAS>Altera PLL v19.1</ALIAS>

<ALIAS>Altera PLL v20.0</ALIAS>

<ALIAS>Altera PLL v20.1</ALIAS>

</INFO>

将<ALIAS>后的Altra PLL修改成PLL Intel FPGA,对应自己的版本即可

[Basic Functions|Clocks; PLLs and Resets|PLL]

Altera PLL v18.1= "%t" "%w/../common/lib/megawizard.pl" --wizard:altera_pll --early_gen:on --wizard_file:"%w/source/top/pll_hw.tcl" --familyparameter:device_family %f %o %h

<INFO>

<QIP_FILE_ENABLED/>

<ACCEPT_OTHER_CNX VALUE="ON"/>

<DEVICE_FAMILY SUPPORTED="NONE | Stratix V | Arria V | Cyclone V | Arria V GZ" SUPPORT_CHECK="ON" />

<LANGUAGES AHDL="OFF"/>

<PINPLAN SUPPORTED="ON"/>

<ALIAS>Altera PLL</ALIAS>

<ALIAS>Altera PLL v10.0</ALIAS>

<ALIAS>Altera PLL v10.1</ALIAS>

<ALIAS>Altera PLL v11.0</ALIAS>

<ALIAS>Altera PLL v11.1</ALIAS>

<ALIAS>Altera PLL v12.0</ALIAS>

<ALIAS>Altera PLL v12.1</ALIAS>

<ALIAS>Altera PLL v13.0</ALIAS>

<ALIAS>Altera PLL v13.1</ALIAS>

<ALIAS>Altera PLL v14.0</ALIAS>

<ALIAS>Altera PLL v14.1</ALIAS>

<ALIAS>Altera PLL v15.0</ALIAS>

<ALIAS>Altera PLL v15.1</ALIAS>

<ALIAS>Altera PLL v16.0</ALIAS>

<ALIAS>Altera PLL v16.1</ALIAS>

<ALIAS>Altera PLL v17.0</ALIAS>

<ALIAS>Altera PLL v17.1</ALIAS>

<ALIAS>Altera PLL v18.0</ALIAS>

<ALIAS>PLL Intel FPGA v18.1</ALIAS>

<ALIAS>Altera PLL v19.0</ALIAS>

<ALIAS>Altera PLL v19.1</ALIAS>

<ALIAS>Altera PLL v20.0</ALIAS>

<ALIAS>Altera PLL v20.1</ALIAS>

</INFO>

解决方法二:在PLL.qip->PLL.v的第一行的注释,将PLL Intel FPGA vXX.X改成Altera PLL vXX.X

二、 quartus调用IP核无法生成.vo文件

问题:在Quartus中调用IP核后无法生成.vo文件,导致modelsim报错

解决方法:在Quartus的Assignments->Settings->EDA Tool Settings中,勾选Run gate-level simulation automatically after compilation,再重新编译即可

用上面解决办法后每次编译完就会进行modelsim仿真,可以仿真完成后再取消勾选

三、QSYS在Generate HDL时报错

Error: border: Error during execution of script generate_hps_sdram. tcl: seq: Error during execution of "{D:/intelfpga/23.1std/quartus/.. /nios2eds/Nios II Command Shell.bat} make all 2>> stderr.txt": child process exited abnormally

因为从quartus 19.1标准版开始的Nios II EDS开始,Cygwin组件就被替换成WSL,需要安装WSL

解决方法:如何在 Windows*作系统上安装面向 Linux* 的 Windows* 子系统 (WSL)?

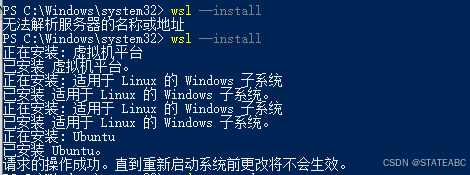

tips:最好是通过管理员打开power shell,输入wsl --install进行WSL的安装

如果遇到“无法解析服务器的名称或地址”,可以挂梯子

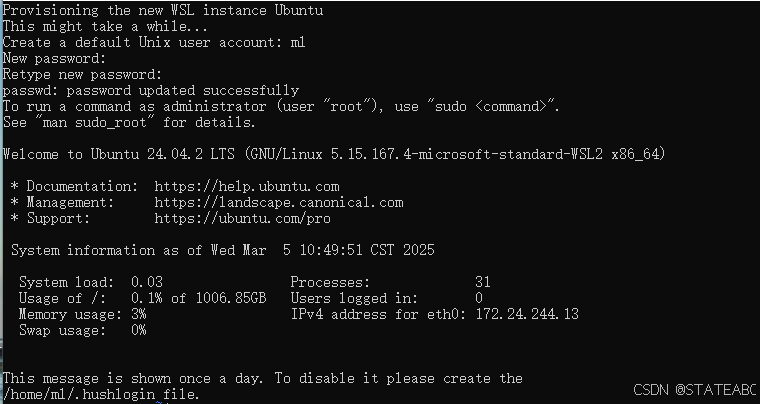

安装WSL完成后重启电脑,可以在开始菜单打开Ubuntu,打开后需要一段时间进行安装并且设置用户名和密码

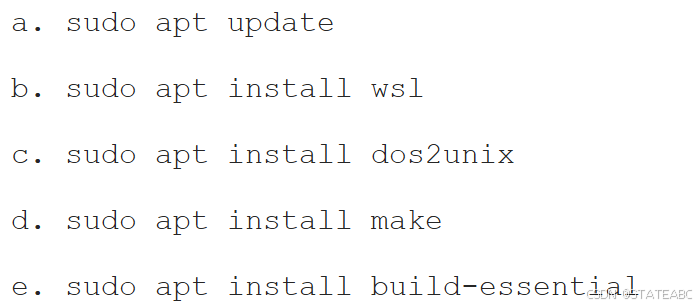

安装完成后输入以下命令安装NIOS

四、quartus中调用DDR3 IP核编译报错

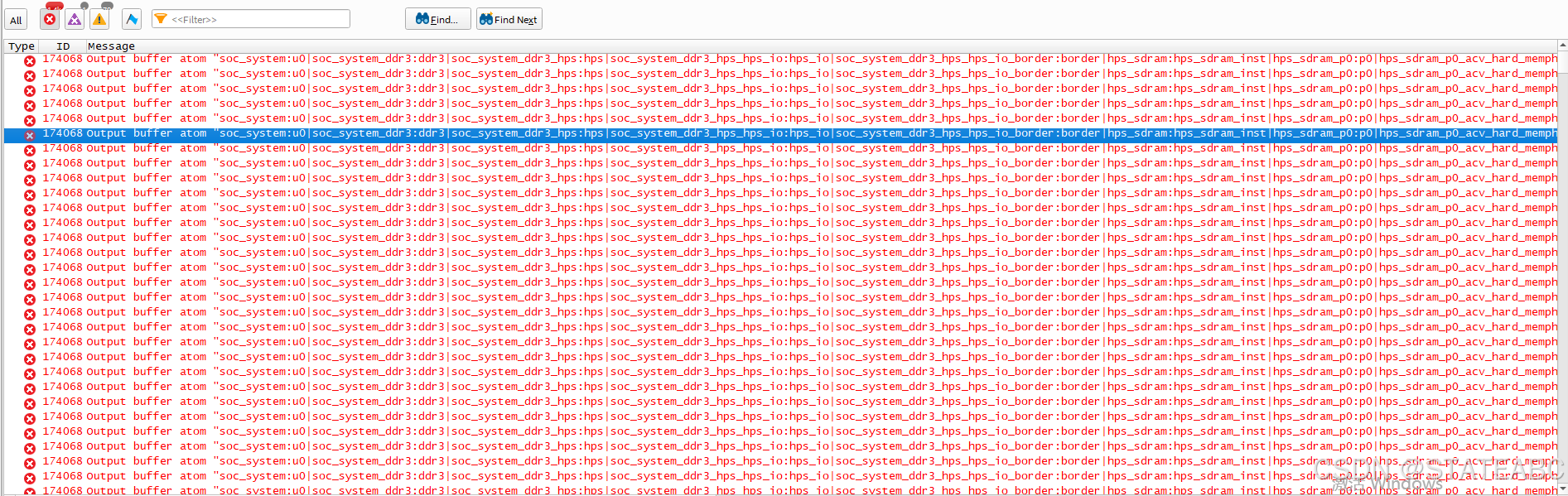

Error (174068): Output buffer atom "soc_system:u0|soc_system_ddr3_0:ddr3_0|soc_system_ddr3_0_hps:hps|soc_system_ddr3_0_hps_hps_io:hps_io|soc_system_ddr3_0_hps_hps_io_border:border|hps_sdram:hps_sdram_inst|hps_sdram_p0:p0|hps_sdram_p0_acv_hard_memphy:umemphy|hps_sdram_p0_acv_hard_io_pads:uio_pads|hps_sdram_p0_altdqdqs:dq_ddio[0].ubidir_dq_dqs|altdq_dqs2_acv_connect_to_hard_phy_cyclonev:altdq_dqs2_inst|extra_output_pad_gen[0].obuf_1" has port "SERIESTERMINATIONCONTROL[0]" connected, but does not use calibrated on-chip termination

解决方法:

解决方法:

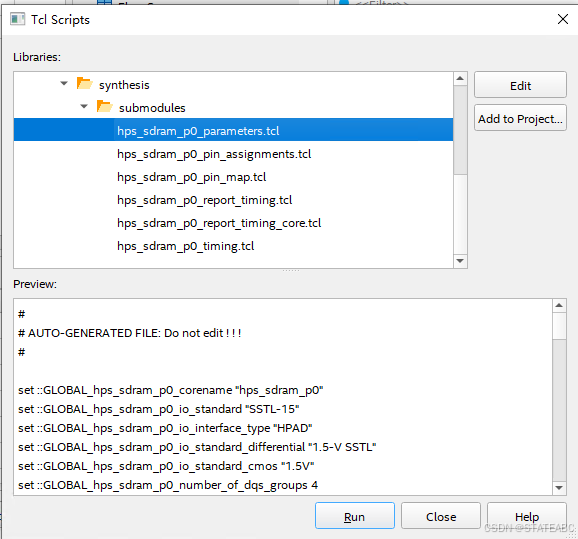

运行pin_assignments.tcl文件

tools>>Tcl Scripts,运行后缀为*_pin_assignments.tcl和*_piin_assignments.tcl

本文讲述了在Quartus中遇到的两个问题:1)因Intel收购Altera导致的MegaWizardPlug-InManager启动失败,需修改PLLIntelFPGA的alias;2)IP核调用后无法生成vo文件,需在设置中勾选自动运行门级仿真。

本文讲述了在Quartus中遇到的两个问题:1)因Intel收购Altera导致的MegaWizardPlug-InManager启动失败,需修改PLLIntelFPGA的alias;2)IP核调用后无法生成vo文件,需在设置中勾选自动运行门级仿真。

5205

5205

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?