原文来源

ARM的Cortex-R5技术参考手册,为网页版,也可以下载pdf。

下载地址:https://developer.arm.com/documentation/ddi0460/d/

《Cortex-R5 Technical Reference Manual.pdf》

ARM DDI 0460D

第14页,第1.1节

英文原文

1.1 About the processor

The Cortex-R5 processor is a mid-range CPU for use in deeply-embedded, real-time systems.

It implements the ARMv7-R architecture, and includes Thumb-2 technology for optimum code

density and processing throughput. The pipeline has a single Arithmetic Logic Unit (ALU), but

implements limited dual-issuing of instructions for efficient utilization of other resources such

as the register file. A hardware Accelerator Coherency Port (ACP) is provided to reduce the

requirement for slow software cache maintenance operations when sharing memory with other

masters.

Interrupt latency is kept low by interrupting and restarting load-store multiple instructions, and

by use of a dedicated peripheral port that enables low-latency access to an interrupt controller.

The processor has Tightly-Coupled Memory (TCM) ports for low-latency and deterministic

accesses to local RAM, in addition to caches for higher performance to general memory.

Error Checking and Correction (ECC) is used on the Cortex-R5 processor ports and in Level 1

(L1) memories to provide improved reliability and address safety-critical applications.

Many of the features, including the caches, TCM ports, and ECC are configurable so that a given

processor implementation can be tailored to the application for efficient area usage.

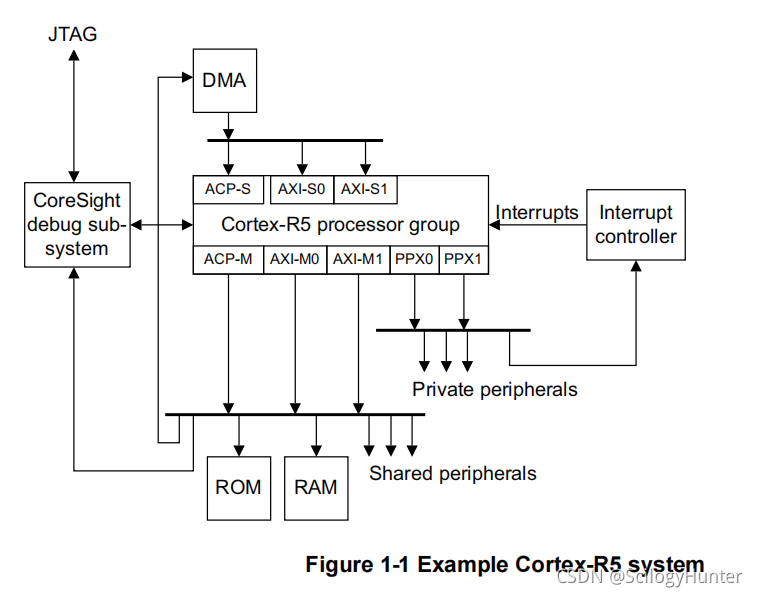

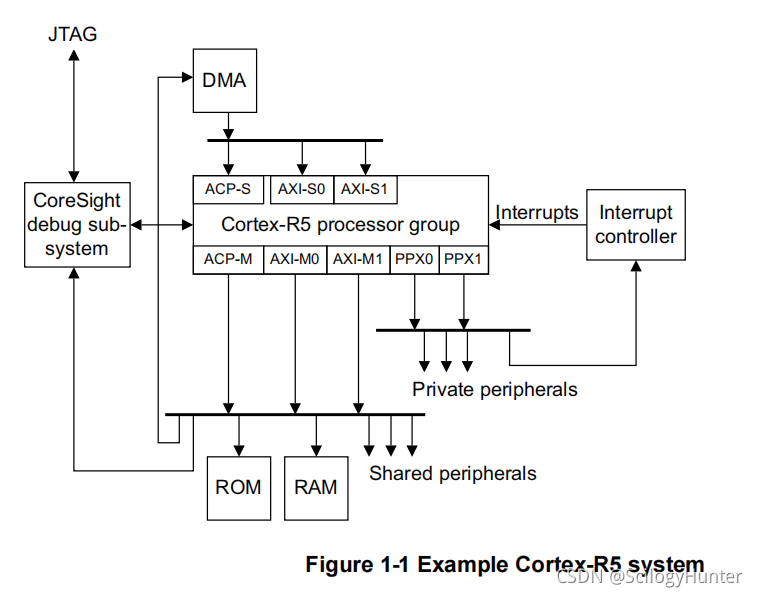

Figure 1-1 shows the processor in a typical system.

单词表

| 单词 | 音标 | 释意 |

|---|---|---|

| processor | /ˈprəʊsesə/ | 处理器;处理程序 |

| implement | /ˈɪmplɪment/ | vt. 实施,执行;实现,使生效 n. 工具,器具;手段 |

| optimum | /ˈɒptɪməm/ | adj. 最适宜的 n. 最佳效果;最适宜条件 |

| density | /ˈdensəti/ | n. 密度 |

| pipeline | /ˈpaɪplaɪn/ | n. 管道;输油管;传递途径;流水线 |

| efficient | /ɪˈfɪʃnt/ | adj. 有效率的;有能力的;生效的 |

| resource | /rɪˈsɔːs; rɪˈzɔːs/ | n. 资源,财力;办法;智谋 vi. 向…提供资金 |

| maintenance | /ˈmeɪntənəns/ | n. 维护,维修;保持;生活费用 |

| dedicated | /ˈdedɪkeɪtɪd/ | adj. 专用的;专注的;献身的 |

| latency | /ˈleɪtənsi/ | n. 潜伏;潜在因素;延迟,时延 |

| deterministic | /dɪˌtɜːmɪˈnɪstɪk/ | adj. 确定性的;命运注定论的 |

| reliability | /rɪˌlaɪəˈbɪləti/ | 可靠性 |

| correction | /kəˈrekʃn/ | n. 改正,修正 |

| tailored | /ˈteɪləd/ | adj. 定制的, v. 专门制作,定制; |

| 短语 | 释意 |

|---|---|

| mid-range | 中级,中等 |

| deeply-embedded | 深度嵌入式 |

| real-time | 实时 |

| Arithmetic Logic Unit | ALU,算术逻辑单元 |

| register file | [计] 寄存器文件;寄存蒲 |

| dual-issuing of instructions | 双指令派发 |

| Accelerator Coherency Port, ACP | 加速器一致性接口 |

| Interrupt latency | 中断延迟 |

| load-store | 加载与存储 |

| safety-critical | 安全关键 |

| – | – |

| – | – |

全文翻译

1.1 About the processor

关于此处理器

The Cortex-R5 processor is a mid-range CPU for use in deeply-embedded, real-time systems.

Cortex-R5处理器是一个为深度嵌入、实时系统应用的中级CPU。

It implements the ARMv7-R architecture, and includes Thumb-2 technology for optimum code

它由ARMv7-R体系结构实现,包括为最佳代码密度和处理吞吐量的Thumb-2技术。

density and processing throughput. The pipeline has a single Arithmetic Logic Unit (ALU), but

流水线只有单个算术逻辑单元(ALU)

implements limited dual-issuing of instructions for efficient utilization of other resources such

但是提供有限的的双指令派发功能,以有效利用处理器其他资源如寄存器组。

as the register file. A hardware Accelerator Coherency Port (ACP) is provided to reduce the

一个硬件加速器一致性接口被提供

requirement for slow software cache maintenance operations

以减少请求,降低软件缓存维护操作

when sharing memory with other masters.

当和其他总线主机共享内存时

Interrupt latency is kept low by interrupting and restarting load-store multiple instructions, and

通过可中断重启的多加载存储指令中断延迟被保持的很低

by use of a dedicated peripheral port that enables low-latency access to an interrupt controller.

并且通过专用外设接口可以低延迟的访问中断控制器

The processor has Tightly-Coupled Memory (TCM) ports for low-latency and deterministic

此处理器具备紧耦合存储(TCM)接口,用于低延迟和确定性的访问本地存储,

accesses to local RAM, in addition to caches for higher performance to general memory.

此外还有缓存,用于提高一般内存的性能。

Error Checking and Correction (ECC) is used on the Cortex-R5 processor ports and in Level 1

(L1) memories to provide improved reliability and address safety-critical applications.

错误无检查纠正单元(ECC)用于Cortex-R5处理器端口和L1内存,以提功高可靠性,并解决对安全至关重要的应用。

Many of the features, including the caches, TCM ports, and ECC are configurable so that a given

许多特性,包括缓存、TCM端口和ECC,都是可配置的,

processor implementation can be tailored to the application for efficient area usage.

因此,为了一个高效芯片面积的具体应用的处理器实现可以被定制

Figure 1-1 shows the processor in a typical system.

图1-1展示了一个典型处理器系统

ARM Cortex-R5是一款适用于深度嵌入式实时系统的中端CPU,采用ARMv7-R架构,支持Thumb-2技术以实现最佳代码密度和处理效率。处理器具有单个ALU并实现有限的双指令发布,提供硬件加速器一致性端口以优化资源共享。其低中断延迟通过中断和重启加载存储指令以及专用外设端口实现。此外,还包含紧耦合内存(TCM)和L1内存的错误检查和校正(ECC),确保可靠性和安全性。处理器配置可根据具体应用进行定制。

ARM Cortex-R5是一款适用于深度嵌入式实时系统的中端CPU,采用ARMv7-R架构,支持Thumb-2技术以实现最佳代码密度和处理效率。处理器具有单个ALU并实现有限的双指令发布,提供硬件加速器一致性端口以优化资源共享。其低中断延迟通过中断和重启加载存储指令以及专用外设端口实现。此外,还包含紧耦合内存(TCM)和L1内存的错误检查和校正(ECC),确保可靠性和安全性。处理器配置可根据具体应用进行定制。

5686

5686

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?