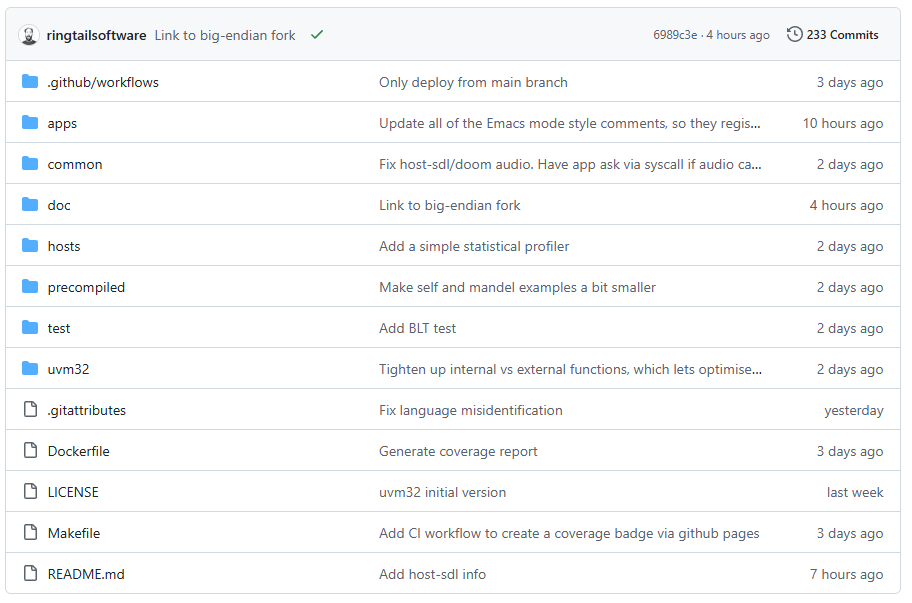

https://github.com/ringtailsoftware/uvm32

uvm32是一款极简、无依赖的虚拟机沙箱,专为微控制器及其他资源受限设备设计。采用单文件C语言实现,无动态内存分配,采用异步架构,完全兼容C99标准。在STM32L0(ARM Cortex-M0+)平台上,其存储占用低于3KB闪存/1KB RAM。

uvm32本质上是封装了管理接口的RISC-V模拟器,并提供配套工具链以构建可在其中运行的高效代码。

应用场景

1、作为嵌入式脚本引擎(Lua、Duktape、MicroPython等)的轻量替代方案

2、作为隔离系统中不可信或不稳定组件的安全沙箱

3、在目标平台缺乏编译器的场景下,支持使用现代系统编程语言开发(如Rust示例)

4、实现"一次编写,随处运行",避免维护多版本软件

核心特性

1、提供C、Zig、Rust及汇编语言的字节码示例程序

2、非阻塞设计,防止异常字节码阻塞主机系统

3、不预设主机IO能力(无标准IO依赖)

4、简洁而明确执行模型

5、安全的最小化类型FFI接口

6、既可满足简单脚本/插件需求,亦能支持复杂场景

安全性优先于速度,确保虚拟机内的异常代码永远不会导致主机崩溃,虽基于完整CPU模拟器实现,但专注于执行自定义脚本逻辑,而非硬件模拟

与同类方案的比较

现有许多适用于小型系统的脚本语言与虚拟机都在不同维度做出了权衡取舍。

uvm32致力于:

1、极小资源占用(适配嵌入式设备、游戏及应用)

2、支持使用成熟编程语言开发虚拟机代码(配备高质量开发工具)

3、易于集成至现有软件体系

4、支持多种编程范式(事件驱动、轮询、多处理器)

对异常虚拟机代码具备强容错性

uvm32不追求:

1、零摩擦FFI(主机与虚拟机代码间无直接函数调用)

2、极限运行效率

3、最简单的脚本开发体验(需要完整的开发-编译-运行周期)

"开箱即用"的标准IO、网络等功能库

项目结构说明

uvm32是微型虚拟机的核心实现,所有代码均位于uvm32目录中。

host-mini展示了运行虚拟机代码的最简主机示例。

其余目录均为进阶主机示例,或可供主机运行的示例应用程序。

1539

1539

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?