FPGA VHDL语言实现FIR低通滤波器,包含完整代码,可在modelsim仿真

可仿真,可在FPGA开发板硬件实现

ID:94150683735518602

yqgo

本文将围绕FPGA VHDL语言实现FIR低通滤波器展开讨论。在介绍之前,先简要概述一下FPGA和VHDL的基本概念。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重构性,使得它成为了一种理想的硬件开发平台。相比于传统的专用集成电路(ASIC),FPGA具有更高的开发效率和更低的成本。而VHDL(VHSIC Hardware Description Language)则是一种硬件描述语言,它可以用于描述数字电路的结构和行为。

在本文中,我们将利用VHDL语言来实现一个FIR低通滤波器。FIR滤波器是一种常见的数字滤波器,它的特点是系统稳定性好、抗干扰能力强以及易于设计和实现。FIR滤波器的工作原理基于线性卷积,它通过对输入信号进行加权和延时来实现滤波效果。

FIR低通滤波器的设计目标是将高频信号抑制,只保留低频信号。在实际应用中,我们通常需要根据具体需求来选择滤波器的截止频率和滤波器阶数。截止频率决定了滤波器对高频信号的抑制程度,而滤波器阶数则决定了滤波器的陡峭程度。

在VHDL代码实现方面,我们首先需要定义FIR滤波器的结构。一般来说,FIR滤波器由输入端、输出端和一系列的延时单元组成。在FIR滤波器的每一个延时单元中,我们需要定义滤波器的系数和延时。

接下来,我们将介绍如何在VHDL中实现FIR滤波器的功能。首先,我们需要定义输入和输出信号的数据类型和位宽。对于输入信号,我们可以选择使用标量或矢量来表示。然后,我们需要定义滤波器的系数,这些系数将用于对输入信号进行加权。在定义系数时,我们可以使用一维数组或者ROM来存储。最后,我们需要定义延时单元的个数以及每个延时单元的延时长度。

一旦我们完成了FIR滤波器的结构和参数定义,我们就可以开始编写核心的滤波器逻辑。对于FIR滤波器来说,核心逻辑就是对输入信号进行加权和延时。在VHDL中,我们可以使用for循环来实现这一功能。

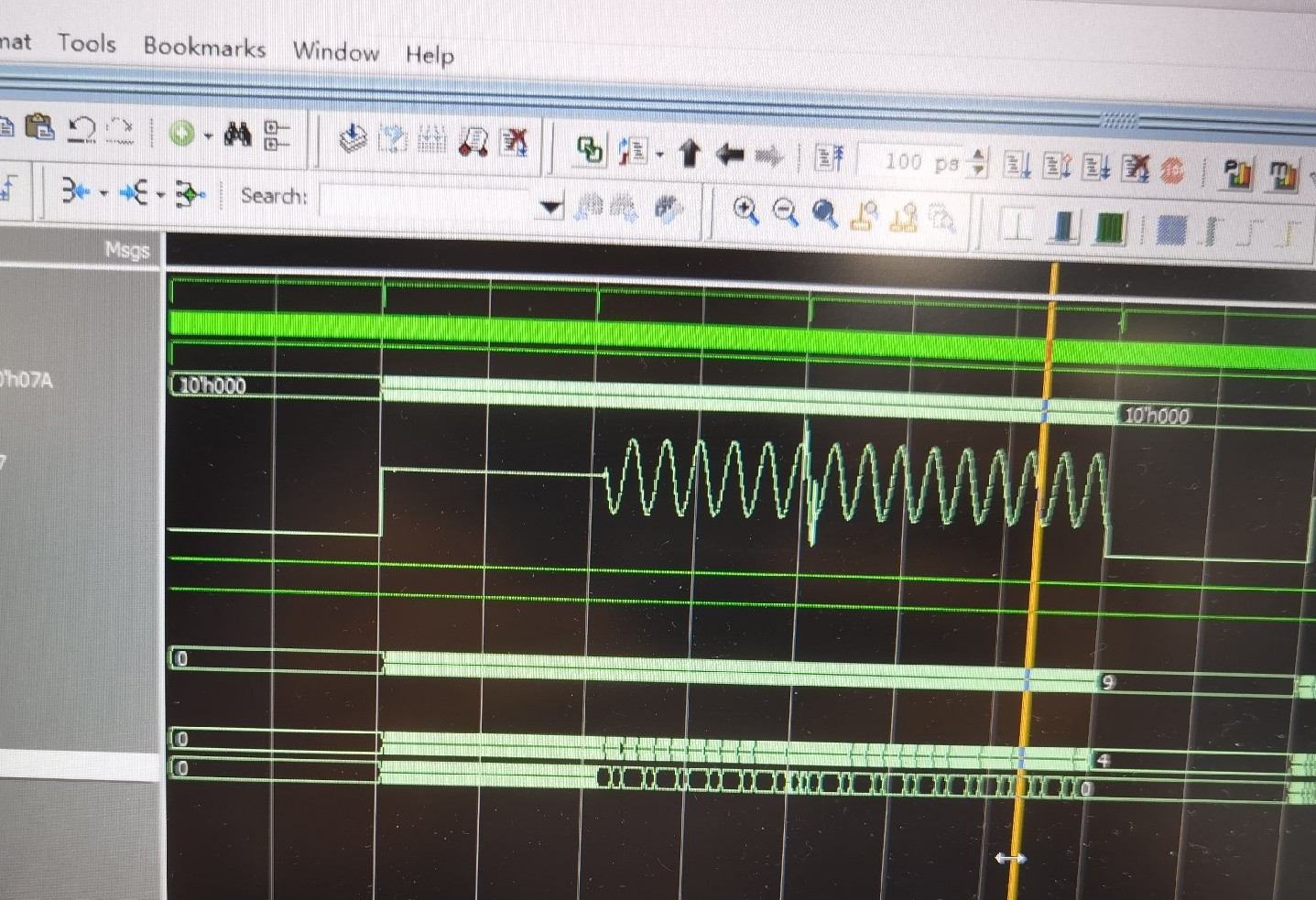

在编写完FIR滤波器的核心逻辑后,我们就可以进行仿真了。我们可以使用仿真工具(如ModelSim)对FIR滤波器进行验证。通过输入一组测试信号,我们可以观察滤波器的输出是否符合预期,并进行必要的调整和优化。

一旦通过了仿真验证,我们就可以将FIR滤波器实现在FPGA开发板上。这样,我们就能够在硬件上实现滤波器的功能,从而达到更高的处理速度和更低的延时。

总结一下,本文介绍了如何利用VHDL语言实现FIR低通滤波器。通过定义滤波器的结构、参数和延时单元,编写核心的滤波器逻辑,并进行仿真验证和硬件实现,我们可以实现一个功能完善且性能优越的FIR低通滤波器。希望本文能够为读者提供有关FPGA VHDL语言实现FIR低通滤波器的详细介绍和实际操作指南。

以上相关代码,程序地址:http://wekup.cn/683735518602.html

538

538

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?