【Vivado那些事儿】两种创建工程的方法

前言

本篇介绍了两种创建工程的方法,一种是根据向导进行创建,一种是直接使用tcl指令进行创建,还简单介绍了工程参数在哪进行更改。

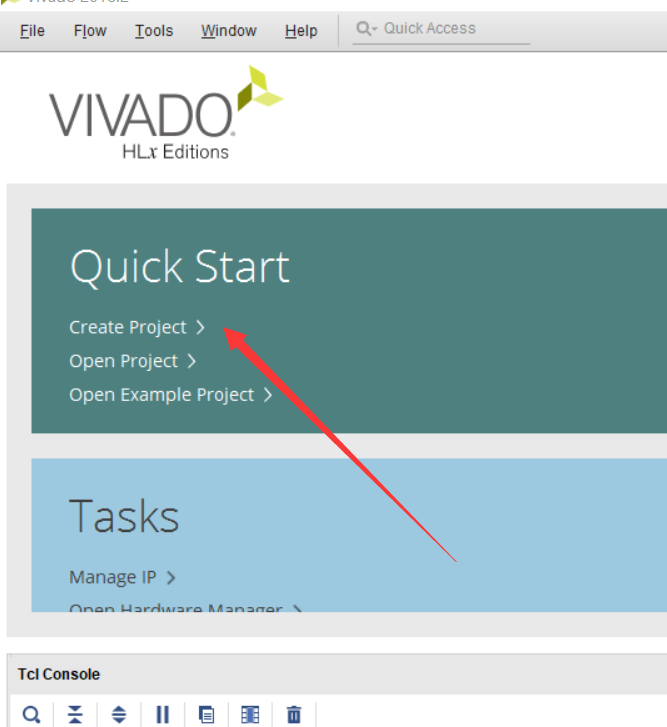

创建工程【方法1】

打开Vivado的初始界面后,可以直接点击Create Project

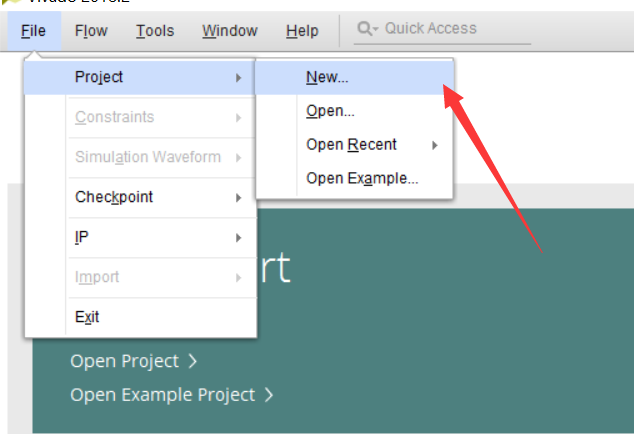

也可以在菜单栏File > Project > New

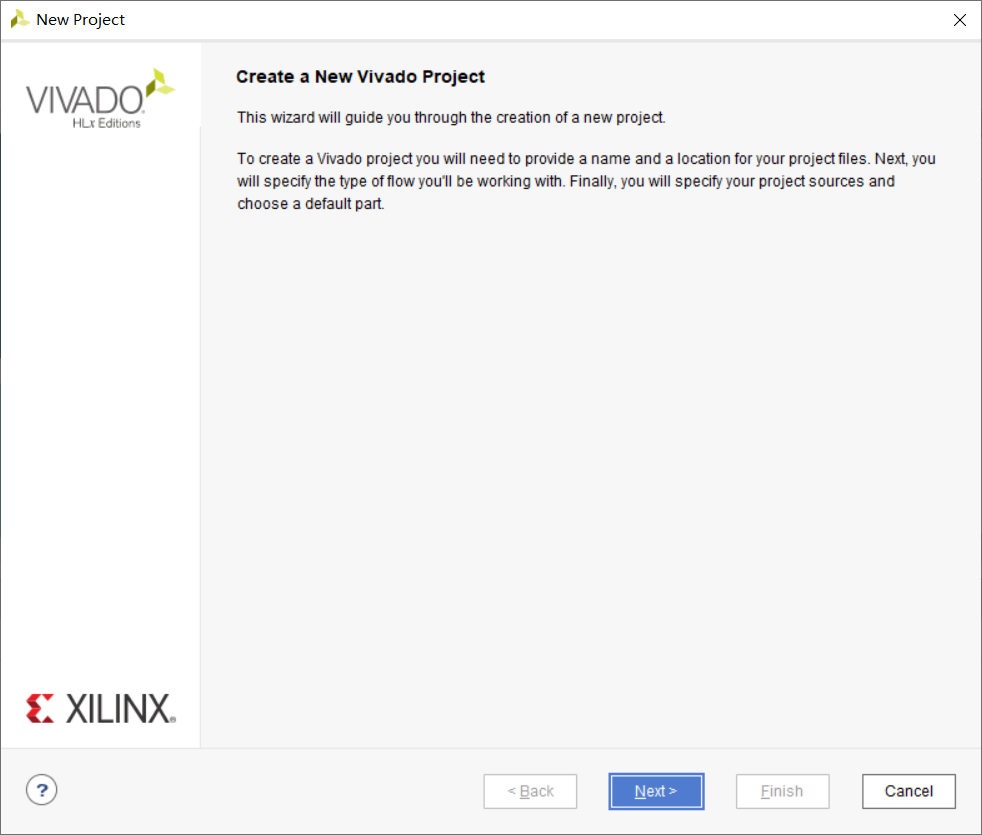

然后会出现创建工程的向导

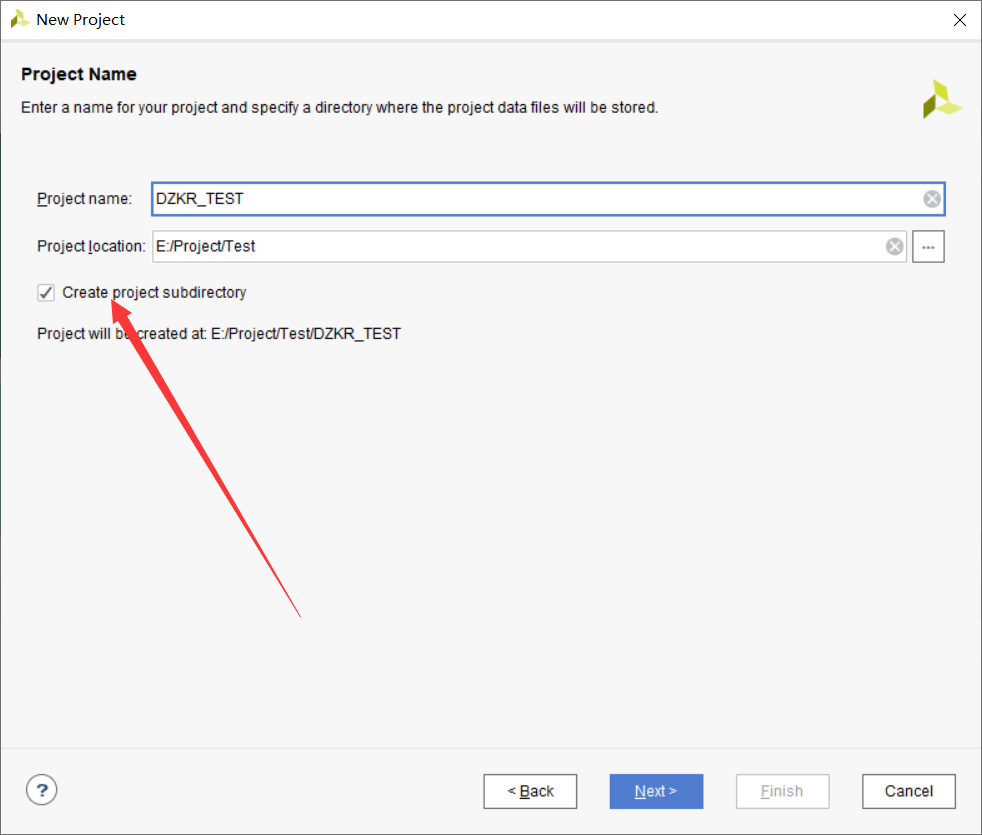

点击Next,进入设置工程名以及指定存放路径的界面

箭头所指项,代表是否在指定的路径下,将工程以子文件夹的形式存在,工程的文件夹名为工程名,可能看得有点绕,直接看效果

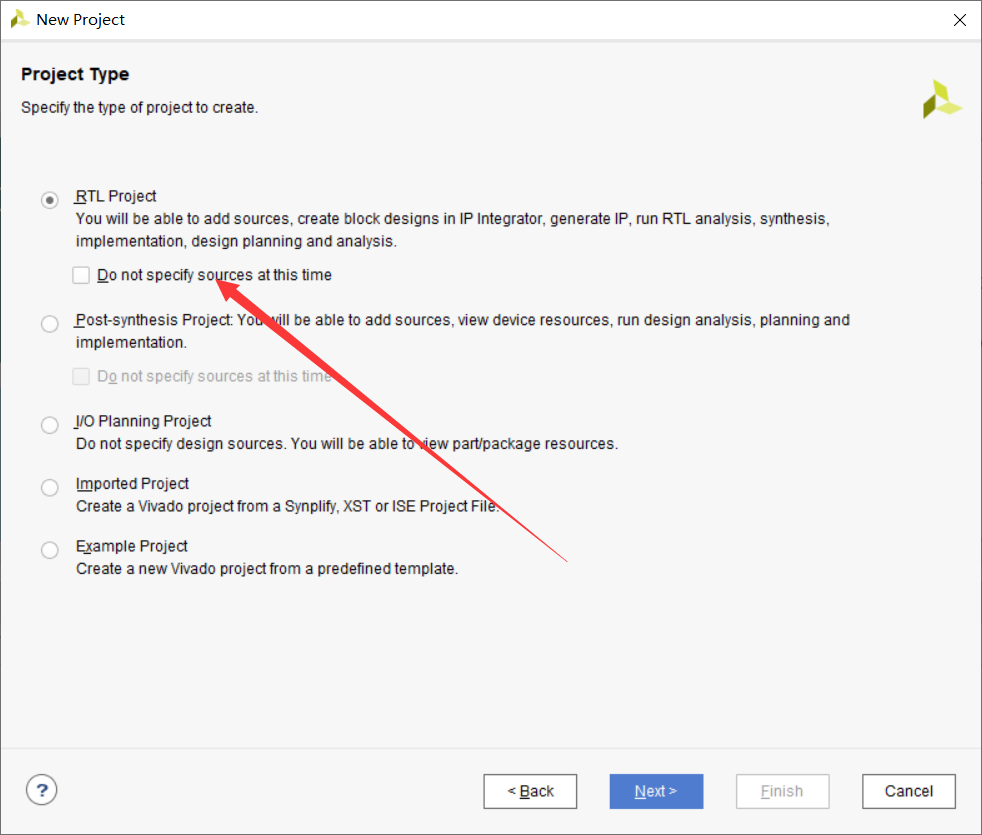

然后点击Next,进入工程类型的选择界面,第一个就是我们常用的RTL工程,其他的依次是设计综合后工程、IO计划工程、导入(Synplify、XST或者ISE)创建的工程以及示例工程,直接以第一个进行举例,其他的就不讲了,操作都没啥区别。

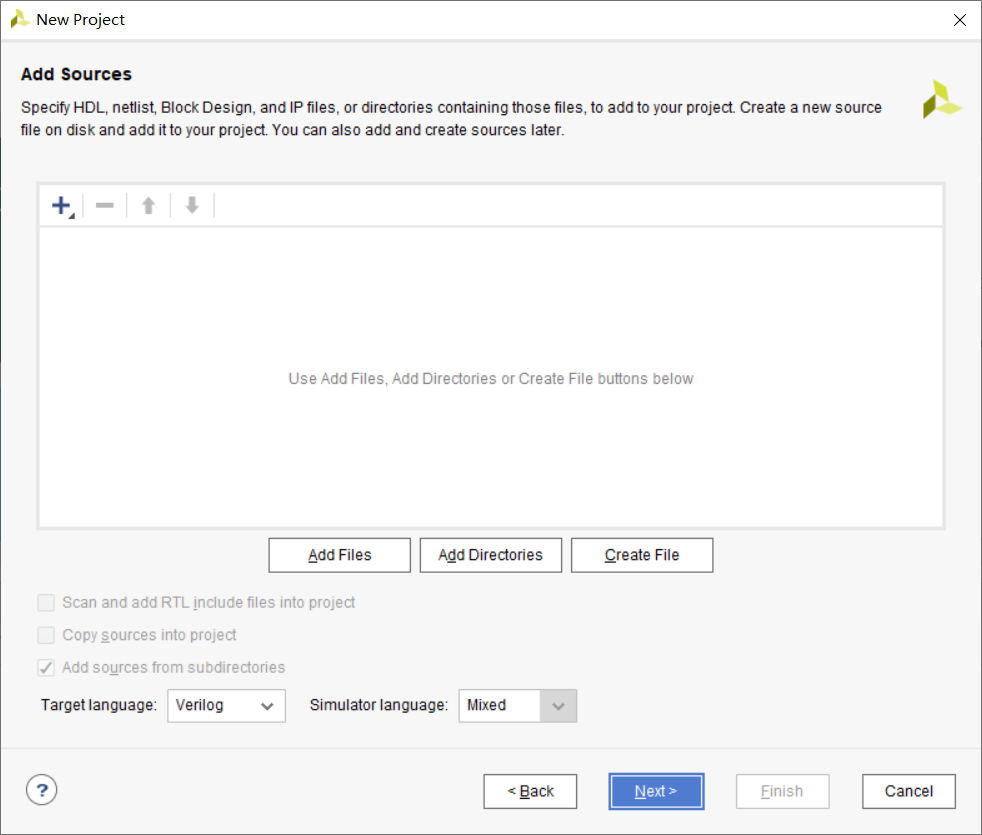

箭头所指项,勾上代表创建工程的时候不定义源文件,反之,需要在创建工程的时候,就把需要用到的源文件添加到该工程,没勾上时,点击Next会出现以下添加源文件的界面,这边就先不做添加和创建的示例。

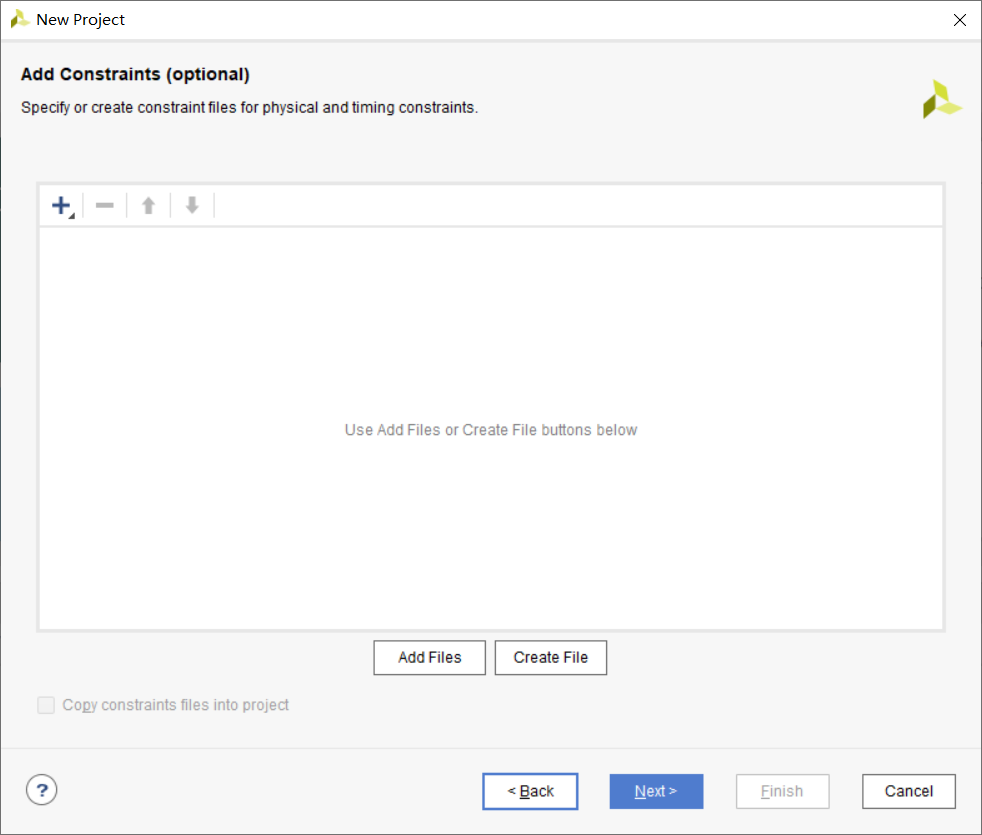

源文件指定后,然后继续Next就是指定约束文件,也就是管脚约束、时序约束的那个XDC文件。

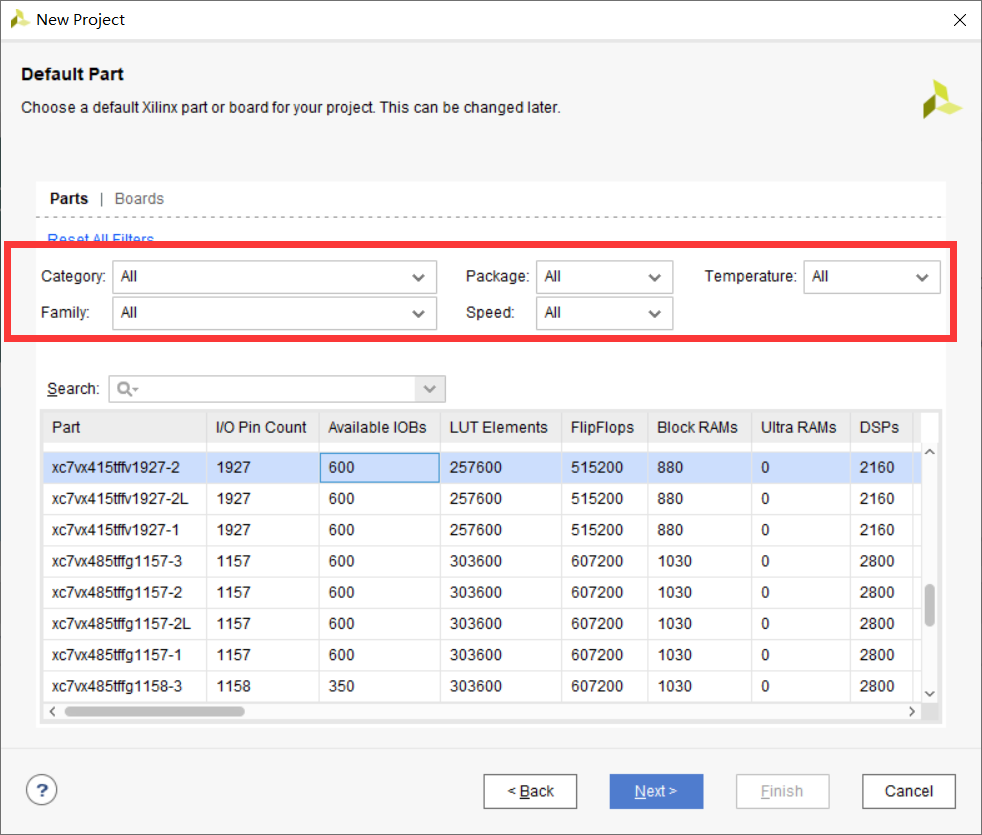

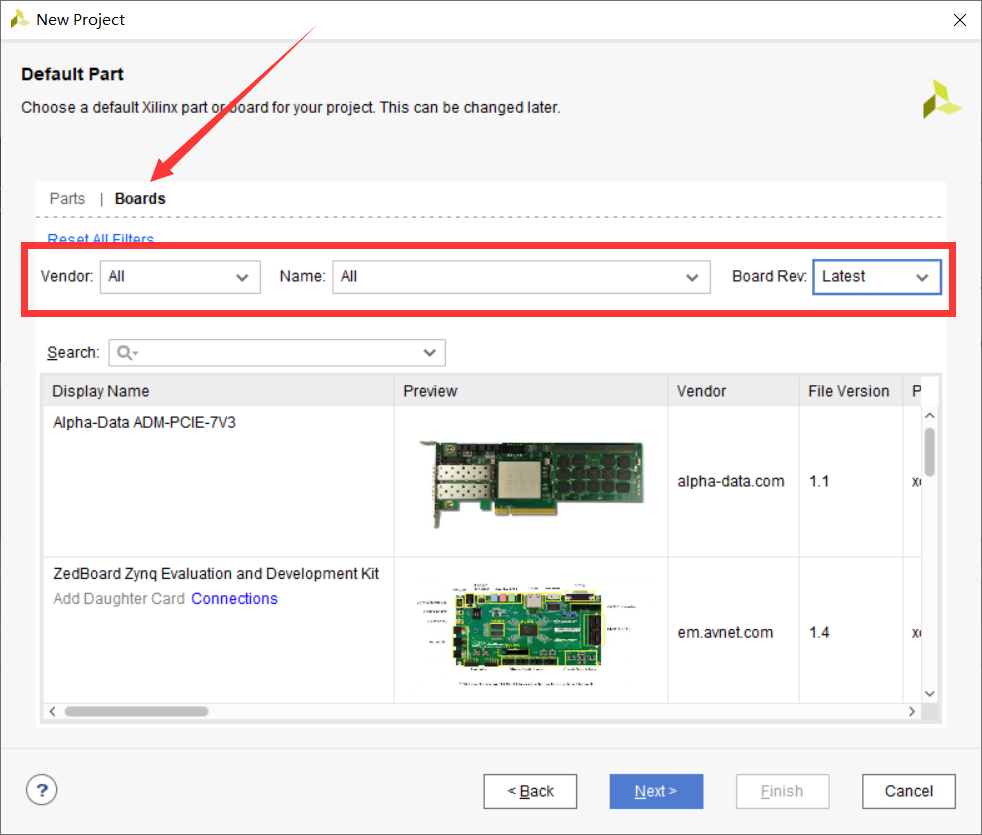

继续下一步就是进入器件选择,如果在工程类型的那一界面勾上了(Do not specify sources at this time)则会跳过以上两个添加源文件和约束文件的界面,直接到该界面,该部分用于指定该工程使用的器件,可以根据红框中的类别进行查找,也可以直接搜索对应的芯片名(Search),

如果是使用的官方的评估板,那就更轻松了,直接查自己的板卡是哪个,选上就完事

如果创建完工程之后发现工程用的器件设置错了,也能更改,之后介绍到Setting的时候再说下,先接着往下看,选好器件后,Next,出现工程的摘要,然后觉得信息都对了,就可以Finish,完成创建。

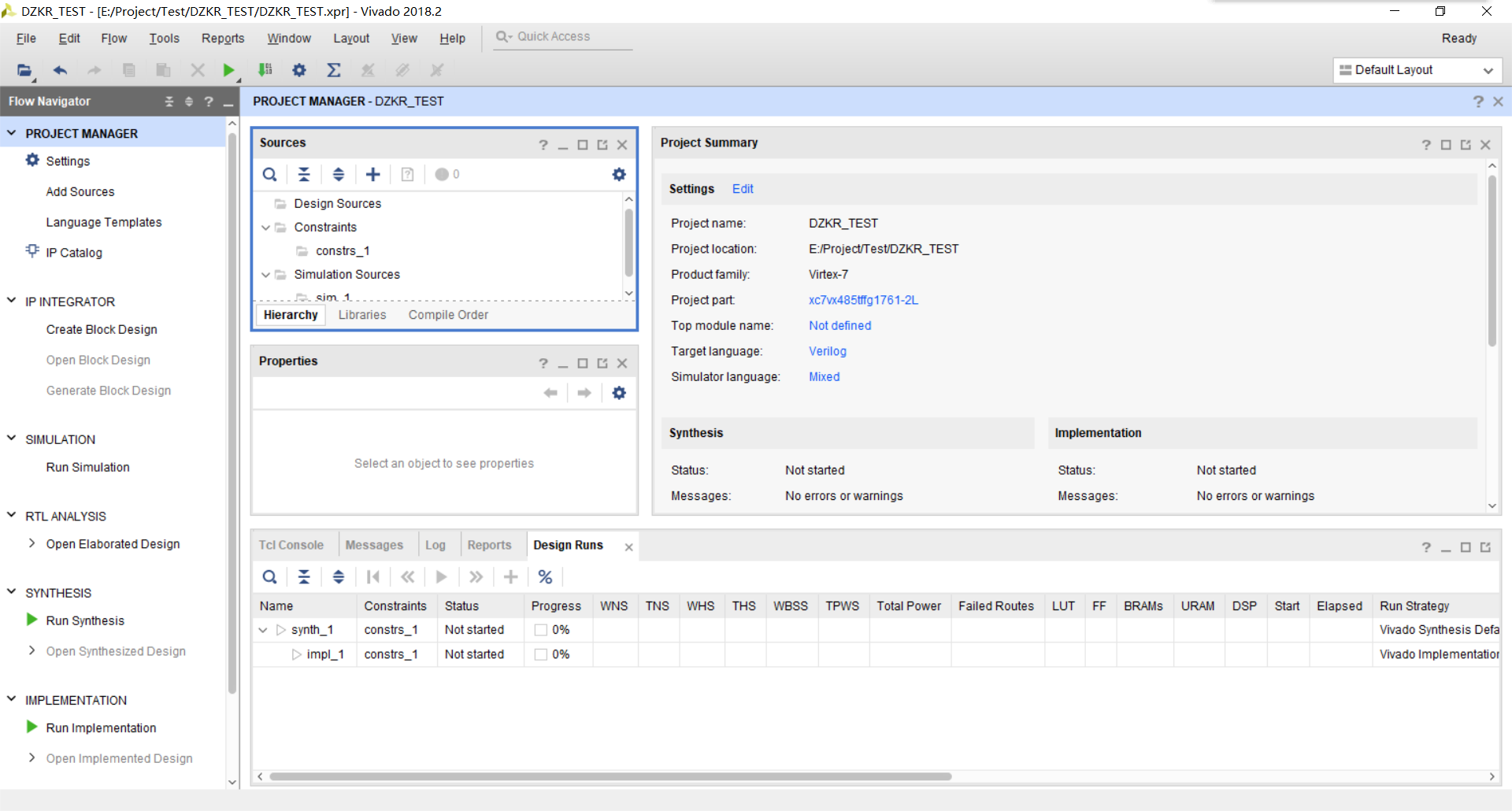

创建完成出现的界面如下

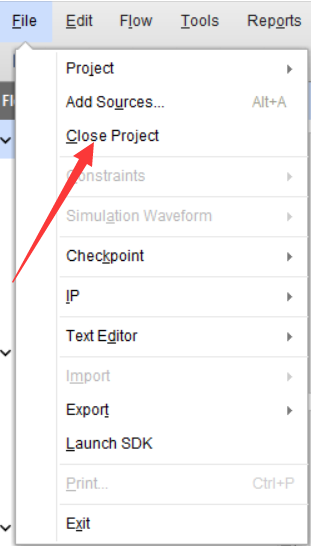

关掉该工程,接下来用TCL命令来创建工程,可以根据以下箭头所指关闭当前工程。

创建工程【方法2】

刚开始学习Vivado的时候,用界面创建工程显然是用着很舒服的,但是用久了,总会想要可以快速创建的方法,于是tcl就可以用起来了,用tcl命令创建工程的语法如下:

create_project [-part <arg>] [-force] [-in_memory] [-ip] [-rtl_kernel] [-quiet] [-verbose] [<name>] [<dir>]

| 名称 | 说明 |

|---|---|

| [-part ] | 目标器件 |

| [-force] | 覆盖现有目录(若已存在相同文件) |

| [-in_memory] | 创建一个内存中的工程 |

| [-ip] | 管理IP的工程 |

| [-rtl_kernel] | 针对RTL Kernel的工程 |

| [-quiet] | 忽略命令的错误 |

| [-verbose] | 执行命令的时候挂起消息限制 |

| [] | 工程名 |

| [

| 工程路径 |

以上的指令在创建一个工程的时候,不一定全部都加上,可以根据自己需要做删减,比如我只想实现一个空的RTL工程的创建,类似一开始通过界面创建的工程,甚至器件也暂时不设置,指令则只需要:create_project+工程名+工程路径,具体如下:

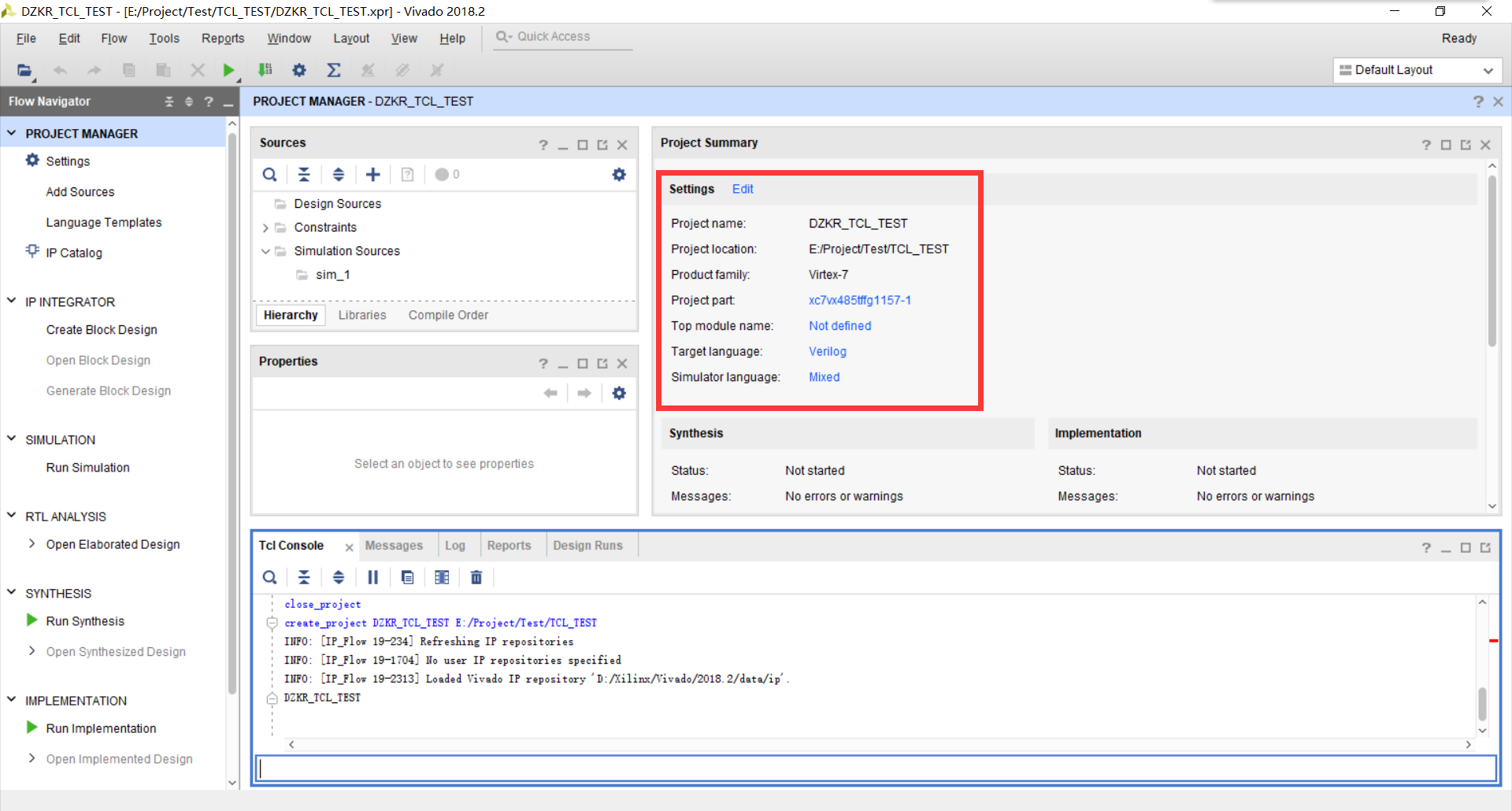

create_project DZKR_TCL_TEST E:/Project/Test/TCL_TEST

创建完成后会自动打开如下图,一些未写的参数则会默认进行赋值,如下图中的红框所示,器件之类的都使用了默认参数:

如果你想要的是其他类型的工程,可以直接在命令TCL的命令窗口输入以下对应的命令,直接复制粘贴就可以实现工程类型转换。

• RTL Project

set_property DESIGN_MODE RTL [current_fileset]

• Netlist Project

set_property DESIGN_MODE GateLvl [current_fileset]

• I/O Planning Project

set_property DESIGN_MODE PinPlanning [current_fileset]

命令后面的参数我就不再多进行演示了,想要知道参数的更多说明,可以参考官方文件:UG835

关闭工程的话还可以直接在命令窗口输入:close_project

更改工程参数

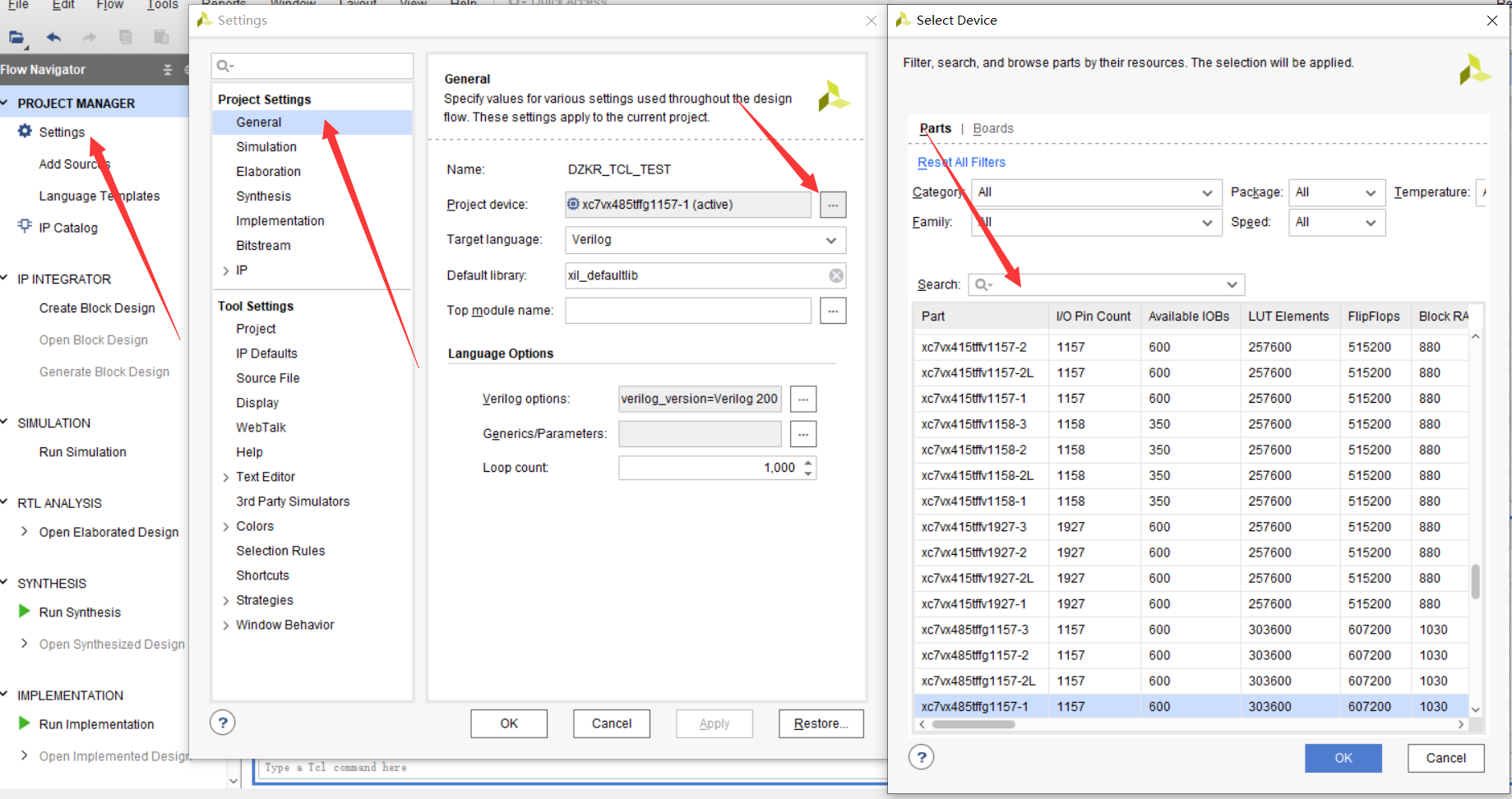

直接点击PROJECT MANAGER下面的Settings,对工程进行相关设置,下图进行了工程的目标器件进行修改举例:

在General中还可以更改工程使用的编程语言,设置顶层模块,Verilog标准的版本等等,此外还有仿真、综合、实现等信息的设置,默认的配置也足够实现一般的需要了。

结语

工程的相关就简单介绍到这了,下一篇【Vivado的那些事儿】打算弄下仿真,不过还没想好弄咋样的,所以可能还得要一段时间准备准备~

554

554

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?