1.1 Pmod DA3模块简介

本设计采用的DA模块为专用Pmod接口,16bits高精度串行DA,适配zynq7020开发板的Pmod接口,简单易用,但是需要编写相应的接口电路。

Pmod DA3的时序图:

具体参数和接口请参考Pmod DA3的使用手册

1.2 DA模块设计

接上一篇博客,新建一个设计文件:

模块命名为PmodDA:

将下列代码添加到PmodDA模块中,以便设计相应的电路接口(根据时序图编写):

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/04/26 20:01:33

// Design Name:

// Module Name: PmodDA

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module PmodDA(

input [15:0] DATA,

input DA_drdy,

input clk,

output reg _CS,

output reg DIN,

output reg _LDAC,

output SCLK

);

reg [4:0] counter=0;

reg clk_div_25M;

reg[1:0] _clk_div_25M;

always @(posedge clk)

if(counter==4) counter <= 0;

else counter <= counter+1;

always @(posedge clk)

if(counter<2) clk_div_25M <= 1;

else clk_div_25M <= 0;

assign SCLK=clk_div_25M;

//reg _CS=1;

//reg DIN;

//reg _LDAC;

reg[4:0] tempcounter=0;

reg[1:0] _drdy=0;

reg[15:0] temp;

reg[2:0] state=0;

parameter[2:0] Idle=0;

parameter[2:0] Start=1;

parameter[2:0] SendData=2;

parameter[2:0] LoadData=3;

always@(posedge clk)

_drdy <= {_drdy[0],DA_drdy};

always@(posedge clk)

_clk_div_25M <= {_clk_div_25M[0],clk_div_25M};

always@(posedge clk)

case(state)

Idle:

begin

_LDAC<=1 ;

_CS<=1;

if (_drdy == 2'b10)

begin // on negative edge

temp<=DATA;

DIN<=DATA[15];

state<=Start;

end

end

Start:

begin

if (_clk_div_25M == 2'b10)

begin // on negative edge

_CS<=0;

state<=SendData;

end

end

SendData:

begin

if (tempcounter!=16)

begin if (_clk_div_25M == 2'b01)

begin // on postive edge

tempcounter<=tempcounter+1;

temp<=temp<<1;

end

if (_clk_div_25M == 2'b10)

begin // on negative edge

DIN<=temp[15];

end

end

else

if (_clk_div_25M == 2'b10)

begin // on negative edge

_CS<=1;

tempcounter<=0;

state<=LoadData;

end

end

LoadData:

begin

if (_clk_div_25M == 2'b01)

begin // on postive edge

if(_LDAC==1)_LDAC<=0;

else

begin

_LDAC<=1;

state<=Idle;

end

end

end

endcase

endmodule

PmodDA模块的接口设计是为了与Pmod DA3连接,后面通过约束文件绑定相应端口,即可实现DA直插,无需连线,这也是FPGA设计电路的好处,根据需要设计相应接口。

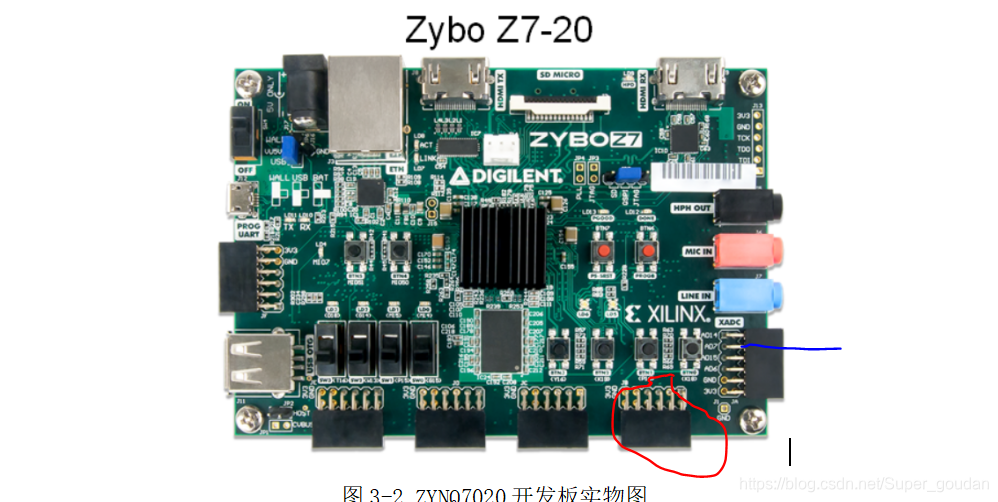

工程中的AdDA_top文件连接了片上XADC和Pmod DA3,可以下载到板上直接测试·,实现的功能是AD7端口输入信号,DA连接示波器与下图所示的开发板Pmod接口,在示波器上可以观察到输入的信号,具体测试流程为(其他测试流程可参考此流程,过程相似):

下图红圈所示为Pmod DA3与开发板连接点,直插上排接口即可,蓝线所示为AD7,信号驶入端口,上为AD7P,接信号红线,下为AD7N,接信号蓝线(此接线方式是按照工程中的端口约束文件连接)

约束文件(XDC文件)改成下面代码:

## This file is a general .xdc for the Zybo Z7 Rev. B

## It is compatible with the Zybo Z7-20 and Zybo Z7-10

## To use it in a project:

## - uncomment the lines corresponding to used pins

## - rename the used ports (in each line, after get_ports) according to the top level signal names in the project

# ports used: clk, led, ja

#Clock signal

set_property -dict {PACKAGE_PIN K17 IOSTANDARD LVCMOS33} [get_ports clk]

#create_clock -period 8.000 -name sys_clk_pin -waveform {0.000 4.000} -add [get_ports clk]

set_property -dict {PACKAGE_PIN L15 IOSTANDARD LVCMOS33} [get_ports AD7P]

set_property -dict {PACKAGE_PIN K16 IOSTANDARD LVCMOS33} [get_ports AD15P]

set_property -dict {PACKAGE_PIN L14 IOSTANDARD LVCMOS33} [get_ports AD7N]

set_property -dict {PACKAGE_PIN J16 IOSTANDARD LVCMOS33} [get_ports AD15N]

##Pmod Header JB (Zybo Z7-20 only)

set_property -dict {PACKAGE_PIN V8 IOSTANDARD LVCMOS33} [get_ports _CS]

set_property -dict {PACKAGE_PIN W8 IOSTANDARD LVCMOS33} [get_ports DIN]

set_property -dict {PACKAGE_PIN U7 IOSTANDARD LVCMOS33} [get_ports _LDAC]

set_property -dict {PACKAGE_PIN V7 IOSTANDARD LVCMOS33} [get_ports SCLK]

将该模块设置为顶层:

选中该模块,右键单击找到set as top ,点击即可(设置完成会出现一个小三角,表示此模块为顶层,综合,布线等操作只对此模块进行)

综合操作,下图红圈地方可以更改,我的电脑为八核,这可以提高软件运行速度,要查看电脑为几核请百度:

布线操作:

生成比特流:

完成后连接开发板,下载即可:

然后输入信号,可以在示波器上看到相应波形。

788

788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?