一、概述

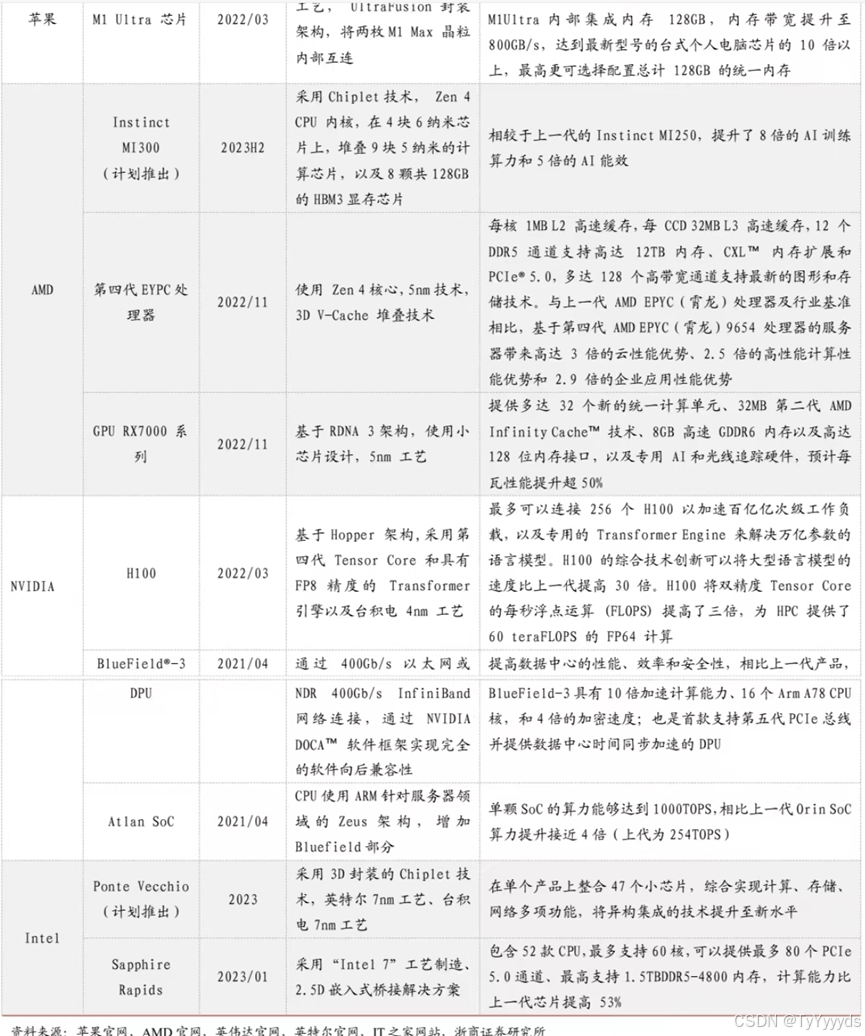

Chiplet技术最早报道于1996年IEEE会议,通过封装技术异质集成化合物半导体器件技术中。自2017年AMD采用Chiplet(小芯片、晶粒、芯粒)的EPYC服务器CPU取得成功之后,Chiplet重新获得了业界的持续关注。继AMD之后,Marvell、Intel、Nvidia、apple等多家公司也陆续展示或布局了Chiplet技术。

但并不是所有芯片都适合使用Chiplet,不少情况下单颗集成的系统芯片会更有价值。相较之下,AI芯片对于芯片的设计规模要求最高,且需整合高频宽记忆体,高速I/O、高速网络等模组。Chiplet架构一般采用3D集成方案,减小了芯片面积,扩展了空间,是对AI芯片最佳、最具经济效益的设计。

Chiplet也非常适合汽车自动驾驶芯片。由于汽车自动驾驶芯片对于算力要求非常高,芯片的面积很大,成本很高,车规级的认证周期又很长,采用Chiplet设计,不仅可以降低设计难度、提升良率、降低设计和制造成本,更为关键的是还能够提供更高的安全性和快速迭代。

高性能服务器/数据中心、自动驾驶、笔记本/台式电脑、高端智能手机等将在未来几年成为Chiplet的主要应用场景,引领该市场增长。

二、国外Chiplet历史与现状

2.1 AMD

2.1.1 EPYC(Naples)

从初代EPYC处理器所采用的Zen架构说起。Zen确立了该系列计算单元模块化的最小单位CCX(Core Complex,核芯复合体),每个CCX包括4个Zen核芯(Core),以及8 MiB共享L3 Cache,每核芯2 MiB。

AMD EPYC的模块化与NUMA之路 - 极术社区 - 连接开发者与智能计算生态

2.1.2 EPYC(zen2)

时隔两年之后,AMD推出基于Zen 2架构的第二代EPYC处理器,通过架构与制程一体优化,达到最高64核、256 MiB L3 Cache,分别是第一代EPYC的2倍和4倍,内存访问一致性和双路的扩展性也有不同程度的改善,终于获得了一众云服务提供商(CSP)的青睐。

2.2 苹果

2.2.1 采用台积电 CoWos-S 桥接工艺的 M1 Ultra 芯片

苹果 2022 年 3 月发布的 M1 Ultra 芯片采用了独特的 UltraFusion 芯片架构,借助台积电的 CoWos-S 技术,通过两枚 M1 Max 晶粒的内部互连,实现了性能的飞跃。M1 Ultra 在新架构下,晶体管数量达到 了 M1 的 7 倍多,同时两颗 Max 之间的互连频宽可达 2.5TB/s。M1 Ultra 内部集成内存 128GB,包含 8 个 16 层堆叠的 HBM(高带宽内存)堆栈的内存部件,核心传输速率达 3200M,实际传输带宽超过 800GB/s。这款产品实现了 Apple 芯片与 Mac 系列电脑的又一次重大飞跃,具有里程碑意义

苹果 M1 UltraFusion 芯片互连背后的技术--台积电CoWoS-S - 知乎

2.3 Intel

2.3.1全球首款基于UCIe连接的Chiplet(小芯片)处理器——代号为Meteor Lake的Intel Core Ultra处理器

Core Ultra 代表了英特尔客户端处理器路线图的一个转折点,因为它是第一个由 Foveros 封装技术(英特尔的3D封装技术)支持的客户端Chiplet设计,还采用了 EUV 光刻技术。从设计上看,芯片内部包含了computing tile、graphics tile和SoC tile和I/O tile四个部分。其中,computing tile是基于Intel 4工艺打造,graphics tile是基于台积电的5nm打造,SoC tile则采用台积电的6nm打造,这正是Chiplet精神的体现。值得一提的是,这个芯片的Soc tile上还集成了英特尔首个NPU。该芯片的couputing tile中有一对新的核心,一个名为 Redwood Cove 的 P 核心和一个名为 Crestmont 的新 E 核心。其中,新的 P 核心是英特尔第 12 代核心 (Raptor Lake) 处理器中之前的 Golden Cove 核心的直接继承者,通过新的 Redwood Cove 核心,英特尔在芯处理器上带来了不小的 IPC 提升。

英特尔展示全球首款基于UCIe连接的Chiplet CPU_腾讯新闻

2.3.2 Granite 和 Sierra

Granite 和 Sierra 可以被认为是解构的 Meteor Lake 处理器,Granite 配备 Redwood Cove P 核心,而 Sierra 配备 Crestmont E 核心。

Chiplet设计、性能240%提升,英特尔下一代数据中心CPU设计来了-腾讯云开发者社区-腾讯云

三、国内Chiplet历史与现状

3.1 华为海思

3.1.1 Hi16xx和晟腾910

华为海思是一家中国的半导体公司,主要生产芯片和系统解决方案,它是国内最早尝试Chiplet的厂商之一。2014年,华为海思与台积电合作的64位Arm架构服务器处理器Hi16xx,采用台积电异构CoWoS 3D IC封装工艺,将16nm逻辑芯片与28nm I/O芯片集成在一起,实现了具有成本效益的系统解决方案,可以视为早期Chiplet实践。

海思因为其属性,公开消息并不多。往往是因为合作伙伴,需要展示自己的技术突破,海思才被迫营业,站台示众。这个海思1616 就是这样挂在TSMC 的网站上的。

晟腾910 的8 个chiplet 设计,融合了HBM die,逻辑部分与I/O 部分分离,两个dummy die,超大总die size 等特点。也算是业界标杆性设计。

3.1.2 基于 Chiplet 技术的 7nm 鲲鹏 920 处理器

华为推出的鲲鹏 920 是业界领先的 ARM-based 处理器,该处理器采用 7nm 制造工艺,基于 ARM 架构 授权,由华为公司自主设计完成,通过优化分支预测算法、提升运算单元数量、改进内存子系统架构等 一系列微架构设计,大幅提高处理器性能。典型主频下,SPECint Benchmark 评分超过 930,超出业 界标杆 25%。同时,能效比优于业界标杆 30%。鲲鹏 920 以更低功耗为数据中心提供更强性能。该处 理器创建了相干缓存子系统以将多核集成到单个小芯片中,同时开发了专用并行小型 IO 块,以实现二 维封装解决方案的高带宽芯片间连接

3.2 芯原股份

除华为之外,国内其他诸多半导体公司也有了惊喜的进步。如芯原股份有望是业内首批推出商用Chiplet的公司,近年来一直致力于Chiplet技术和产业的推进。基于“IP芯片化,IP as a Chiplet”和“芯片平台化,Chiplet as a Platform”两大设计理念,芯原推出了基于Chiplet架构所设计的高端应用处理器平台,目前该平台12nm SoC版本已完成流片和验证,正在进行Chiplet版本的迭代。

3.3 芯动科技

在Chiplet领域已耕耘多年的芯动科技,推出的首款高性能服务器级显卡GPU“风华1号”就使用了Innolink Chiplet技术,将不同功能不同工艺制造的Chiplet进行模块化封装,成为一个异构集成芯片。Innolink是自主研发的Chiplet的标准通信协议,在摩尔定律趋近失效,先进工艺的成本高昂的市场状况下,开拓了新的技术路线,为高性能计算,5G,元宇宙,游戏,云服务等应用提供异构集成的基础连接技术。Innolink Chiplet具有自主知识产权,填补了国内的异构集成技术空白,打破了国外核心技术垄断,成功应用于国产GPU及其他高性能计算芯片,为国产高性能芯片的发展提供了一条新的道路。

2022年4月,芯动科技又率先推出国产自主研发物理层兼容UCIe标准的IP解决方案——Innolink™ Chiplet。据悉,这是国内首套跨工艺、跨封装的Chiplet(芯粒)连接解决方案,且已在先进工艺上量产验证成功。

同时,芯原Chiplet技术将助力设计自动驾驶和高性能计算解决方案

3.4 寒武纪

寒武纪在2021年11月发布了其第三代云端AI芯片思元370,基于7nm制程并且是其首款基于Chiplet技术的AI芯片,在一颗芯片中封装2颗AI计算芯粒(MLU-Die),每一个MLU-Die具备独立的AI计算单元、内存、IO以及MLU-Fabric控制和接口,通过MLU-Fabric保证两个MLU-Die间的高速通讯,可以通过不同MLU-Die组合规格多样化的产品,实现不同算力、内存和编解码器的组合。

寒武纪思元370采用2片相同的基于7nm 工艺的神经网络加速器芯片组合集成,实现性能翻倍。

附录:

1335

1335

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?