Chiplet基本知识点汇总

1. Wafer, die, chip, cell的区分

-

Wafer: 晶圆,指一整个晶圆硅片。

-

Die: 从晶圆上切分下来的小方格,一个晶圆上的每个die的设计内容都是一样的,重复单元。

-

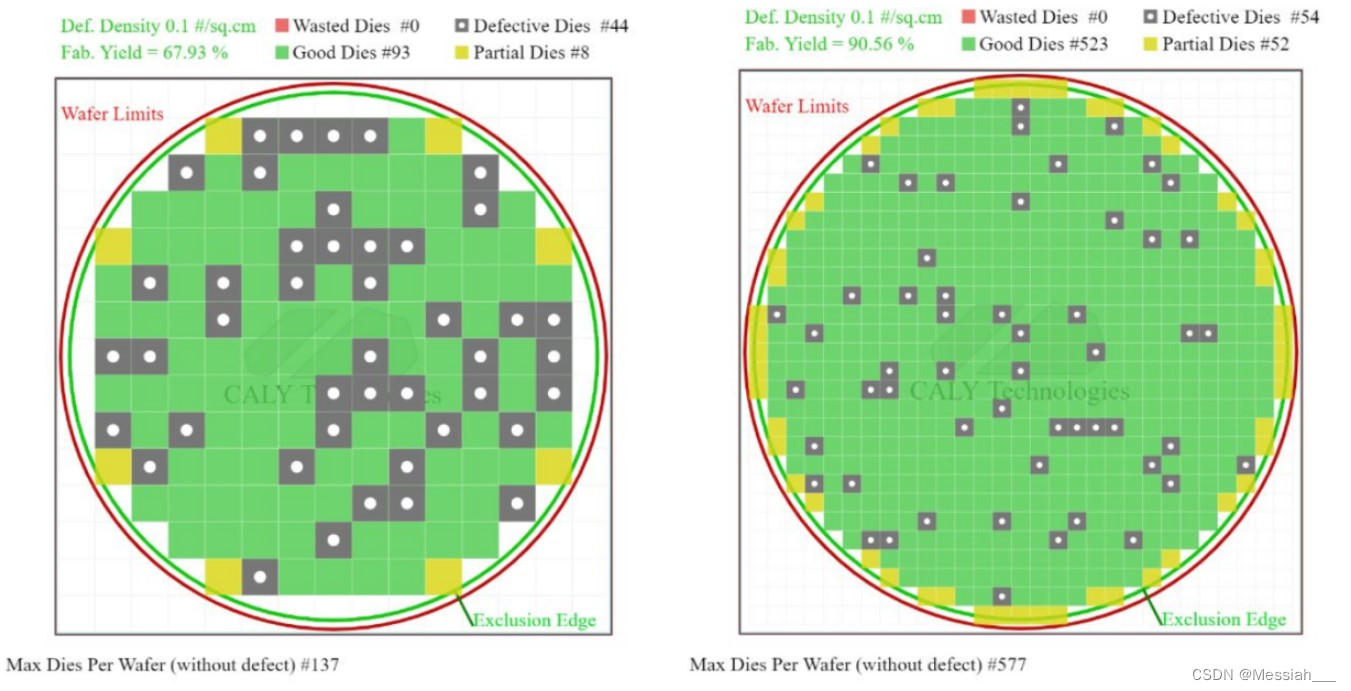

Die的大小会影响良率,Die越小,良率一般越高(不绝对)。

-

wafer本身会有制造的缺陷点,当Die很大的时候,大面积的Die都会因为缺陷点儿报废,当Die很小的时候,这种损耗就大大降低了。

-

-

Chip: 通常指集成电路,将多个电子元件集成到一块半导体材料上。

-

Cell: 是数字电路设计的标准单元,晶体管和连线组成,具有最基本的布尔逻辑或触发功能。

2. MCM, SiP, SoC, Chiplet的区别

1. IP核(Intellectual Property core)

- 早期的电路设计是全定制的,设计非常耗时。考虑到CPU有很多相似的模块,那能不能将这些相似的东西模块化,于是有了IP核。

- IP核是指芯片中具有独立功能的电路模块的成熟设计。六大核心处理器IP,分别为图形处理器(GPU)IP、神经网络处理器(NPU)IP、视频处理器(VPU)IP、数字信号处理器(DSP)IP、图像信号处理器(ISP)IP和显示处理器IP。

- IP核在EDA上有非常重要的地位。

- IP核可分为三类:

- 软核:verilog行为描述代码

- 固核:门级网表形式的代码

- 硬核:GDSII版图文件,不能修改

2. MCM(multi-chip module, MCM):一种封装技术,将多个芯片封装在一个模块中

- 多个裸片(die)和其它元器件组装在同一块多层高密度**互连基板/衬底(substrate)**上进行互连接, 然后进行封装。

- 特征是通过基板电路进行互连,比较可靠,但集成密度低。

- 相比于技术本身,MCM更多的表现了一种趋势和导向,比如芯片IP化、异构集成、异质集成等,这也是Chiplet的发展方向。

- Die to Die通过基板电路直接进行互连,比较可靠,成本较低,但集成密度低,latency相对较大。

1. 2D MCM-

多芯片模块(multi-chip module, MCM)技术的想法和商业用途已经存在了数十年。single-chip module单芯片模块

-

MCM采用逻辑上一个大型芯片或片上系统(SoC)的功能,然后将设计划分为多个较小的芯片。由于芯片尺寸和产率之间存在非线性关系,重新集成多个较小的芯片比构建单个SoC更具成本效益。

-

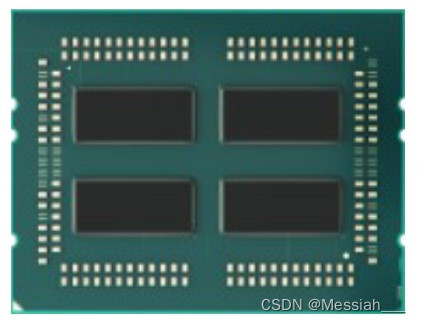

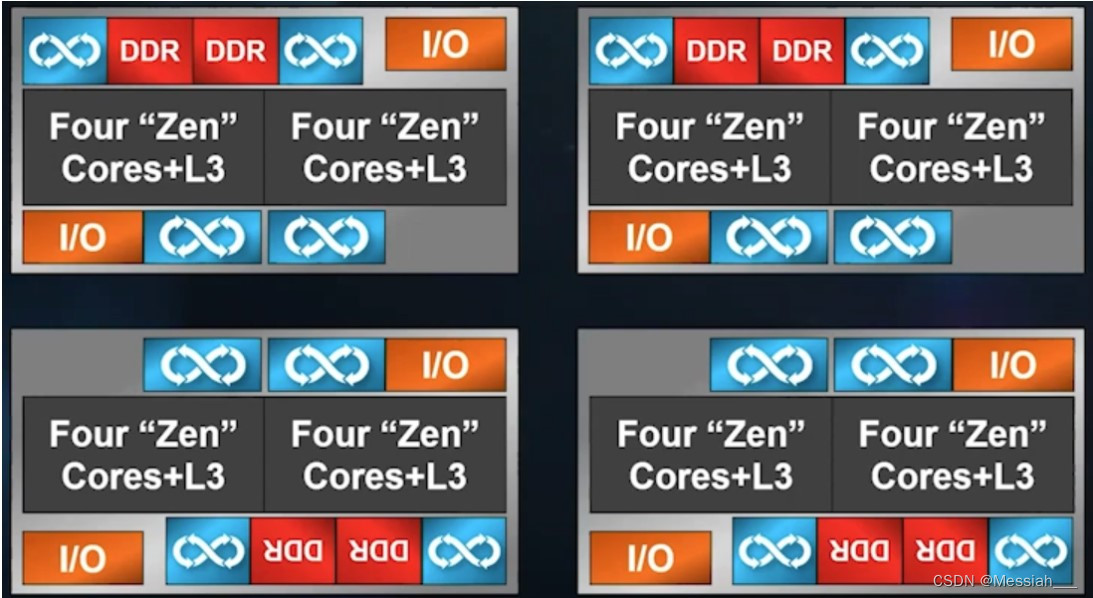

AMD EPYC(霄龙)处理器

- 32-core CPU 分成4个8-core die,这种设计要比单芯片的实现节省约40%的成本。

- 32-core CPU 分成4个8-core die,这种设计要比单芯片的实现节省约40%的成本。

-

die2die通信需要经过封装基板(substrate),与片上相比发送数据的带宽延迟和功耗较差。具有硬件中可以清晰划分并由软件管理的逻辑块的SoC可以减少此影响。

-

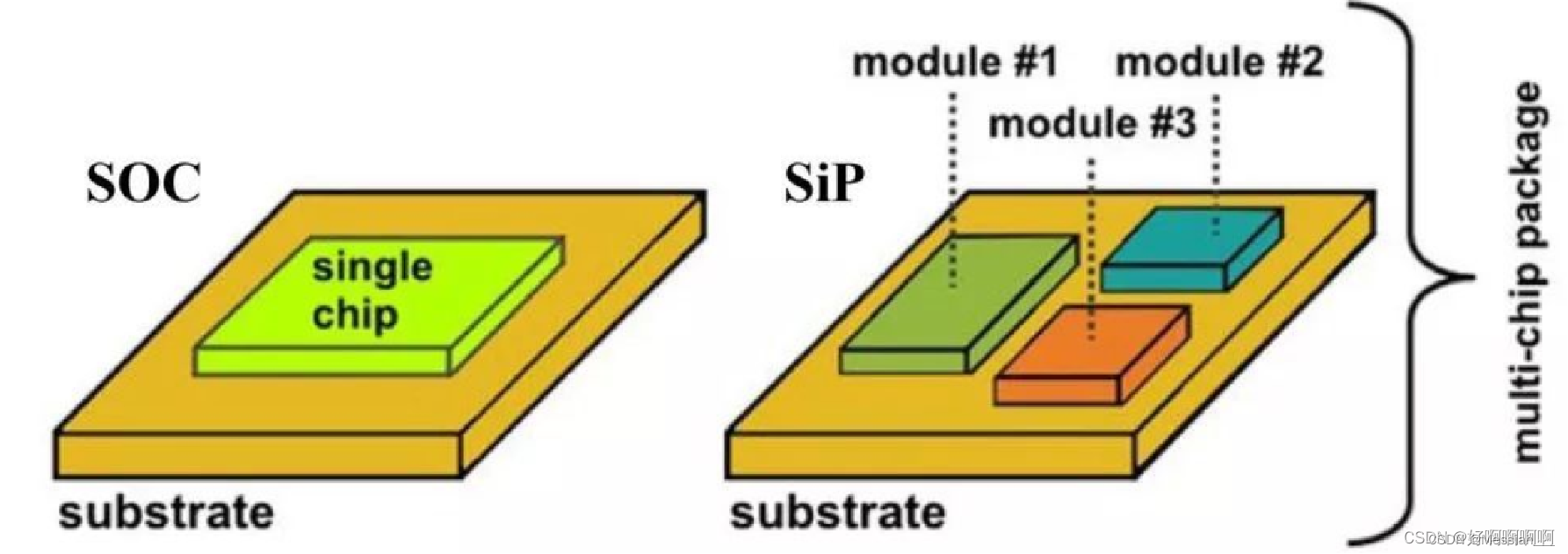

3. SiP(System in Package): 一种制造技术,将多个芯片集成到一个小型包装中

- SiP是MCM封装技术进一步发展的产物,即系统级封装,首先强调的是系统,其次是封装

- 对于某些 IP,无需自己做设计和生产,只需买别人实现好的硅片,然后在一个封装里集成起来,形成一个 SiP

- 在实现多芯片封装过程中,其目标是在适当扩展面积的基础上,尽可能实现同等功能的 SoC 芯片功能

- SiP能将处理器、存储器、传感器、射频收发器等部件搭载于同一个封装体内,形成一个系统或者子系统的封装技术

-

SoC(System on Chip): 片上系统,台式机的存储器、电源模块、功耗管理模块是分开的,而SoC是讲这些围绕CPU的关键模块集成在一个芯片上,笔记本手机上使用较多。

-

Chiplets

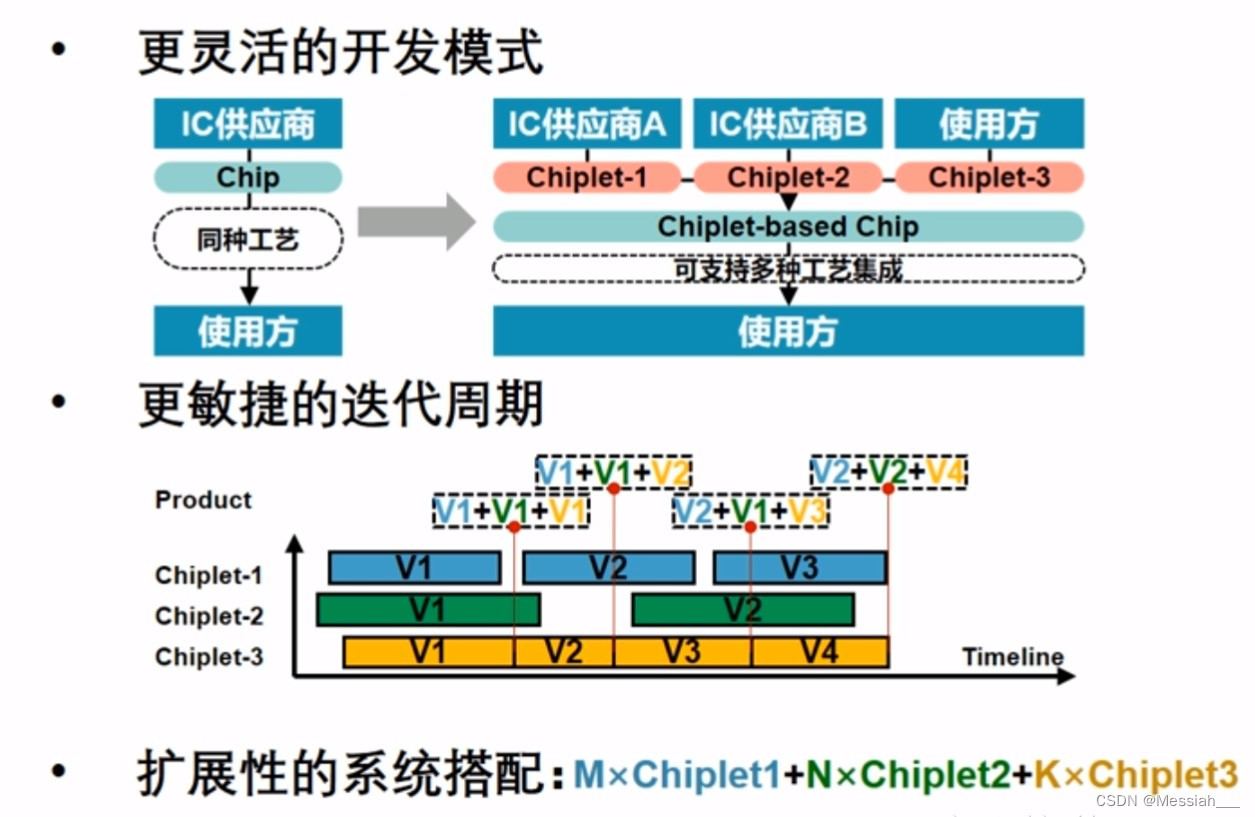

- Chiplet技术就是像搭积木一样,把一些预先生产好的实现特定功能的芯片裸片(die)通过先进的集成技术(比如3D integration)集成封装在一起形成一个系统芯片。而这些基本的裸片就是Chiplet。从这个意义上来说,Chiplet就是一个新的IP重用模式。

- 2D Chiplets

-

虽然经典的MCM将SoC划分为多个更小的且更具成本效益的组件,但AMD的chiplet方法更进一步,在不同工艺上实现不同的芯片,以更好地匹配每个chiplet的要求和约束。

-

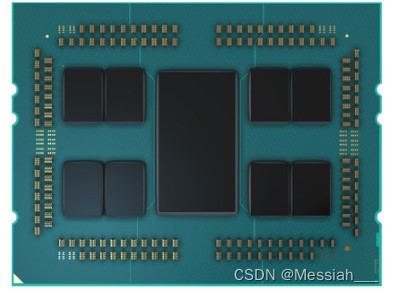

AMD 第二代 EPYC CPU,八个Chiplet都在7nm工艺下实现了8个CPU内核,中间较大的芯片是IO芯片,包含内存控制器,IO接口和其他系统组件。因为IO的迭代周期很长,使用先进技术节点的收益不大,因此IO Die使用较为成熟的、更具成本效益的技术节点12nm实现。

-

和MCM也面临同样的问题,chiplet之间的通信可能会受到基板级的路由限制,因此将SoC有效划分为Chiplet架构设计是非常重要的。

-

3. Chiplets的先进封装

1. 2.5 Silicon Interposer 硅中介层

-

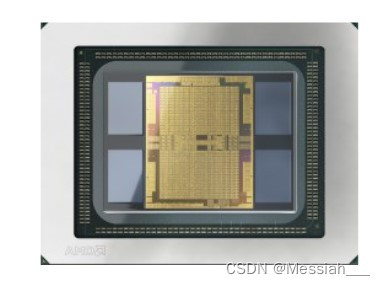

2D MCM和2D chiplet设计中封装基板上的芯片间通信链路通常限制在几十GB/s。主要限制是有机基板上可以实现的金属布线的宽度/密度。对于某些应用如将内存直接集成到封装中,无法提供100GB/s的带宽满足需求。

-

而silicon interposer硅中介层实质上是实现多个chip之间互连的一个芯片。

-

这通常称为2.5D堆叠,虽然芯片以三D的方式堆叠在中介层顶部,但各个芯片之间仍处于2D状态。

-

interposer可以在相对较小的区域内提供数百GB/s的带宽。硅中介层也可以通过TSV(through-silicon vias)来提供从各个芯片到封装外部IO、电源和接地连接。

-

如AMD Instinct MI100加速器,将基于GPU的计算芯片(较大的芯片)和四个封装内的DRAM模块相结合,全部堆叠在interposer上并进行互连,支持理论峰值带宽1.2TB/s.

2. 2.5 Silicon Bridges 硅桥

-

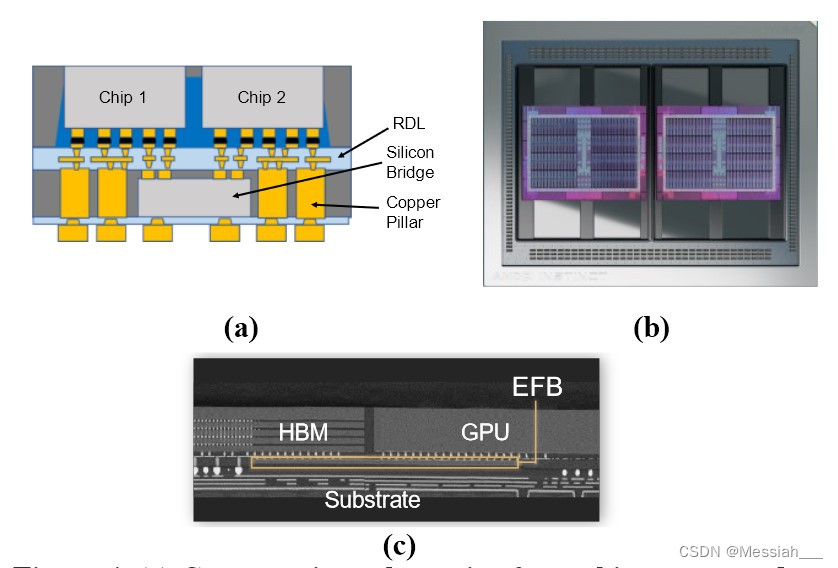

但中介层有一定的限制,中介层必须足够大以容纳要堆叠的所有的2.5D芯片。这样的非常大的中介层会增加系统的成本,如果甚至超过了掩膜版的限制(800-900mm^2),也会产生额外的成本去支持缝合技术以构建更大的interposer.

-

而硅桥可以替代interposer,去使用更小的硅片同时提供硅级别的导线密度。下图a展示了AMD的elevated fanout bridge高架扇出桥(EFB)技术的横截面图。

-

与硅中介层很类似但是硅桥要小的多,只需要覆盖连接在一起的两个芯片的连接接口即可。在硅桥占据的区域以外传统的铜柱技术copper pillar可以直接向芯片提供IO、电源和接地信号。同时也不需要额外制造TSV,更具成本效益。

-

图b显示了AMD Instinct MI200 加速器,由两个GPU大芯片和八个封装内内存模块。每个内存模块通过EFB连接到GPU芯片。图c也展示了EFB的横截面显微照片。

3. 3D Stacking: Microbumps

-

先前提到的技术将所有有源组件彼此相邻放置,而3D堆叠可以直接将一个或多个有源芯片彼此堆叠,进一步提高集成密度和芯片间带宽。

-

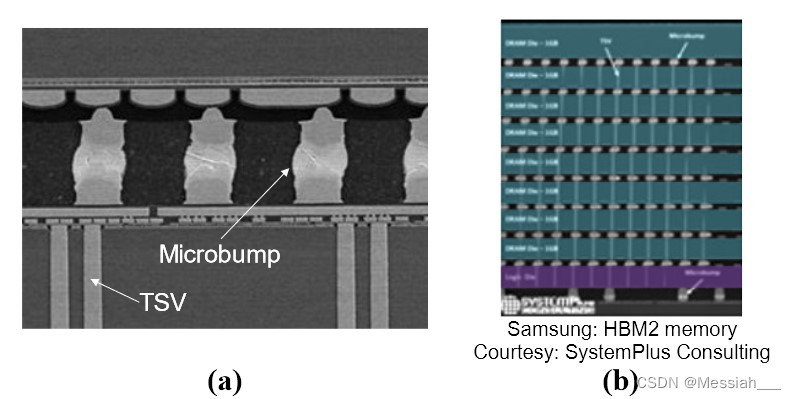

Microbumps 微凸块是非常小的焊接连接。图a显示了用微凸块连接连个该芯片的图片,可以重复堆叠构建具有多个管芯的堆叠,图b显示了一个3D内存堆栈,其中包含8层DRAM芯片,所有芯片均通过TSV和微凸块互连。

-

这样的连接大大增加了可以集成到给处理器封装区域的内存量。

-

但也有一定的问题:更高的热阻,额外高度,互连密度也受到微凸块尺寸限制,微凸块的尺寸和间距很难缩放到很小的尺寸。

4. 3D Stacking: Hybrid Bonding 混合键合

-

混合键合 最新的 3D 堆叠技术使用两相混合键合工艺。

-

芯片不是通过微凸块将两个芯片上的金属焊盘连接在一起,而是直接熔合在一起。第一阶段包括在两个芯片各自表面的氧化物之间形成共价键。第二阶段包括高温铜-铜接合工艺,使每个芯片上的金属焊盘直接熔合在一起。通过完全消除微凸块,混合键合可以支持更高的互连密度(例如,从微凸块的数十微米间距到混合键合的个位数微米)

-

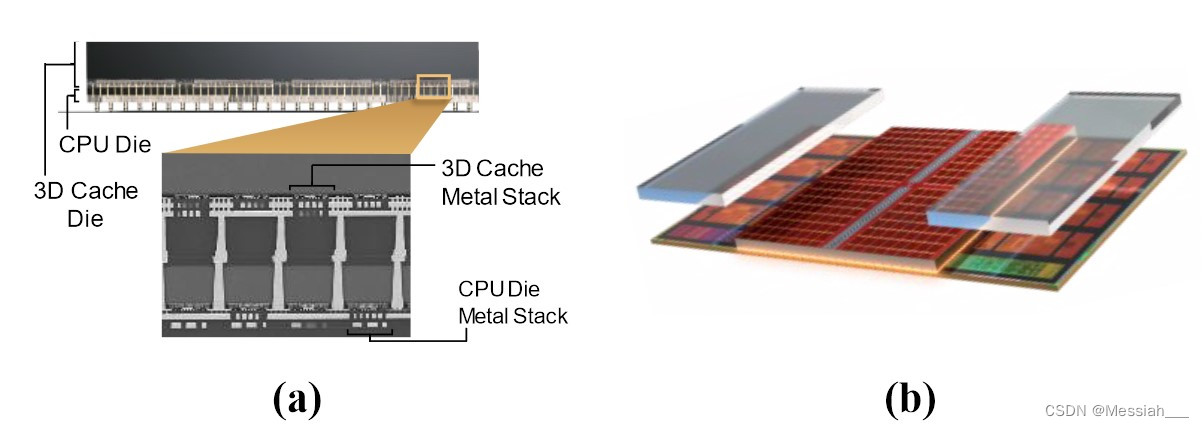

图a显示了混合粘合在 CPU 芯片顶部的高速缓存芯片的横截面图。底部芯片上的 TSV 连接到混合键合界面处的金属键合焊盘。顶部芯片上的接合焊盘通过接合焊盘通孔连接到顶部高速缓存芯片的普通金属堆叠。图b显示了 AMD V-CacheTM 技术的图形渲染,该技术将缓存芯片堆叠在 CPU 小芯片之上。这使得能够在全带宽下将 CPU 的 L3 缓存容量增加三倍。

-

在此实现中,额外的无源填充硅(如图中浮动的灰色块所示)堆叠在 CPU 计算逻辑的顶部,以帮助将热量从处理器管道传导到封装的冷却解决方案(未显示)。与基于微凸块的 3D 堆叠相比,没有微凸块或底部填充的直接芯片间接口提供了优越的散热路径。

4. Chiplet发展阶段

-

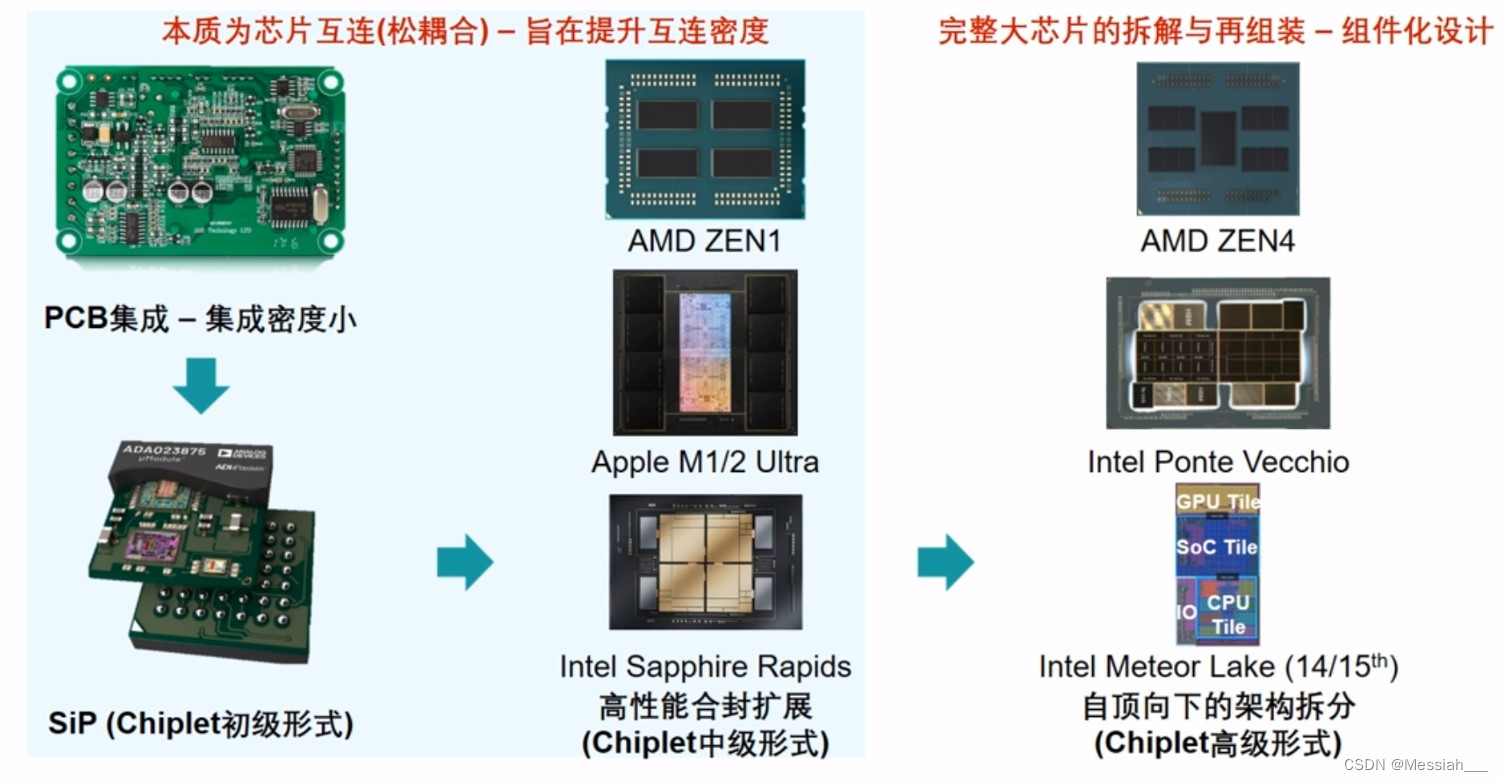

具体来说,chiplet的发展阶段可分为三个:

- Chiplet初级形式:SiP。可以基于已经封好的芯片、也可以基于裸片去做封装,可以更加紧凑,比较简单,互连可能也只是一些低速IO

- Chiplet中级形式:高性能合封扩展。同构的方式实现更好的良率和芯片,提供一定的扩展性。

- Chiplet高级形式:自顶向下的架构拆分:完整大芯片的拆解和组装,之前的工作都是同构扩展,而高级形式可以使用不同的技术节点的Die, 异构的一些Die进行组装,提供更好的一个性价比。那么就可以在完整大芯片的基础上进行异构的拆分,不同组件使用不同的技术节点。

-

Chiplet的拆分、互连、封装三个阶段 拆拼封的优势:

References:

[1] G. H. Loh and R. Swaminathan, “The Next Era for Chiplet Innovation,” in 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium: IEEE, Apr. 2023, pp. 1–6. doi: 10.23919/DATE56975.2023.10137172.

本文详细介绍了Chiplet技术的基础知识,包括Wafer、die、chip和cell的区别,以及MCM、SiP、SoC和Chiplet的不同。文章还探讨了Chiplet的先进封装技术,如SiliconInterposer、SiliconBridge和3DStacking,以及AMDEPYC等实例。最后,概述了Chiplet的发展阶段及其优势。

本文详细介绍了Chiplet技术的基础知识,包括Wafer、die、chip和cell的区别,以及MCM、SiP、SoC和Chiplet的不同。文章还探讨了Chiplet的先进封装技术,如SiliconInterposer、SiliconBridge和3DStacking,以及AMDEPYC等实例。最后,概述了Chiplet的发展阶段及其优势。

293

293

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?