一、逻辑代数基础

- 卡诺图基本原则

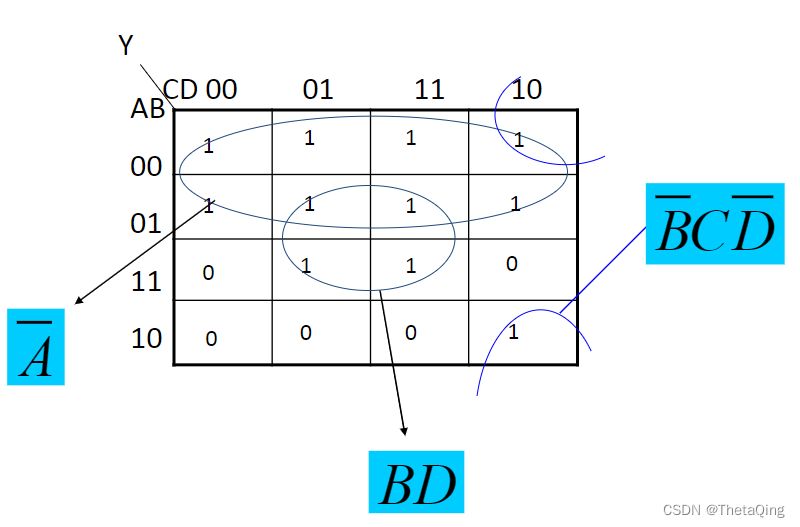

(1)若两个最小项相邻,可合并为一项消去一对不同因子;

(2)若四个最小项相邻,可合并为一项消去两对不同因子;

(3)若八个最小项相邻,可合并为一项消去三对不同因子;

注意:最小项是乘积项,最大项是和的形式;卡诺图中如果只有三个项,则高一位,低两位;排列顺序是00 01 11 10,最小项的序号从左到右依次是m0 m1 m3 m2

- 逻辑函数的表示方法有哪几种?它们之间如何转换?

逻辑函数的表达方式有四种,分别是逻辑函数式、逻辑真值表、逻辑图、卡诺图。

- 逻辑函数式转换为真值表,首先需要将输入逻辑变量的组成情况按顺序写出,再一一判断输出逻辑变量。

- 真值表转换为函数式,首先要把输出逻辑变量为1的情况标出,再看对应的输入逻辑变量——1对应原变量,0对应反变量,每一组组内变量相乘,组外相加。

- 其它方式转换为逻辑图,最好统一转换为函数式,再根据函数式的情况分类画图,最后统一起来。 其它方式转换为卡诺图

二、逻辑门电路

- 试说明在vi1接高电平(3.4V)的情况下,用万用电表测量图2.1的vi2端得到的电压为多少?图中的与非门为74系列的TTL电路,万用电表使用5V量程,内阻为20kΩ/V。(1.4V)

- 由TTL反相器的电压传输特性可知,其阈值电压VTH是( 1.4 )V左右。

- OC门(集电极开路门):当输入有低电平时,可认为此时门的输出端为高阻状态。

- TS门(三态门):除了高低电平之外,还有第三个状态。

- OC门主要用于线与:

下图所示电路Y输出为:

- CMOS门电路在外部特性上与TTL门电路有哪些区别?

电源范围更宽,更低功耗,抗干扰能力更强,连接方便

三、组合逻辑电路

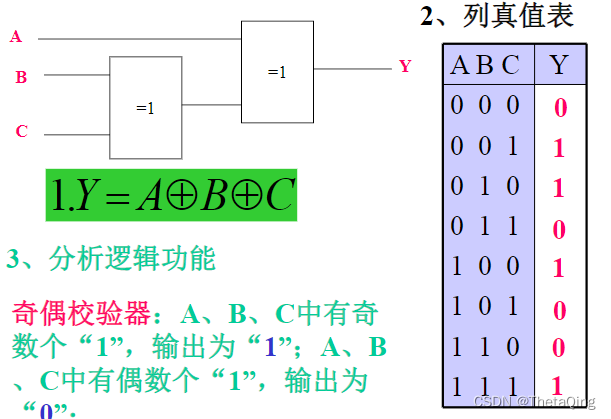

- 奇偶校验器

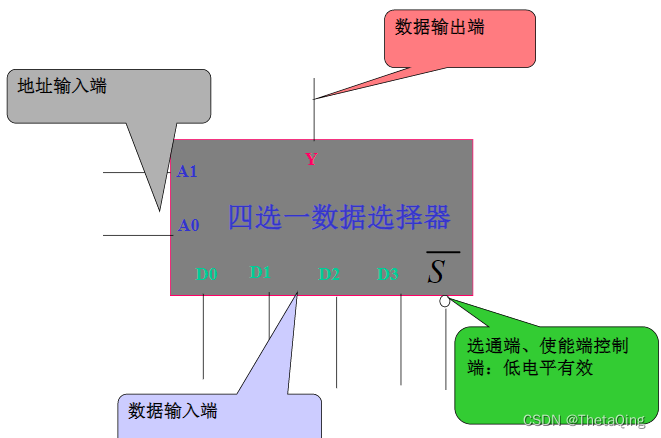

- 数据选择器

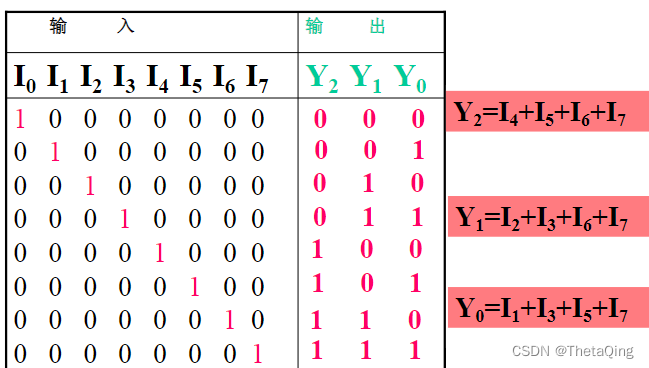

- 编码器:将不同的事物用二进制代码表示的电路。

(1)普通编码器:任何时刻只允许一个输入信号有效,否则输出将会发生混乱。

图为高电平有效的8线-3线普通编码器功能表

(2)优先编码器:在优先编码器中,对每一位输入都设置了优先权,因此允许两位以上的输入信号同时有效,但优先编码器只对优先级较高的输入进行编码,从而保证编码器工作的可靠性。

图为高电平有效的8线-3线优先编码器功能表,I7优先级最高,I0优先级最低

(3)74LS148

低电平有效的。

~S为选通输入端,当~S=1时,所有的输出端均被封锁在高电平;只有在~S=0时,编码器才能正常工作。~Ys为选通输出端,当~S=0,~Ys=0时,表示电路工作,但无编码输入。~Yex为拓展段,当且~S=0,~Yex=0时,表示电路工作,而且有编码输入。- 表中

~I7的优先权最高,~I0的优先级最低,注意编码也是取的反码

- 译码器:将二进制代码译成对应输出的高、低电平信号的电路,称为译码器。

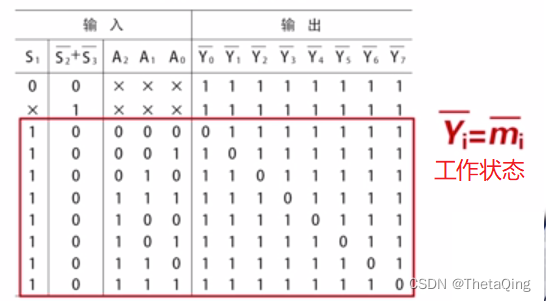

74LS138

S1, ~S2, ~S3为片选输入端,控制多片连接,拓展功能。- 当

S1=1, ~S2+~S3=0时,译码器工作,否则译码器被禁止,所有的输出端被封锁在高电平。- 输出取

反码

3线-8线译码器辅以门电路后,更适用于实现3输入多输出的组合逻辑函数,因为它的每个输出都对应输入3位代码的最小项的非</

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5639

5639

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?