1)加法器1:

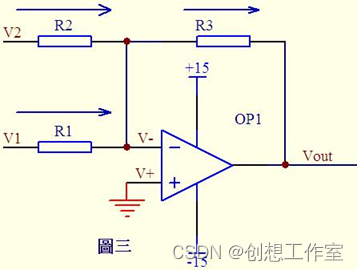

图3

图三中,由虚短知: V- = V+ = 0 ……a

由虚断及基尔霍夫定律知,通过R2与R1的电流之和等于通过R3的电流,故 (V1 – V-)/R1 + (V2 – V-)/R2 = (V- –Vout)/R3 ……b

代入a式,b式变为V1/R1 + V2/R2 = Vout/R3 如果取R1=R2=R3,则上式变为-Vout=V1+V2,这就是传说中的加法器了。

1)加法器2:

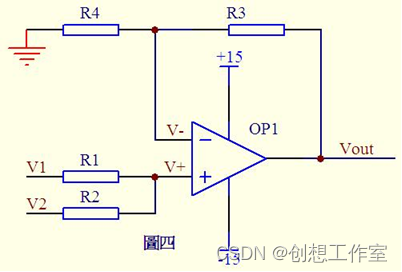

图4

请看图四。因为虚断,运放同向端没有电流流过,则流过R1和R2的电流相等,同理流过R4和R3的电流也相等。

故 (V1 – V+)/R1 = (V+ - V2)/R2 ……a

(Vout – V-)/R3 = V-/R4 ……b

由虚短知: V+ = V- ……c 如果R1=R2,R3=R4,则由以上式子可以推导出 V+ = (V1 + V2)/2 V- = Vout/2 故 Vout = V1 + V2 也是一个加法器,呵呵!

文章介绍了两种使用运算放大器(运放)构建的加法器电路,分别通过虚短和虚断原理分析了电流关系,当特定电阻相等时,电路实现信号的加法功能。

文章介绍了两种使用运算放大器(运放)构建的加法器电路,分别通过虚短和虚断原理分析了电流关系,当特定电阻相等时,电路实现信号的加法功能。

1238

1238

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?