摘要:本文在AutoCAD平台的基础上对常用光学镜头基本结构进行参数化和模块化自动设计。根据光学系统外形尺寸可以一次性设计出结构装配图,而且可以从装配图方便地分离零件图。同时还提供了多种结构形式供设计者选择。

关键词:计算机辅助设计;光学镜头;结构

一、引言

计算机辅助设计技术早已应用到镜头的光学设计当中,镜头的结构设计也有一些计算机辅助设计软件,是由于结构设计的多样性或专业性强或要昂贵平台支持而使用不便。光学镜头的结构设计要求各个光学零件准确定位和合理固定,保证镜头的光学性能。对于照相物镜、显微物镜、望远物镜、目镜等大多数非变焦、光轴成直线的镜头来说,其基本结构由透镜、压圈、镜筒、隔圈组成。只要对这些结构作自动设计,就能省去许多费事的构思和繁琐的计算。以自动设计得到基本结构为基础,就不难修改成为所要求的特殊结构,例如镜筒与机壳的专用连接结构。本文介绍的光学镜头基本结构计算机辅助设计是基于广泛应用的AutoCAD平台和采用人机交互式操作,用AutoLISP语言进行参数化和模块化设计,通用性好且简单易行。

二、镜头结构分类

常用光学镜头诸如望远物镜、显微物镜、照相物镜和目镜,基本结构包括四个部分:透镜、隔圈、镜筒、压圈。

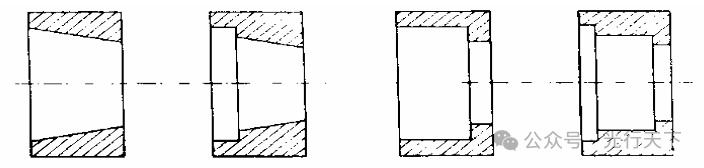

隔圈结构类型比较多,它受前后透镜直径和通光孔径的大小差别影响较大,也受其它结构要素影响。隔圈结构类型如图1所示。

图1

镜筒结构大体可以分为两类:直筒式和台阶式。

压圈的结构形式包括外螺纹压圈和内螺纹压圈,在实际应用中大多采用外螺纹压圈,因此本文仅考虑外螺纹压圈,又根据光学系统对边缘光线是否扩散和外观要求的不同,压圈可以分成三种形式。

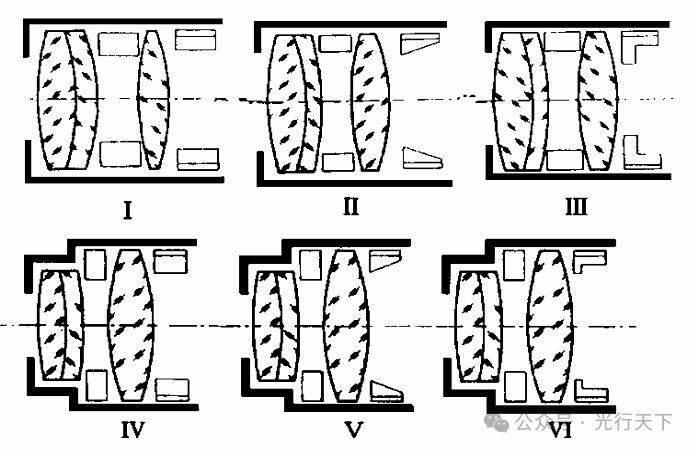

仅以镜筒和压圈的结构形式组合(暂考虑隔圈一种形式)就可以把镜头结构分为如图2所示的六种形式。

本文所述CAD的方法是用户根据镜筒和压圈分类的图标菜单来选择结构形式,再通过文字提示用户去决定选择何种隔圈形式。

三、总体设计

把镜头基本结构分成了六种类型,就可以把整个软件系统设计成六个主程序来分别完成六种类型结构的设计。首先让用户输入光学系统外形尺寸,然后选择:只画光学系统图或画六种类型中一种类型结构图。每个主程序要调用光学系统、压圈、镜筒、隔圈的子程序完成整个光学镜头装配图绘制和自动设计。软件系统框图如图 3所示。

图2

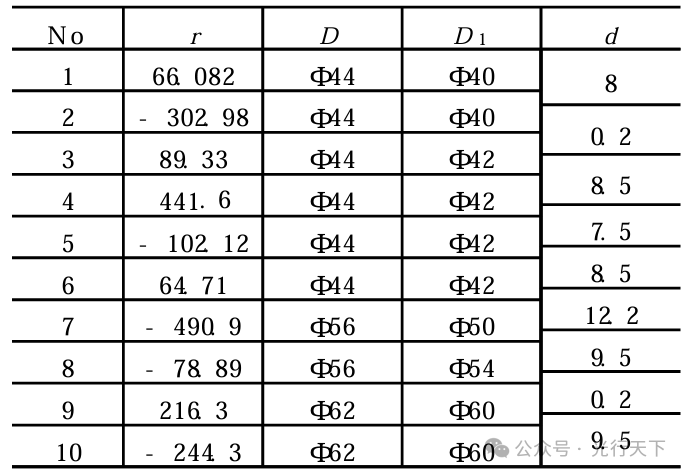

六、镜头设计实例

表2是设计好的光学系统外形尺寸,也是本实例结构设计的已知原始数据。图6是应用本文所述的程序,选择某种结构形式,设计出来的镜头装配图,图中没有作任何修改(图中是在拆零件图之前零件线条存在重叠现象,拆完零件后可以用一程序消除)。

表2

七、结论

(1)对于任意一组常用光学镜头,在已知其光学系统外形尺寸的情况下,可以迅速地绘制出其固紧结构图,并能保证各光学零件定位的准确性。

(2)可以根据用户的需要提供多种结构式样以供选择,并且由装配图可以迅速分离出准确尺寸的零件图,提高了光学镜头的设计质量和设计效率。

(3)本软件比较容易进一步扩充与完善。例如可以更细致地考虑透镜工艺倒角对装配图的影响;可以运用程序进一步完善零件图的尺寸标注等。

文章转自:光行天下

声明:鉴于篇幅,本文仅为节选,转载此文目的在于传递更多信息,仅供读者学习、交流之目的。文章版权归原作者所有,如有侵权,请联系删除。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?