说在开头:关于科学是什么(4)

有一次上课,波普尔对学生说:“拿起你们的的笔和纸,仔细观察,然后记下观察的结果。”结果学生们手足无措,不知道该写什么,也不知道老师让他们观测什么。于是波普尔接着说:我们在开始“观察”经验之前,不可能不带着目的。人在开始观察之前,一定要先有一个目的,有一个明确的任务才能开始开始观察;所以波普尔认为:先有观察后有理论是错的,应该是先有理论(先提出问题、设定目标),再有观察。那这又说明什么呢?

科学研究最基础的一个问题,一切自然科学都要遵守的一个前提:全宇宙一定会遵守相同的物理定律(空间平移对称性);即,在地球上的物理规律,对于遥远宇宙另一端的恒星也同样适用。可是这凭什么?波普尔说,我们并不能证明世界上存在普遍的规律,但是人类为了生存,为了便于使用理论,必须在各种混乱的经验中总结出规律来。即,人们总是带着“总结规律”的目的去观察和总结经验的,因而发现了各种普适的规律。

我们换句话来说:为什么宇宙中存在普适的物理规律呢?因为人类需要,这样人类改造自然才方便!原来科学也只是一个用来描述世界的工具,科学家们并没有一本“科学真理审批手册”,并没有什么固定的程序来决定哪个理论更正确;而更像是去市场采购的的大妈,看着小贩摊位上各类假说叽叽喳喳,挑挑这个够不够精确,那个够不够简洁,最后商量出一个大伙最能接受的假说“买”下来。没有一点追求真理的神圣劲儿。

如此,科学只是描述世界的其中一个工具,那么其它的理论:宗教、巫术等等其它理论也是描述世界的工具。凭什么科学就要以自己的标准去衡量别人?只要人家不符合“科学”就说人家是错误和荒谬的呢?那科学还不符合巫术,为什么科学就不是荒谬的呢。

那么我们就可以不相信科学了么?去信其它的神魔?虽然我们不能将科学作为作为衡量一切理论的标准,但仍旧是有标准可用的。我们有两个原则必须坚持:经验主义原则(眼见为实,拿出大家都承认的证据)和实用主义原则(有实用价值)。假如有一个理论认为自己比现有的科学理论更优秀,那么就应该拿出可以检验的证据来。比如民间医术/偏方,那就要拿出证据来,证明在某些方面比现代医学更能有效的治愈病人。

所以我们不能说某个理论“不符合科学理论”,就认为它是错的。但假如我们认为“科学方法”是指“以经验主义为标准,以实用主义为目标,允许别人检验,反对独断论”的话,那么我们就应该相信科学。就可以说:如果某个理论的论证过程“不符合科学方法”,那么它就是不可信的。

我们要反对一切迷信,同样也不能对科学迷信:只相信科学而拒绝除此之外的所有理论,认为科学就代表了终极真理(唯科学主义),不承认科学的局限性,认为不能证伪的观点就是错的。但是如果我们在承认科学局限性的前提下,仍旧相信科学的结论,那就不应该叫迷信,因为科学不仅是可以证伪,而且还在于对它的检验是开放的。科学理论的语言基于严谨的逻辑,任何人只要花时间,都能够读得懂(相对应的,一些学说则需要自己领悟),科学没有权威,任何人只要有技术条件,都可以去证伪、推翻最权威科学家的理论。因为这些原因,科学虽然有局限性,但比其它不允许质疑的理论,还是要更“不迷信”一点。(参考自:林欣浩-哲学家们都干了些什么)

一,PCI总线概述

PCI总线,这是啥玩意呢?现在大部分人只知道这货是PCIe总线的前身,这个已被淘汰了十多年的总线,为什么还要拿出来讲呢?

记得那是12年的时候,Intel出了最后一代支持PCI总线的X86(似乎是Ivy Bridge),我还为之焦虑了一阵;因为在我们的硬件方案中X86与CPLD是通过PCI总线连接的(更早之前用的 Motorola(Freescale的前身)PowerPC CPU是用Local Bus扩展的),如果只剩下了PCIe接口,而CPLD又不支持PCIe,那只能自己硬着头皮写一个LPC总线的CPLD接口来实现(最后自己还真用Verilog写了一个LPC接口)。

当年CPLD代码中用的PCI接口模块是部门共用模块,但如果CPLD逻辑出问题了,还是得自己定位,没办法只能一边看代码,一边看PCI总线协议的内容,把这部分协议了解个7788;过了几年又参与到了NVME(PCIe3.0接口固态硬盘)项目中去,这次PCIe应用就复杂的太多,各种各样稀奇古怪的问题频出:兼容性的、热插拔的、丢包的、协商出错的……;Intel这个商用标准的协议,要搞出工业标准要求的可靠性应用,难度真的不小,不过那又是另外一个故事了。

废话了这么多,其实我想说的是:PCI总线和PCIe总线除了物理形态不一样之外,但从软件层面看来两者是一样的;PCIe总线协议是兼容PCI总线协议的,我们可以通过对PCI总线的学习,就更能理解PCIe总线协议。

好,老规矩,咱们从它的历史开始说起。

1,PCI总线历史

PCI总线:Peripheral Component Interconnect; PCI总线也属于局部总线(Local Bus)的一种,当然从它的名字中,我们也可以知道它是系统总线的延伸,用于连接CPU与外围组件。随着CPU性能的提升,如上一章所述ISA总线先是被LPC总线替代,现在又被eSPI总线所替代;PCI总线的出现也是淘汰了EISA(Extended Industry Standard Architecture)、VESA(Video Electronics Standards Association)等32位的总线,从那时起它便一直占据了处理器体系结构中的重要地位。

——我习惯称Local Bus是地址/数据信号分离的局部总线(已灭迹好多年),虽然PCI总线也属于Local Bus的一种。

那么PCI总线有怎样的魅力,能在快速发展的处理器体系结构中经久不衰呢?而与它同时代的局部总线却早已被淹没在时代的洪流之下了。这就不得不说到“投胎”的技术了:PCI总线规范由Intel的IAL(Intel Architecture Lab)提出,并在1992年正式发布V1.0版本;那么IAL是个啥组织?它是Intel的一个重要实验室,提出了:USB,AGP(Accelerated Graphics Port,替代了VESA总线),PCIe总线规范;甚至连X86的南北桥结构也是由它提出的。

到了1996年, PCISIG(PCI Special Interest Group)陆续发布了PCI总线V2.2,V2.3规范,而PCI总线规范最终定个在V3.0版本。除了PCI总线规范本身之外,PCISIG还定义了与PCI总线相关的规范:PCMCIA(Personal Computer Memory Card International Association)规范、MiniPCI规范,PCI-to-PCI桥规范、PCI电源管理规范、PCI热插拔规范以及CompactPCI总线规范。

——PCI-to-PCI桥规范是理解PCI体系结构的基础,CompactPCI规范用于背板结构大型系统,支持热插拔(当年进公司后做的第一个项目就是类似CPCI架构的设备,然后是ATCA架构(mTCA)的设备)。

PCI总线规范这么多年来取得了巨大的成功,虽然规范中有很多内容是基于Intel架构的X86处理器,但是在其它处理器系统上也有着非常广泛的应用,大多数处理器系统优选使用PCI/PCIe总线来连接外设。随着处理器技术的快速发展,PCI和PCI-X总线遇到了瓶颈,单端并行数据传输方式,限制了总线频率的进一步提升,所以高速串行总线逐步替代了并行总线,而PCIe总线最终替代了PCI总线成为主流。

——不考虑并行数据信号复杂度、功耗以及所占PCB面积等的问题,为什么单端并行数据传输模式的数据速率会受到限制呢?我们知道数据传输需要有时钟来采样,必须要有建立时间(ts)和保持时间(th),如果有64根数据线要实现高速同步传输,就必须要求时钟信号与64根信号线保持精确等长,走线路径环境(PCB板材、过孔以及连接器等)相同,还不能受到串扰等等(看过《信号完整性基础》这章内容的胖友们应该就知道,这是非常困难的),所以实现起来难度非常高;但是为什么DDR总线却可以呢?现在DDR5的速率可以支持到6.4Gbps,它为什么能这么牛B的单端并行传输?有兴趣的胖友们,可以思考下这个问题,DDR总线是如何解决这些问题的。

2,PCI总线结构

PCI总线相比于前面介绍的IIC,SPI,LPC以及eSPI总线都复杂了太多,这是一个很大的系统(记得当年刚工作时,学习TCP/IP协议红宝书,看的昏天暗地的,根本就看不懂,好不容易理解了的一点东西也早已忘光),因为它是处理器连接外部设备的主要总线,可以实现管理或业务的功能。

如下图展示了一个基于PCI总线的老系统结构。该系统包括一个北桥(North Bridge,位于中央PCI总线的北方向),北桥是处理器与PCI总线之间的接口。与北桥相连的是处理器总线(processor bus)、系统存储总线(system memory bus)、AGP图像总线(AGP graphics bus),以及PCI总线。这些设备共享PCI总线,它们要么直接与总线相连,要么作为插卡插入到连接器上。在中央PCI总线的“南方”有一个南桥(South Bridge),它用于将PCI与系统外设相连接,这里的系统外设可以是为了使用旧的遗留设备而应用发展了多年的ISA总线。南桥通常也是PCI的中心资源区(central resource),它提供了一些系统信号诸如复位、参考时钟和错误报告操作。

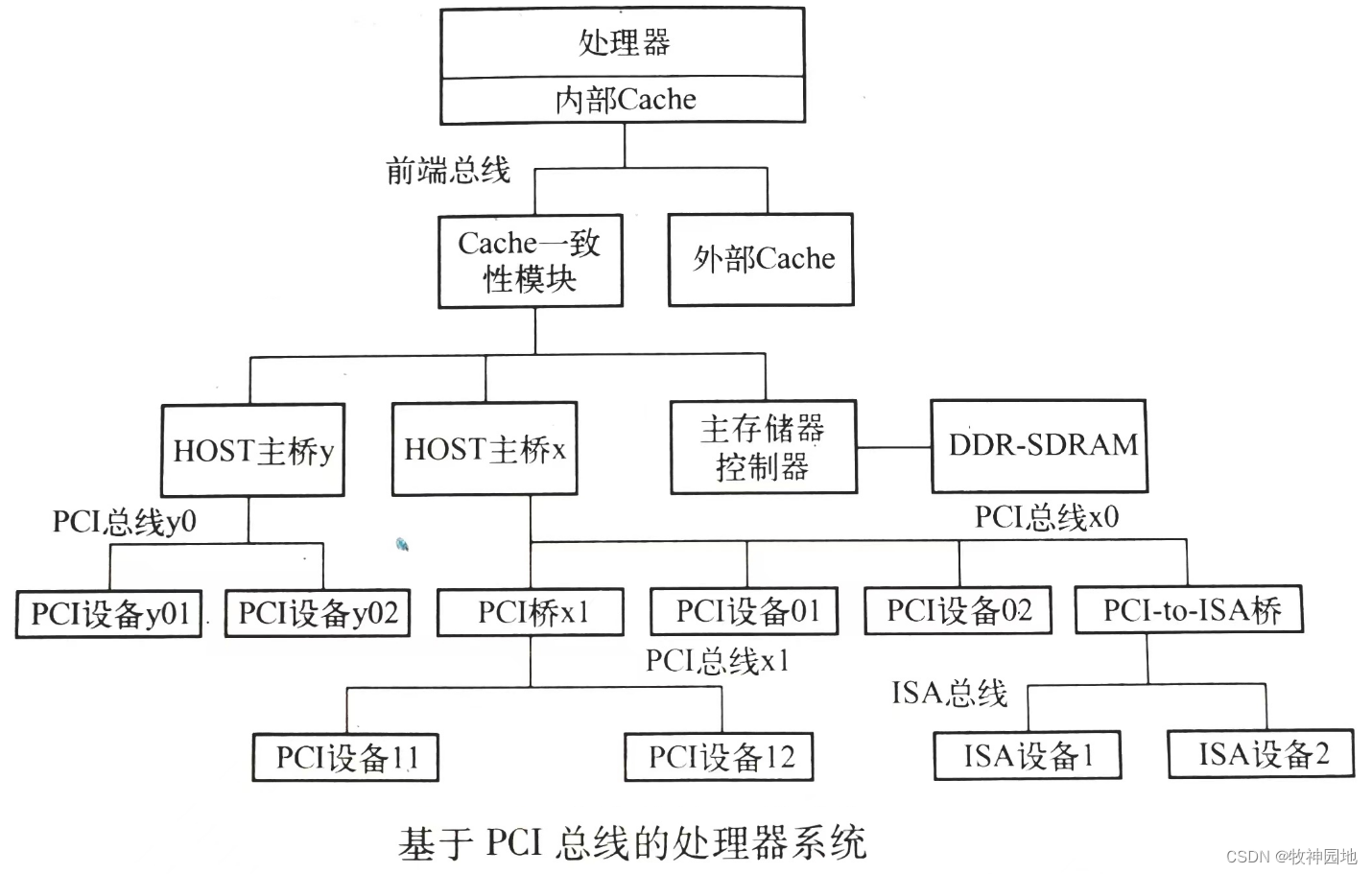

我们知道PCI总线与处理器总线(FSB)以及存储总线(DDR)三者是相互分离的。如下图所示,PCI总线作为处理器系统的局部总线,是处理器系统的一个组成部分。

PCI总线相关的模块包括了:HOST主桥,PCI总线,PCI桥以及PCI设备。

1. 处理器与PCI设备之间的数据通信,需要先经过HOST主桥进行地址转换(翻译);

2. 处理器系统可能含有多个HOST主桥,那么不同HOST主桥下的PCI设备通信需要经过两个HOST主桥;

3. HOST主桥与主存储器控制器在同一级总线上,因此PCI设备可以直接通过HOST主桥访问主存储器(DMA:Direct Memory Access);

4. PCI设备的DMA操作需要与处理器的Cache进行一致性操作:进行地址监听,并根据监听结果改变Cache的状态。

2.1 PCI总线域和存储器域地址空间

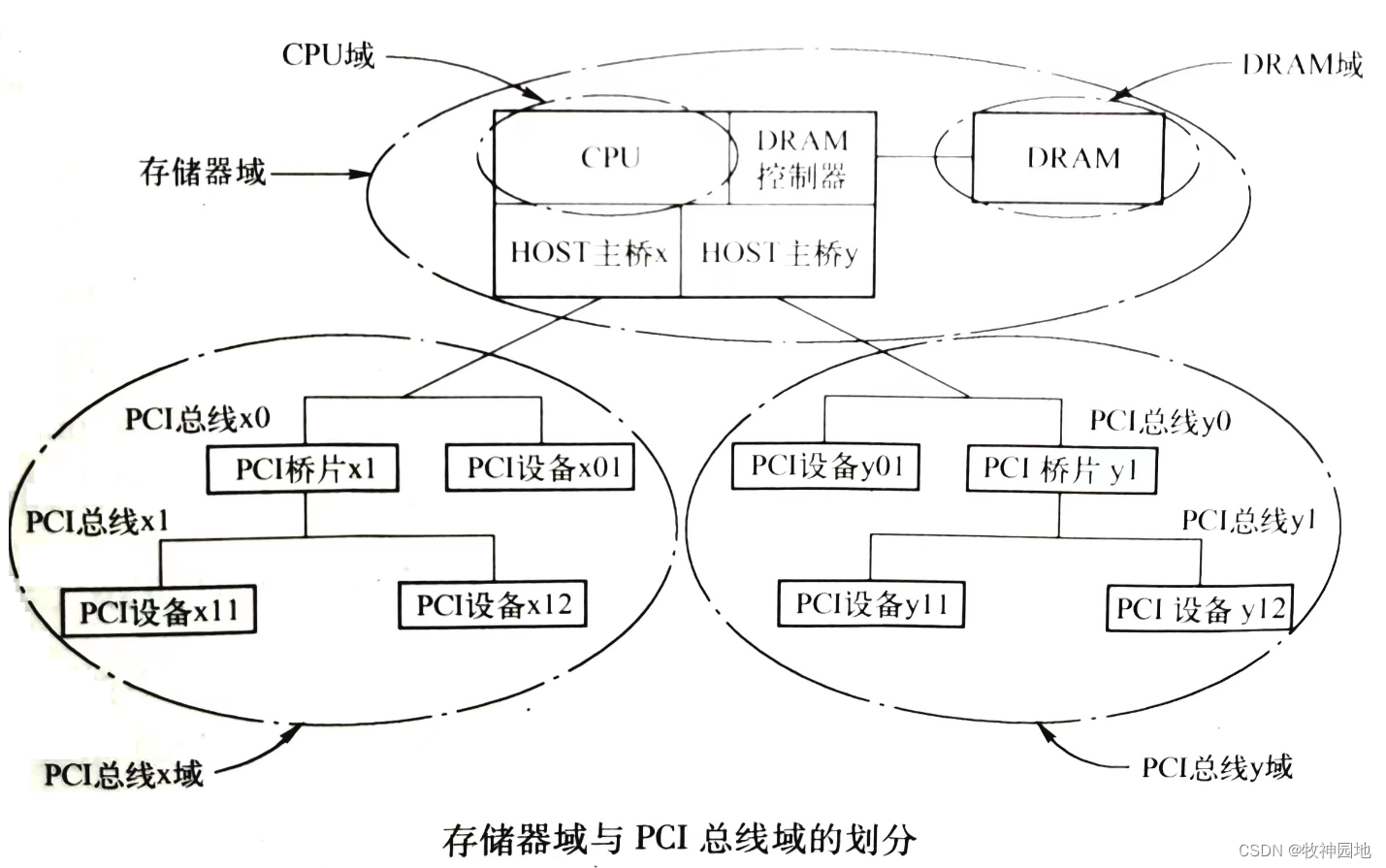

如上所述,HOST主桥的基本功能是分离存储器域和PCI总线域,实现PCI总线域到存储器域,存储器域到PCI总线域之间的数据传递,并管理PCI设备的配置空间。如下图所示,划分了存储器域和PCI总线域;存储器域中划分为CPU域和DRAM域,而PCI域由HOST主桥所决定。

1. PCI总线域:是外部设备与的重要组成部分,由PCI设备所能直接访问的地址空间组成;在一个处理器系统中,可能存在多个HOST主桥,因此存在多个PCI总线域(如上图PCI总线x域和y域),两个PCI总线域的PCI设备不能直接进行数据交换,需通过FSB(Front Side Bus)总线进行数据交换(需要CPU参与);

——在x86处理器系统中,所有外设都使用PCI总线管理,所以PCI总线域与外设空间等效。

——举个栗子:一个HOST主桥对应一个PCI总线域,两个HOST主桥对应两个PCI总线域,不同的HOST主桥对应的PCI总线域是不同的。

——如果HOST主桥支持Peer-to-Peer传输机制(PCI V3.0版本规范支持,不需要CPU参与),那么两个HOST主桥之间可以直接通信。

2. CPU域地址空间:指的是CPU所能直接访问的地址空间集合;CPU域的边界是CPU所能控制的数据完整性边界,仅在CPU内核(Cache)中有效;CPU如果要访问主存储器/PCI设备:

1,首先将读写命令放入读写指令缓存中,然后将命令发送到DRAM控制器/HOST主桥;

2,DRAM控制器/HOST主桥将CPU地址转换为DRAM或PCI总线地址,分别进入DARM域或PCI总线域;

3,访问到DRAM域/PCI总线域的相应地址空间。

3. DRAM域地址空间:DRAM控制器所能访问的地址空间集合,在多数处理器系统中,DRAM域空间是CPU域空间的一部分;

——但有DRAM域空间不属于CPU域空间的情况,例如显卡控制器可能会借用一部分CPU的存储空间,这些被借用的空间不能被CPU所访问。

4. 存储器域:是CPU域和DARAM域的统称;存储器域内包括了CPU内部的通用寄存器,存储器映像寻址的寄存器、主存储器空间和外部设备空间;

——存储器域的外部设备空间,在PCI总线域中还有一个地址映射,当处理器访问PCI设备时首先访问的是该设备在存储器域上的PCI设备空间,然后HOST主桥将该存储器域的PCI总线地址转换为PCI总线域的物理地址。

5. 处理器域地址空间:指处理器系统能够访问的地址空间集合,由存储器域和外部设备域组成;存储器域与PCI总线域两者相互独立,并通过HOST主桥进行数据交换;HOST主桥是连接存储器域和PCI总线域的桥梁,是PCI总线域的实际管理者。HOST主桥进行不同地址域之间的数据交换时,需要遵循如下规则:

——对于x86来说,外部设备域即为PCI总线域;对于其它处理器来说,很多外设直接挂在FSB总线上而不是挂在PCI总线下。

——非常重要的一点:在处理器系统中,HOST主桥管理着PCI总线域,而不是HOST处理器;如果一个处理器系统中有多个CPU,那么每个CPU都可以成为HOST主桥所管理PCI总树的HOST处理器。

1,处理器访问PCI总线域地址空间时:首先需要访问存储器域的地址空间,再通过HOST主桥将存储器地址转换成PCI总线地址,之后才能进入PCI总线域进行数据交换;

2,PCI设备访问存储器时:首先需要访问PCI总线域的地址空间,再通过HOST主桥将PCI总线地址转换为存储器地址,才能进行数据交换;

——此时处理器需要通过HOST主桥将PCI总线地址反向映射为存储器地址,否则不能访问存储器域地址。

4,如果HOST主桥不支持Peer-to-Peer传输方式,那么不同PCI总线域的PCI设备之间不能直接进行数据交换,而需要通过FSB总线实现。

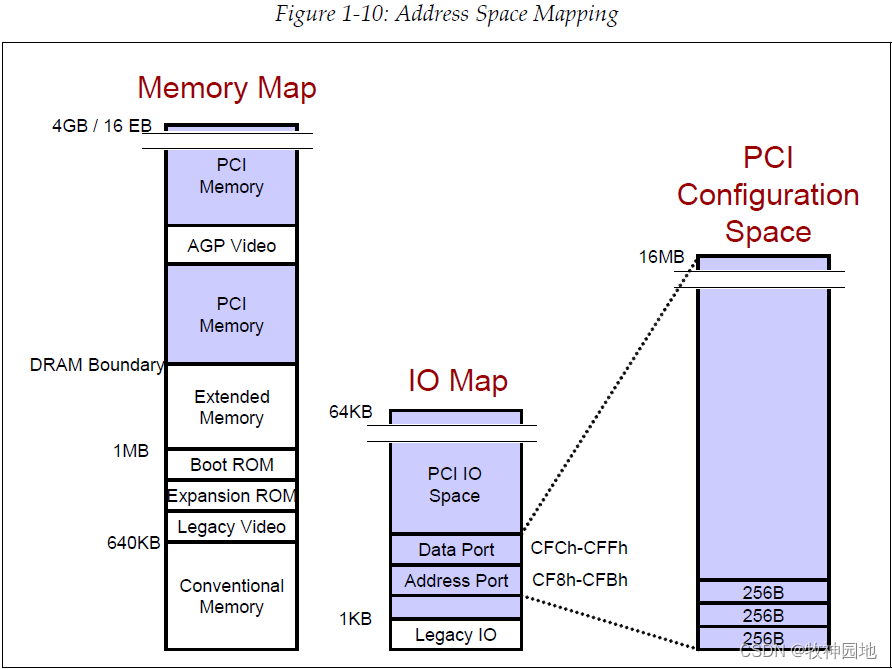

2.2 PCI总线地址空间

PCI体系结构支持3种地址空间,如图下图所示:Memory(内存)、I/O、Configuration Address Space(配置地址空间)。x86处理器可以直接访问Memory和I/O空间:如上所述PCI设备映射到处理器内存地址空间,可以支持32位(4GB)或64位寻址;在I/O地址空间,PCI设备可以支持32位寻址,但是因为x86 CPU仅使用16位的I/O地址空间,所以I/O空间限制在了64KB。

PCI还引进了第三种地址空间,称为配置空间(Configuration Address Space),CPU只能对它进行间接访问而非直接访问(软件不能通过命令直接访问到配置空间寄存器)。PCI设备中的每个Function(功能)都包含专为配置空间所准备的内部寄存器,这些寄存器对于软件来说是可见的,并且软件可以通过一个标准化的方式来控制它们的地址与资源,这为PC提供了一个真正的即插即用(plug and play)的环境。每个PCI Function最多可以有256 Bytes的配置地址空间,PCI总线系统的配置空间总大小为16MB。

——PCI最多可支持单个设备含有8个Function、每路总线含有32个设备、单个系统包含256路总线,那么可以得到一个系统的配置空间总量为:256B/Function *8Function/device * 32devices/bus *256buses/system =16MB。

因为x86 CPU无法直接访问配置空间,所以它必须通过IO寄存器进行索引(然而在PCI Express中引入了一种新方法来访问配置空间,这种新方法是通过将配置空间映射入内存地址空间来完成的)。在传统模型中,如上图所示,使用了一种被称为配置地址端口(Configuration Address Port)的IO端口,它位于地址CF8h-CFBh;还使用了一种被称为配置数据端口(Configuration Data Port)的IO端口,它位于地址CFCh-CFFh。

2.3 PCI总线组成

我们再次回到PCI总线的结构,如上所述PCI总线相关的模块包括了:HOST主桥,PCI总线,PCI桥和PCI设备;

1. 我们已经知道了,HOST主桥的功能是隔离处理器系统的存储器域和PCI总线域,并管理PCI总线域,完成处理器与PCI设备之间的数据交换;而处理器与PCI设备之间的数据交换主要由:1,处理器访问PCI设备的地址空间;2,PCI设备使用DMA机制访问主存储器;这两部分组成;

——HOST主桥下的PCI设备的配置空间都由HOST主桥通过配置读写(Config Read/Write)访问。

2. PCI总线,有PCI总线和PCI总线树两个概念;一颗PCI总线树中可能有多条PCI总线,而具有血缘关系的PCI总线组成一颗PCI总线树,一般直接与HOST主桥连接的PCI总线被命名为总线0;

——PCI总线由HOST主桥或PCI桥来管理,用来连接各类PCI设备;如果有多个HOST主桥那么就有多个PCI总线树。

3. PCI设备,PCI总线中有三类设备:PCI主设备,PCI从设备和桥设备;

1,PCI从设备只能被动接收来自HOST主桥或其它PCI设备的读写请求;

2,PCI主设备可以通过总线仲裁获得PCI使用权,主动向其它PCI设备/主存储器发起读写请求;

3,桥设备的主要作用是管理下游PCI总线,并转发上下游总线之间的事务;

——PCI桥的两端分别接了两条PCI总线:上游总线和下游总线;其中距离HOST主桥较近的总线称为上游总线(Primary Bus),相反较远的那条称为下游总线(Secondary Bus);但是不可否认的是它们都属于同一个总线域。

——存在两种PCI桥:透明桥和非透明桥。

——PCI桥的存在是PCI总线具有强大扩展性的重要原因,使大规模系统互连成为可能。

4,HOST主桥是一个特殊的PCI设备,可以获取PCI总线的控制权和访问PCI设备,也可以被PCI设备所访问,但是HOST主桥并非PCI设备,在PCI规范中没有对HOST主桥进行定义;

4. HOST处理器,PCI总线规范规定在同一时刻,在一颗PCI总线树上有且只有一个HOST处理器;该HOST处理器可以通过HOST主桥发起PCI总线的配置请求总线事务,并对PCI总线上的设备和桥片进行配置。

——对于多CPU的处理器,这些CPU都可以通过HOST主桥访问其下的PCI总线树,作为HOST处理器;但上面已经说了:PCI总线树的实际管理者是HOST主桥,而非HOST处理器。

2.4 PCI总线的优点

PCI总线相比于EISA和MCA总线相比有很多突出的优点:

1. PCI总线空间与处理器空间隔离,即PCI设备具有独立的地址空间,如上图所示该空间通过HOST主桥隔离,而且HOST主桥包含有缓存,使得处理器和PCI总线工作在各自时钟频率中,互不干扰;

——任何访问PCI设备的操作必须经过HOST主桥, PCI设备可以通过HOST主桥与处理器共享主存储器资源;

——HOST主桥的一个重要作用就是将处理器访问的存储器地址转换为PCI总线地址;而PCI设备的地址属于PCI总线域的,与存储器地址空间不同。

2. PCI总线具有很好的可扩展性,HOST主桥管理的第一条PCI总线,可以通过PCI桥扩展出一系列PCI总线,并以HOST主桥为根节点,形成一颗PCI总线树;

——PCI总线树上最多能挂256个PCI设备,这其中包括了PCI桥;而PCI桥是PCI总线能够扩展的主要原因,每一个PCI桥下相当于一个PCI总线的子树,可以通过PCI桥继续扩展;

——PCI桥可以管理这颗PCI总线子树,其配置空间中含有管理PCI总线子树的配置寄存器。

3. PCI设备地址可以根据需要由软件动态分配,解决了设备间的地址冲突问题,实现了PCI板卡即插即用的功能;

——PCI设备的地址在BAR空间中,系统软件可以动态配置这个基地址(也可以配置固定地址),保证了每个PCI设备使用的物理地址不相同;PCI桥的配置空间含有其下挂PCI子树所能使用的地址范围。

4. 总线带宽高,32位/33MHz的PCI总线可提供132MB/s的峰值带宽,相比于EISA和MCA要大的多;

5. 共享总线机制,PCI设备通过仲裁后获得总线使用权,然后才能进行数据传输,PCI总线上的数据传输不需要处理器干预;

——PCI总线仲裁器不在PCI总线规范定义中,并不一定是HOST主桥和PCI桥的一部分(一般来说是由它们来实现)。

6. 中断机制,PCI总线上的设备可以通过4个中断信号INTA~D#向处理器提交中断请求;PCI总线上的设备可以共享中断请求信号,不同的PCI设备可以“线与”后连接到中断请求管脚上。

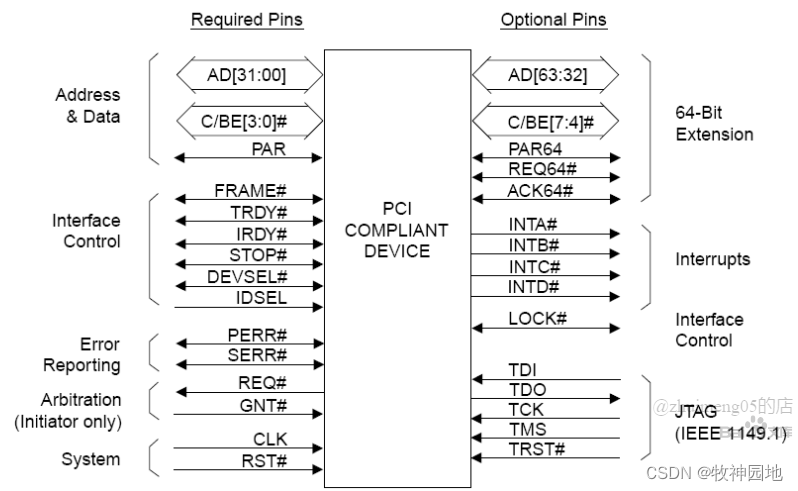

3,PCI总线信号

PCI总线是一条共享总线,一条PCI总线上可以挂接多个PCI设备;这些PCI设备通过信号线与PCI总线相连:地址/数据信号,控制信号,仲裁信号,中断信号等等。同时PCI总线也是一个同步总线,每个设备都有一个CLK信号,发送设备和接收设备使用CLK信号进行数据同步传输;PCI总线使用33MHz和66MHz时钟频率,而PCI-X总线可以使用133MHz、266MHz或533MHz的时钟频率。PCI总线信号如下表所示。

1. AD[31:0]信号:PCI总线复用地址/数据信号,PCI总线事务启动后的第一时钟周期传输地址(PCI总线域的Memory地址或I/O地址),第二个时钟周期传输数据;

——传输地址的时钟周期称为地址周期,传输数据的时钟周期称为数据周期。

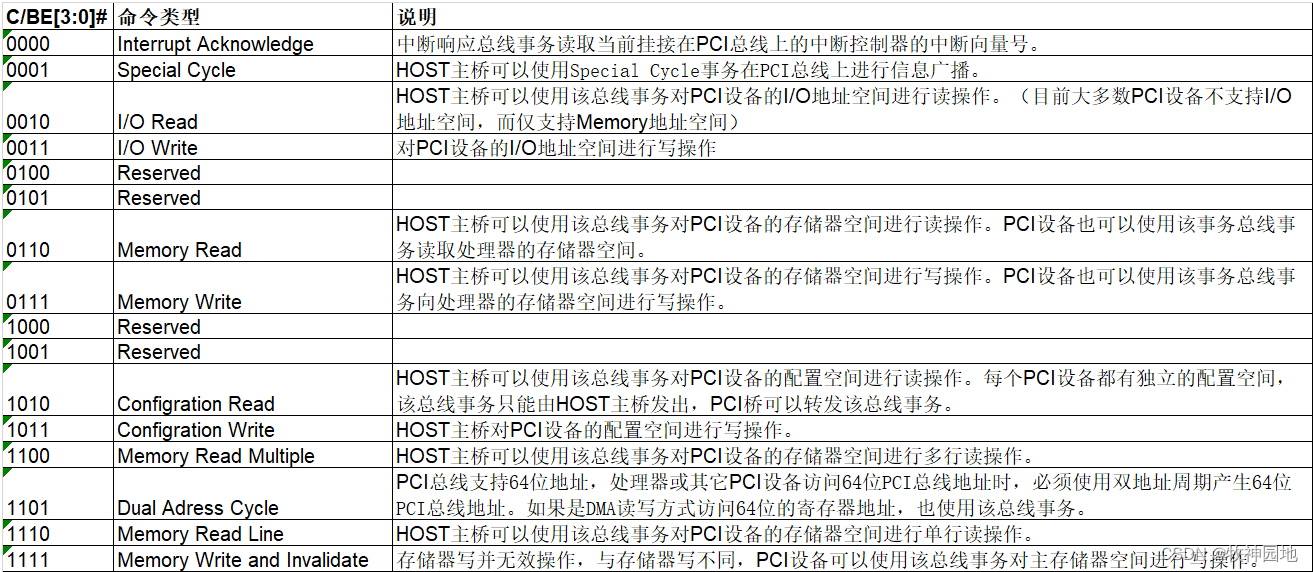

2. C/BE[3:0]#:总线命令和字节多路复用选通信号;

1,在地址周期:C/BE[3:0]#信号表示PCI总线的命令;

2,在数据周期:C/BE[3:0]#输出字节选通信号,CBE3#~0#分别对应数据字节3/2/1/0;使用这组信号可以进行单字节、字和双字访问。

3. PAR:奇偶校验信号;PCI总线使用奇偶校验机制,保证地址和数据信号在进行数据传输的正确性;PAR信号时AD[31:0]和C/BE[3:0]#的奇偶校验信号;

——PCI主设备在地址周期和数据周期中,使用该信号为地址和数据信号提供奇偶校验位。

4. FRAME#:帧周期信号,指示PCI总线事务的开始与结束;当PCI设备获得总线的使用权后,置该信号有效(低电平),启动PCI总线事务,当结束总线事务时,将置该信号无效(高电平);

——PCI设备只有通过仲裁获得当前PCI总线的使用权后,才能驱动该信号。

5. IRDY#:主设备准备好信号,该信号有主设备驱动,该信号有效表示PCI主设备的数据已经准备完成;

——如果PCI总线事务为写事务,则表示数据在AD[31:0]上有效;如果为读事务,则表示PCI主设备已经准备好接收,目标设备可以将数据发送到AD[31:0]上。

6. TRDY#:目标设备准备好信号,该信号由目标设备驱动,该信号有效则表示目标设备已经将数据准备完毕;

——如果PCI总线事务为写事务,则表示目标设备以准备好接收,可以将AD[31:0]上的数据写入目标设备;如果为读事务,则表示PCI设备需要的数据已经在AD[31:0]上有效。

7. STOP#:停止数据传输信号,表示目标设备请求主设备停止当前PCI总线事务;

8. LOCK#:锁定信号,将目标设备的某个存储器或I/O资源锁定,以禁止其它PCI主设备访问此资源,直到锁定这个资源的主设备将其释放;

9. IDSEL:设备选择信号,PCI总线在进行配置读写总线事务时,使用该信号选择PCI目标设备;配置读写总线事务与存储器读写事务在实现上有所不同;配置读写总线事务使用“ID译码方式”访问PCI设备,即通过PCI设备的总线号、设备号和寄存器号访问PCI设备的配置空间;

——IDSEL信号与PCI设备的设备号相关,相当于PCI设备配置空间的片选信号。

10. DEVICE#:该信号有效时表示PCI总线的目标设备准备好,其与TRDY#信号不同在于DEVICE#有效仅表示目标设备已经完成了地址译码,用于通知PCI主设备其访问对象在当前PCI总线上,但并不表示目标设备可以与主设备进行数据交换;

11. REQ#/GNT#:总线占用请求/允许信号,这组信号用于进行总线仲裁,并获得PCI总线的使用权,只有PCI主设备需要用到该组信号,而PCI从设备不需要;

——一条PCI总线能够挂接PCI主设备的数量,除了与总线负载能力相关之外,还与PCI总线仲裁器能够提供的仲裁信号直接相关。

11. INTA/B/C/D#:中断请求信号,PCI设备使用这些中断请求信号向处理器发送中断请求:当中断请求信号为低时,PCI设备想处理器提交中断请求;当处理器执行中断服务程序清楚PCI设备的中断请求后,PCI设备将该信号置高,结束中断请求;

——单功能(Function)PCI设备只能使用INTA#,而多功能(Function)设备才能使用INTB#/C#/D#。

12. PERR#:数据传输过程中出现奇偶校验错误;

13. SERR#:系统错误报告信号。

1,地址奇偶校验错误;

2,在Special Cycle周期中出现数据奇偶校验错误;

3,系统出现其它严重错误。

PCI总线的管理采用单独管脚信号(带外)来实现,但到了PCIe总线中这些管理功能是前向兼容PCI总线的,这些信号的功能被转移到了带内来实现。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?