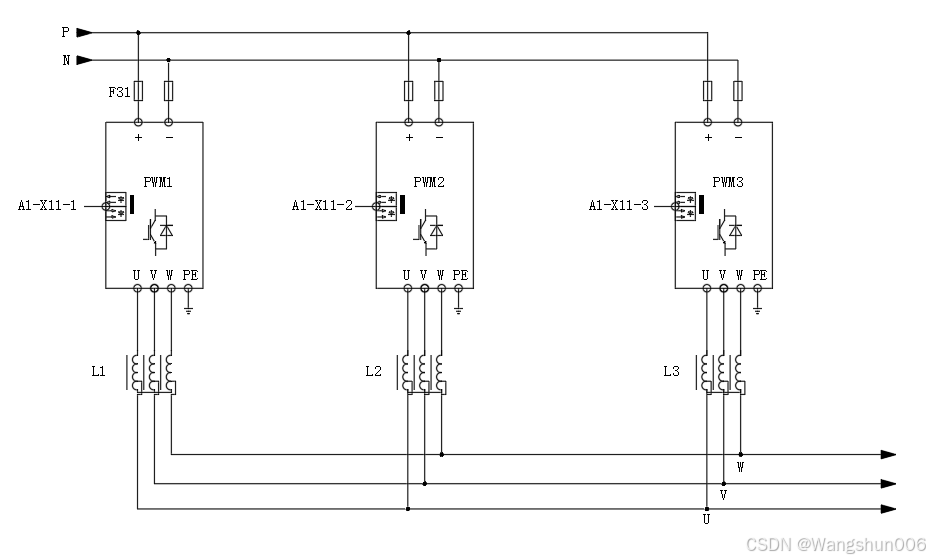

现在大功率国产变频器(大传动)应用越来越多,一般是串联升压的高压变频器,另一种就是低压并联单元使用。本文讲低压大功率,多单元并联使用时,驱动信号存在一定的延时,到达不同单元IGBT驱动开通关断时间存在偏差,从而产生环流。一般都配均流电抗器。但是为了增大使用功率,并联使用是目前使用较多的方式。并联为了每个单元输出电流都在每个单元的IGBT承受能力之内,一般都配均流电抗器,也有的小厂家不加均流电抗器直接并联,非常有风险的。

现在很多稍微大点的功率变频器是在单元内部一块驱动板直接并联多个IGBT来实现增大功率,通过双脉冲测IGBT驱动参数观察并联均流情况,Re和开通关断等综合考虑。但是一块驱动板上并联的多,对驱动电源、驱动光耦要求变大,结构、散热等方面都做不好,所以一般就并联2-3个,而且还要在原来降额使用的基础上还要降额使用。综上所述,超大功率的方案首选是多单元+均流电抗器并联拓扑。

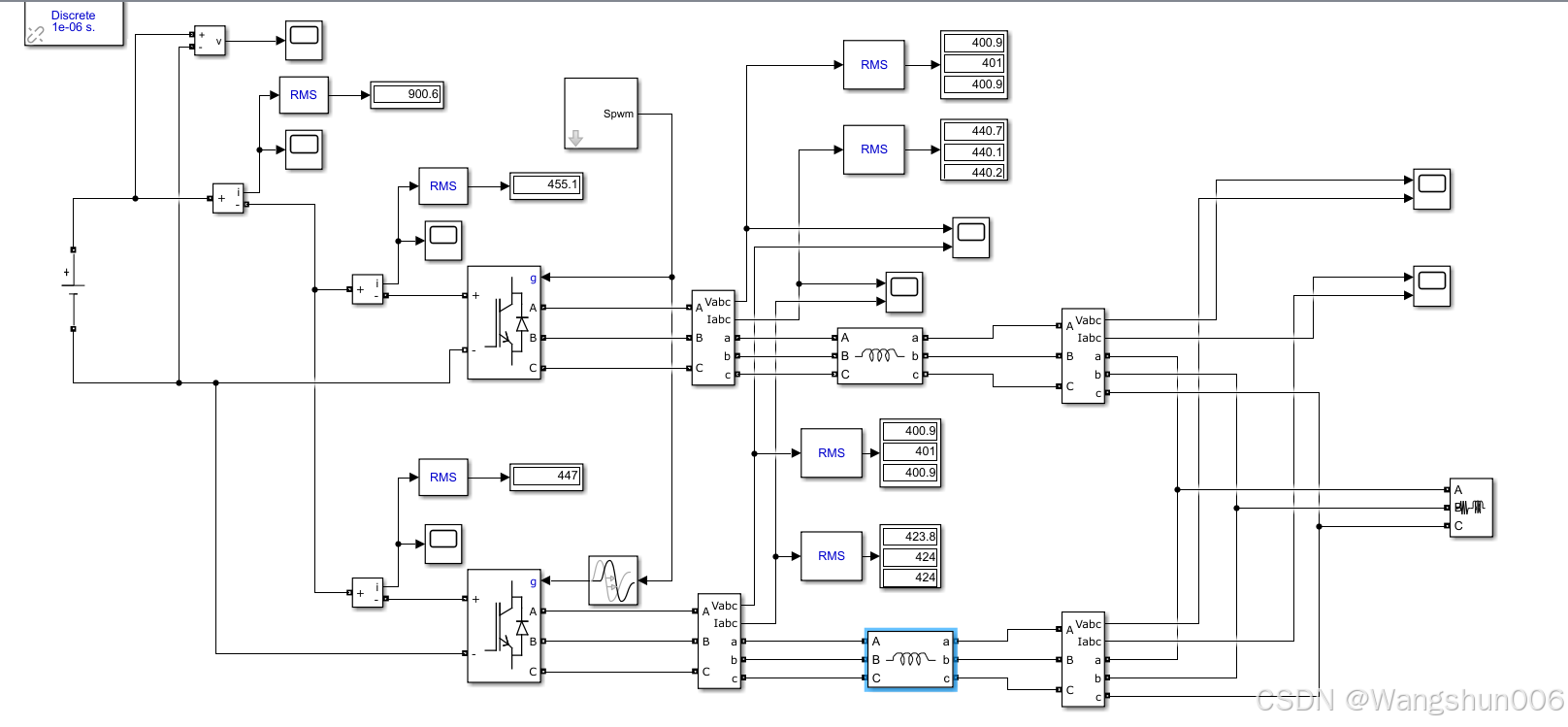

并联电抗器感值要和延时、死区时间都有关系。首先要确认延时,从MCU到IGBT开通的延时。一般这种大功率都是算力较高的芯片,或者ARM+FPGA的主控芯片,FPGA的处理能力快。很多厂家的多并联单元结构都是主控通过光纤控制各个单元,光纤的通讯速率和抗干扰能力强。从控制盒到IGBT驱动这条电路上的延时需要计算出来。电路板原理图里存在的各类RC延时、通讯口、驱动光耦、IGBT开通延时。各家产品各异,我假设一个1uS的延时。

仿真模型如下:

根据公式计算感值在10uH满足2%不均流度,仿真时,电感感值和两侧电流均值有直接关系。增大感值能直接看出均流变好。算下440和424A的不均流度为2%。符合设计要求。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?