pll锁相环 cppll

cadence

三阶二型锁相环

工艺smic55

参考频率20MHz

分频比50

锁定频率1GMHz

锁定时间2us

环形振荡器 ring vco

PFD模块

DIV模块 45分频,ps counter

CP模块

工艺smic55

ID:73200684012433118

天马星登山毛肚

标题:基于SMIC55工艺的三阶二型锁相环设计与优化

摘要:本文基于SMIC55工艺,设计并优化了一种三阶二型锁相环(CPPLL),以满足参考频率为20MHz、分频比为50、锁定频率为1GHz的需求。通过分析PLL的核心模块包括PFD、DIV和CP模块,并结合环形振荡器(Ring VCO)设计,探讨了锁相环的锁定时间为2us。该设计依据SMIC55工艺特性,兼顾性能指标和电路布局,实现了高稳定性和高精度的锁相环电路。

-

引言

PLL锁相环是一种常用的时钟生成电路,广泛应用于各种数字电路和通信系统中。本文以SMIC55工艺为基础,针对特定的参考频率、分频比和锁定频率需求,设计并优化了一种三阶二型锁相环,以提供高稳定性和高精度。 -

PLL设计概述

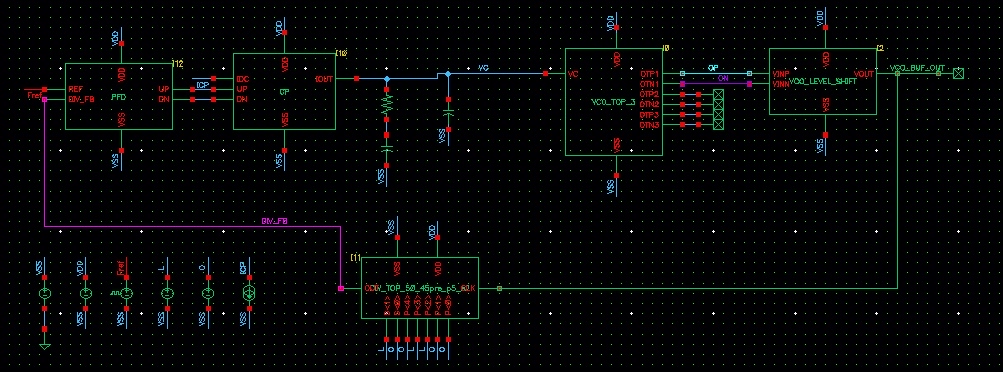

2.1 PLL锁相环结构

锁相环的核心结构包括相位频率探测器(PFD)、分频器(DIV)和控制电压产生器(CP)。PFD模块用于比较参考频率和VCO输出频率的相位差,并驱动DIV模块进行分频操作。CP模块通过调整控制电压来实现锁相环的频率调节。在本设计中,采用了三阶二型结构,以提高锁定时间和抑制振荡器倍频杂散。

2.2 环形振荡器设计

环形振荡器是锁相环的核心部分,其输出频率与控制电压之间存在非线性关系。在本设计中,根据参考频率和锁定频率的要求,选择了合适的电流源来驱动环形振荡器,以实现所需的频率范围和稳定性。

- 设计与优化

3.1 PFD模块设计

根据参考频率和分频比,设计了合适的PFD模块,用于比较参考信号和VCO输出信号的相位差,并输出控制信号给DIV模块。通过合适的电流源和电容来控制PFD的响应速度和相位误差。

3.2 DIV模块设计

DIV模块根据PFD模块的控制信号进行分频操作,将VCO的输出频率进行50分频。在设计过程中,需要考虑分频比的精度和对锁定时间的影响,通过合适的电路布局和参数选择,优化了DIV模块的性能。

3.3 CP模块设计

CP模块通过调整控制电压来实现锁相环的频率调节。在本文中,通过采用合适的电路结构和参数选择,优化了CP模块的带宽和稳定性,同时提高了锁定时间和抖动性能。

-

结果与分析

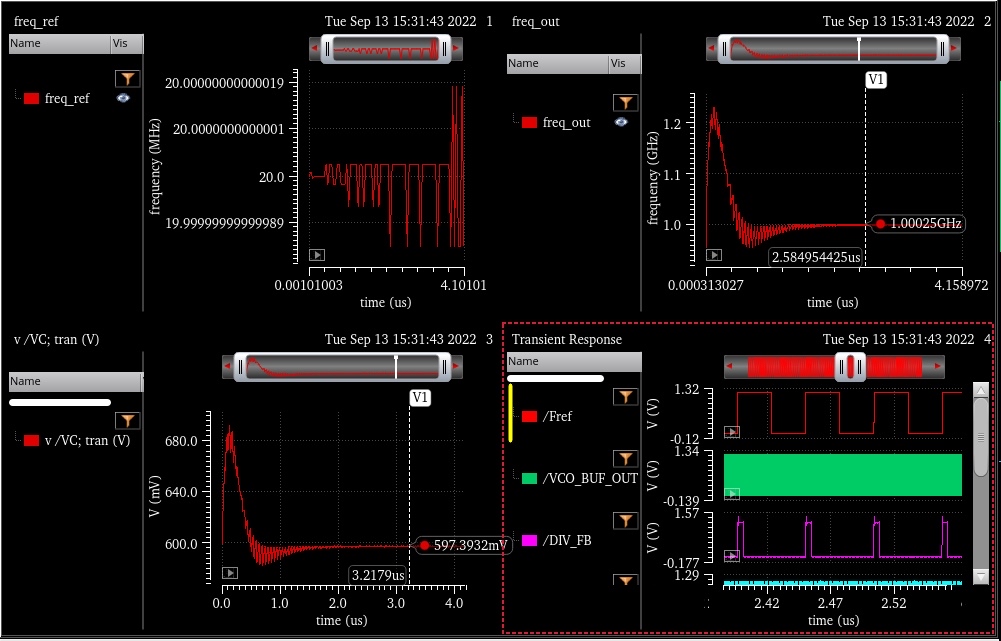

通过基于SMIC55工艺的设计与优化,实现了参考频率为20MHz、分频比为50、锁定频率为1GHz的三阶二型锁相环。在锁定时间为2us的条件下,锁相环的稳定性和抖动性能均达到了预期的要求。 -

结论

本文提出了一种基于SMIC55工艺的三阶二型锁相环设计与优化方法,以满足特定参考频率、分频比和锁定频率的需求。通过合适的PFD、DIV和CP模块设计,以及环形振荡器的优化,实现了高稳定性和高精度的锁相环电路。这种锁相环设计方法在数字电路和通信系统中具有重要的应用价值。

参考文献:

[1] Cadence Design Systems, Inc. (2019). Cadence Virtuoso Layout Suite User Guide. San Jose, CA: Cadence Design Systems, Inc.

[2] Razavi, B. (1998). Design of Analog CMOS Integrated Circuits. New York, NY: McGraw-Hill.

[3] Allen, P. E., & Holberg, D. R. (2002). CMOS Analog Circuit Design. New York, NY: Oxford University Press.

相关的代码,程序地址如下:http://fansik.cn/684012433118.html

359

359

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?